数字电路基础与Quartus-Ⅱ入门

任务要求

1.复习数字电路基础知识;安装Quartus-II软件,进行数字电路的仿真与验证。

安装Quartus-II 13 和Modelsim。

安装参考:

https://blog.youkuaiyun.com/qq_43279579/article/details/115158140

https://blog.youkuaiyun.com/qq_43279579/article/details/115176423

视频教学:

https://www.bilibili.com/video/BV194411f7GD?p=5

2.在 Quartus-II 中自己用门电路设计一个D触发器,并进行仿真,时序波形验证;

3.在 Quartus-II 中直接调用一个D触发器电路,进行仿真,时序波形验证,与2做比较;

4.(选做)在 Quartus-II用Verilog语言写一个D触发器,进行仿真验证,与3做比较;

安装Quartus-II软件

安装参考在任务要求里面有,可查看。

百度网盘下载地址:

https://pan.baidu.com/s/1a9d-bq9RZmWrRV542X4IEA

提取码:ifte

数字电路的仿真与验证

1.创建工程

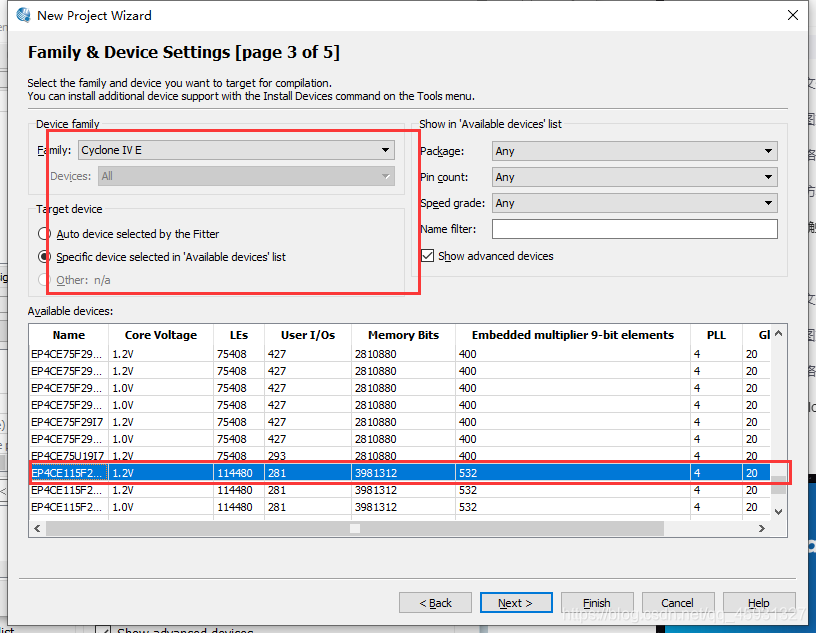

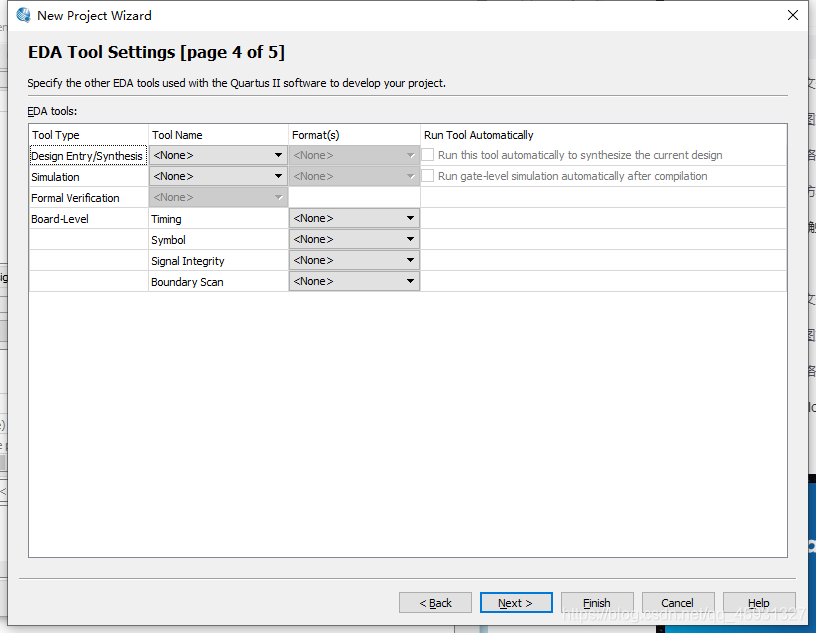

芯片选择与其他

原理图输入这里选择不输入

工程创建完成,点击finish

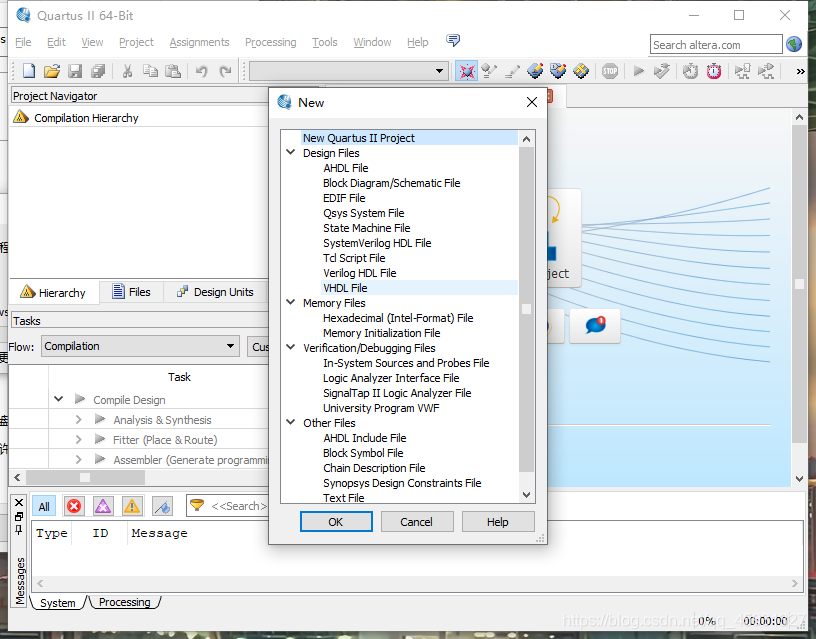

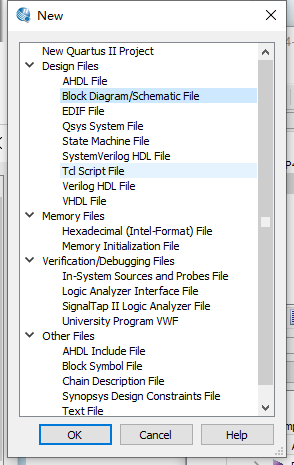

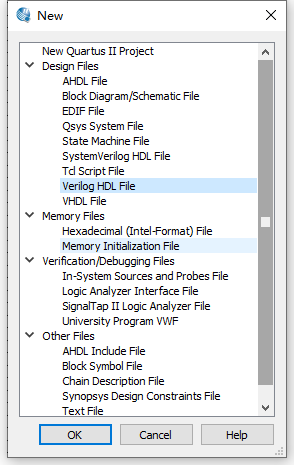

2.创建文档文件file-new

选择Block Diagram/Schematic File

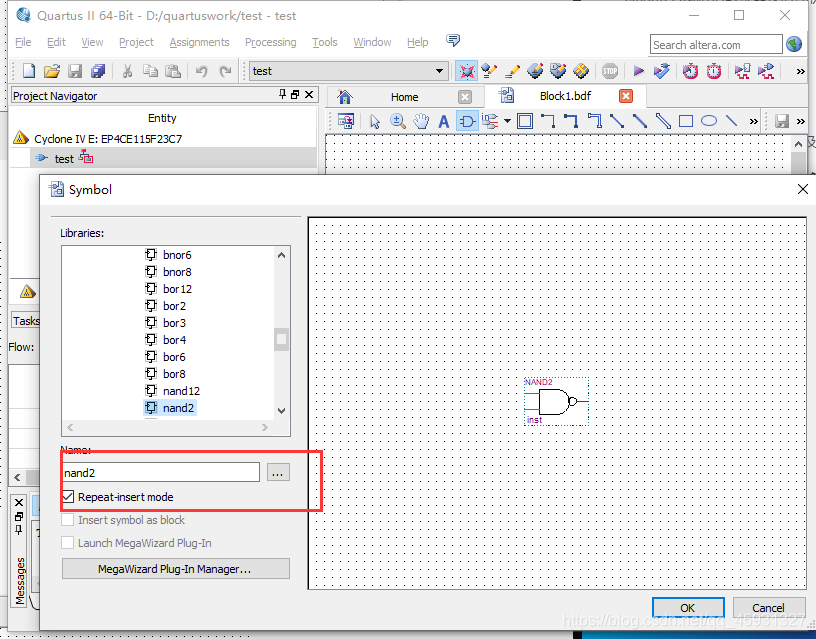

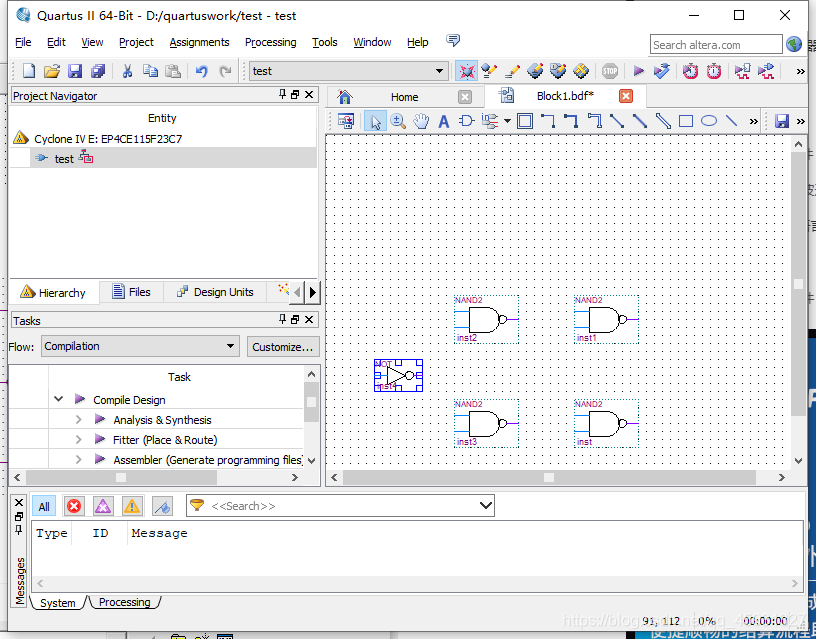

首先点击上面箭头处,然后选择nand2,二个输入的与非门,依次添加四个and2和一个非门not

连线工具选择input

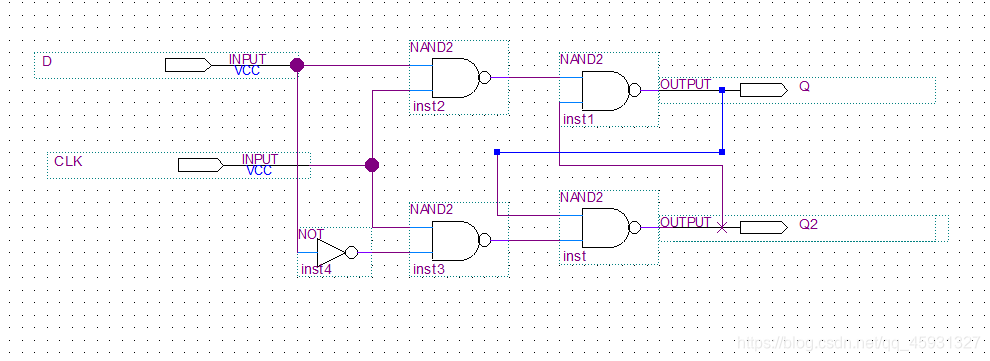

链接的图如下

3.编译原理图文件

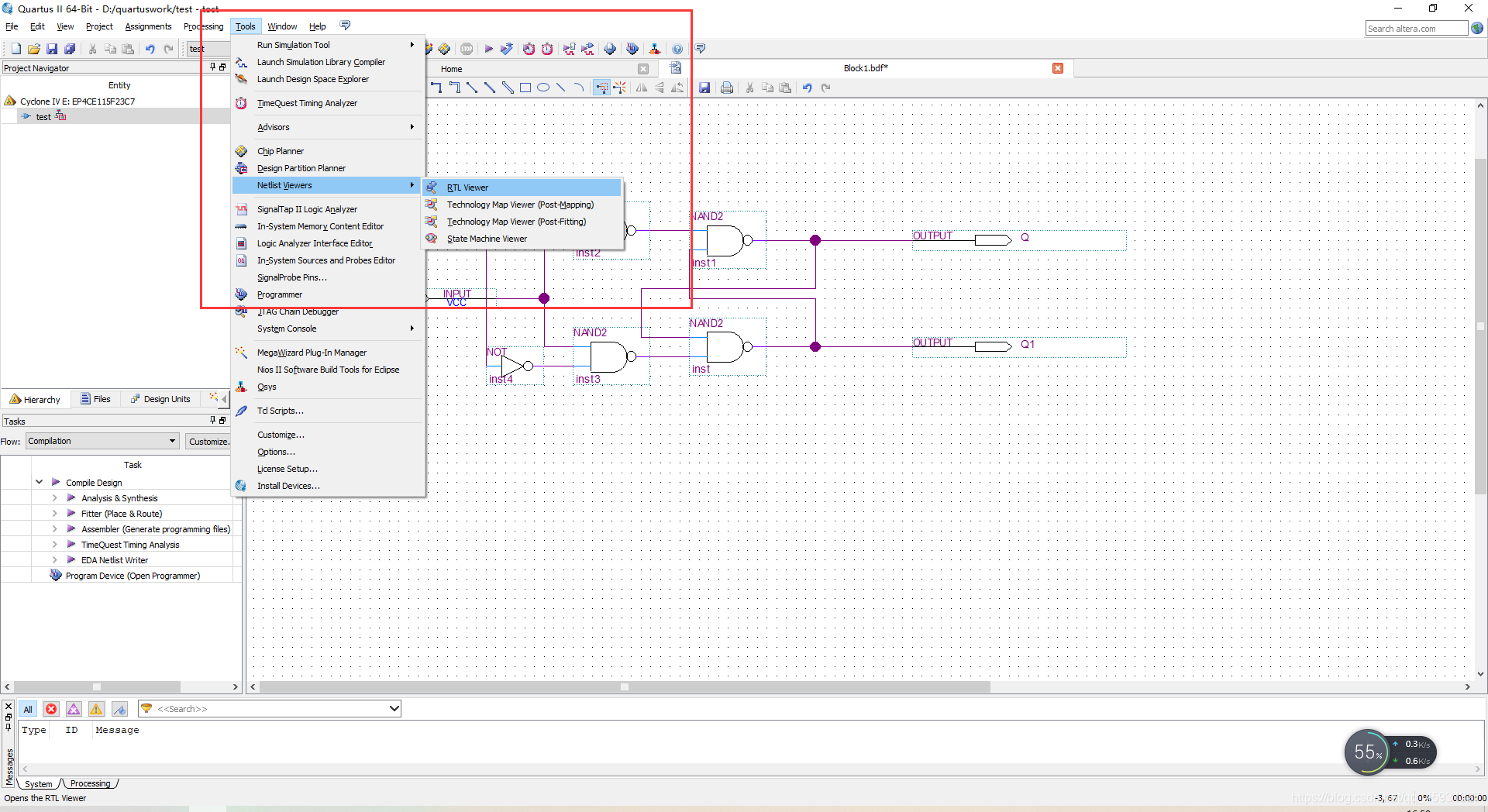

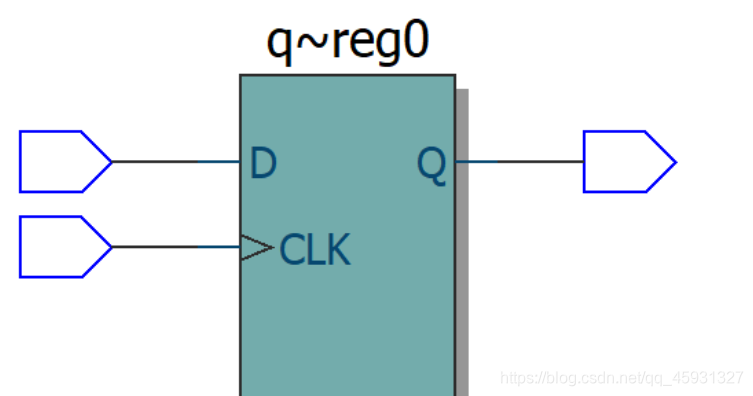

rtl viewer,查看硬件电路图

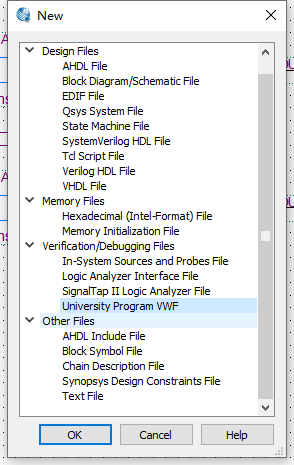

4.创建vwm格式波形文件

选择vwf

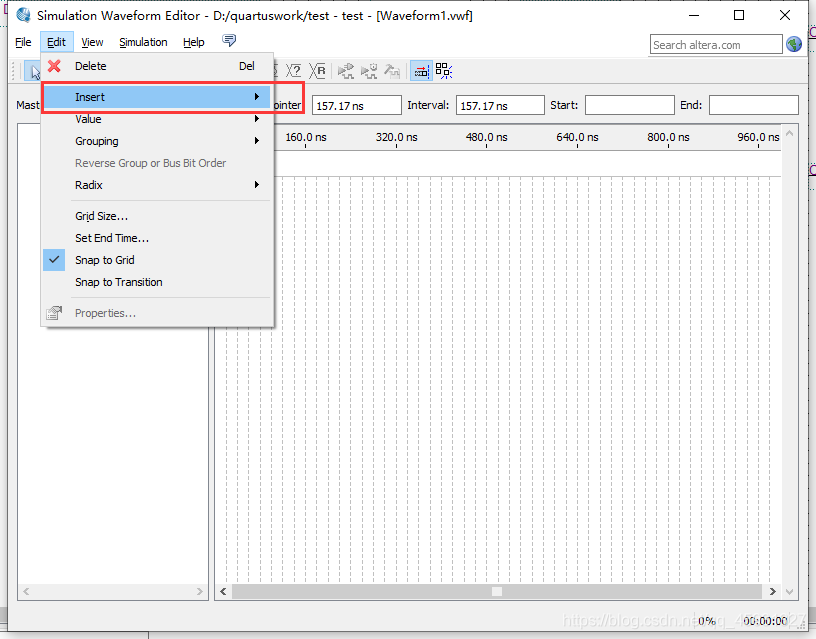

Edit->Insert->Insert Node or Bus

添加Node or Bus

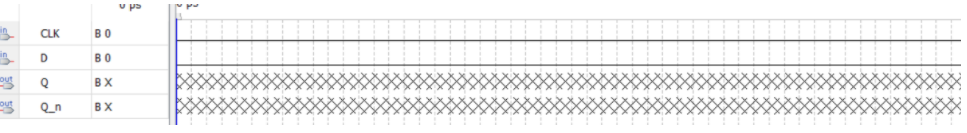

效果如下:

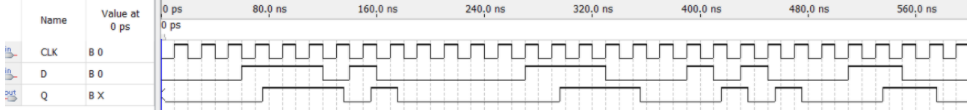

5.时序波形仿真

2.Quartus-II调用D触发器及时序仿真

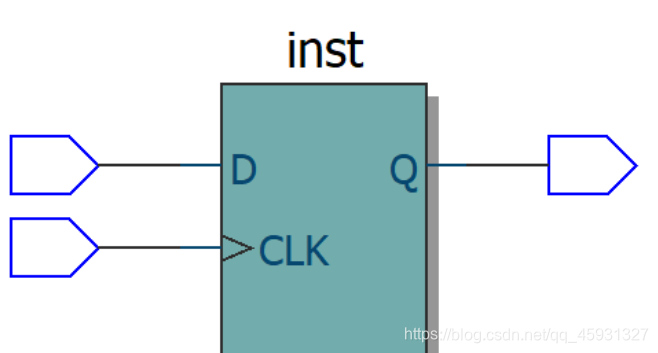

(1)创建方框文件

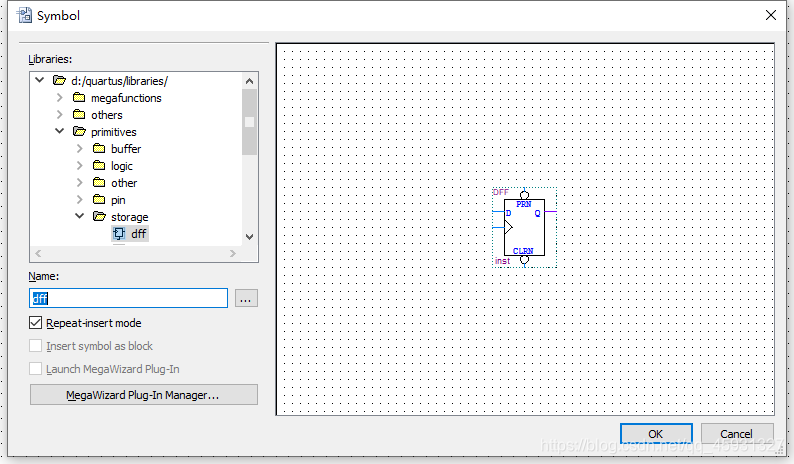

调用D触发器

(2)编译原理图文件

(3)创建vwm格式波形文件及时序仿真

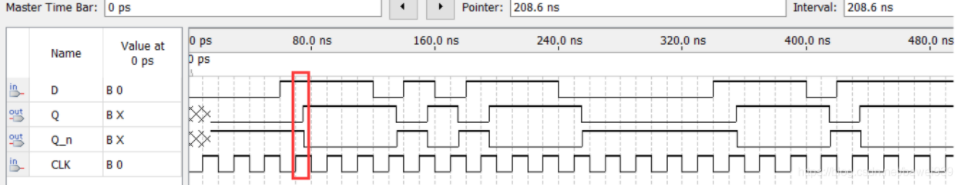

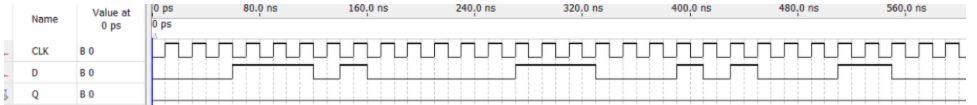

编辑好的波形

功能仿真

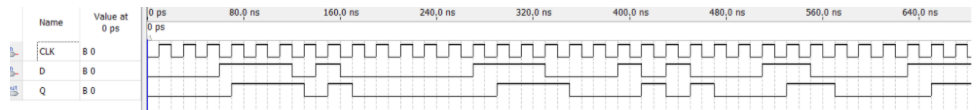

时序仿真

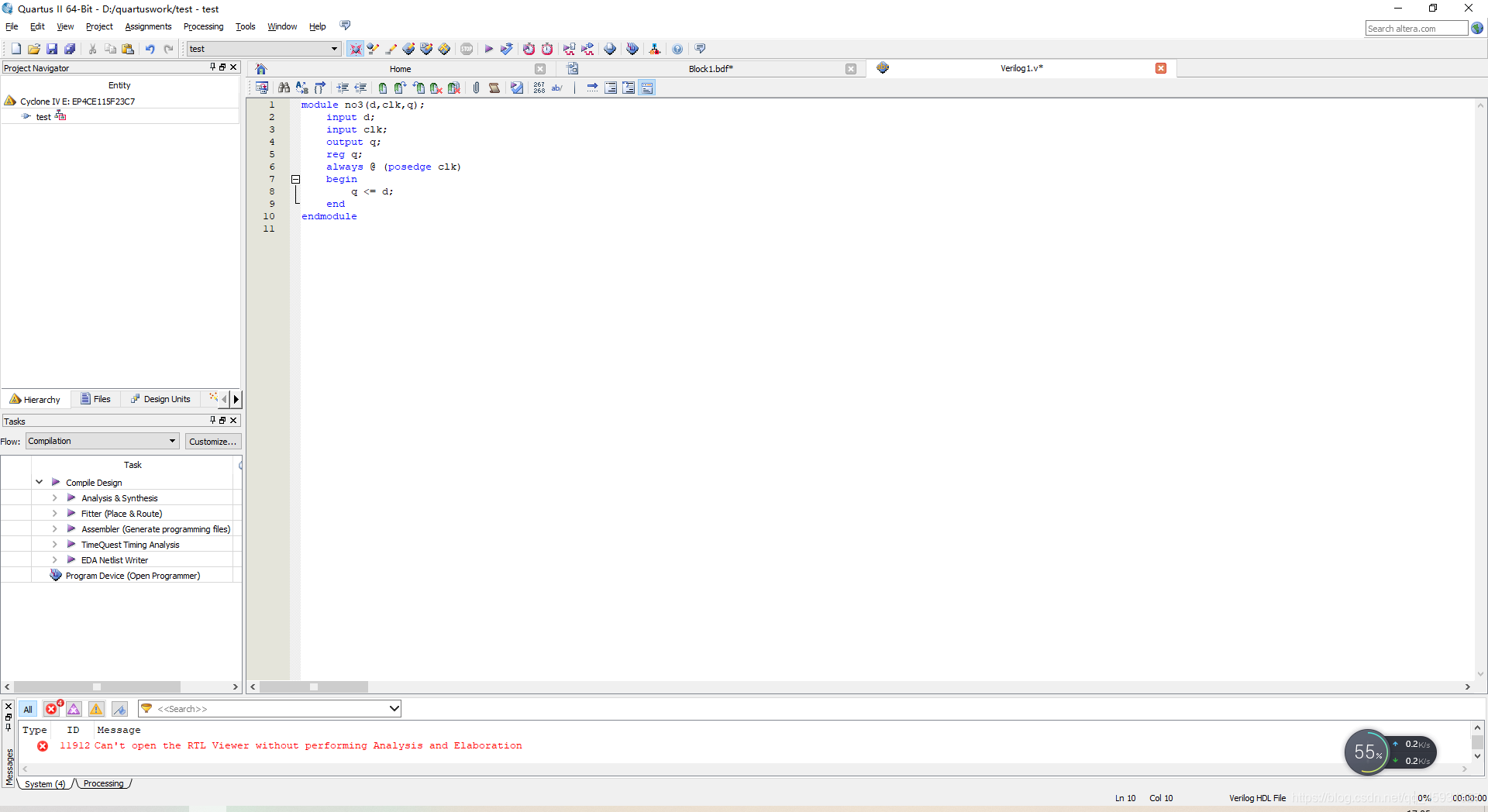

6.Quartus-II用Verilog语言实现D触发器及时序仿真

选择file-new-Verilog HDL File

添加如下代码,保存并编译

module no3 (d, clk,gq);

input d;

input clk;output q;

reg q;

always @ (posedge clk)

begin

q<= d;

endmodule

测试代码:

`timescale 1ns / 1ns

module no3_tb;

reg clk,d;

wire q;

no3 u1(.d(d),.clk(clk),.q(q));

initial

begin

clk = 1;

d <= 0;

forever

begin

#60 d <= 1;

#22 d <= 0;

#2 d <= 1;

#2 d <= 0;

#16 d <= 0;

end

end

always #20 clk <= ~clk;//半周期为20ns,全周期为40ns的一个信号

endmodule

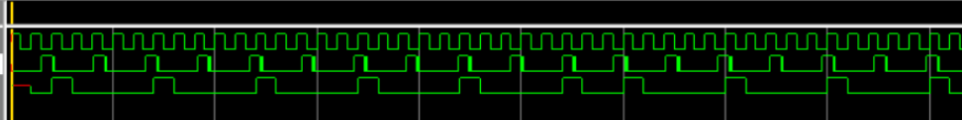

仿真结果:

参考博客:

https://blog.youkuaiyun.com/bawei939/article/details/115349753?spm=1001.2014.3001.5501

https://blog.youkuaiyun.com/qq_43279579/article/details/115158140

1612

1612

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?