目录

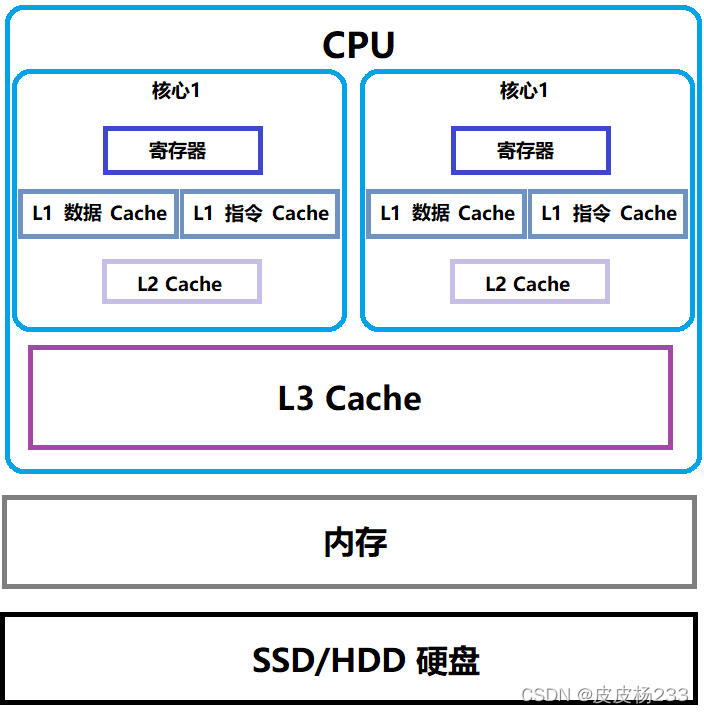

硬件结构

CPU

存储器

层次结构&&关系

离 CPU 越近越快;每个存储器只与相邻一层存储器打交道;速度越快成本越高。

寄存器:

- 通常在几十 ~ 几百个之间

- 每个寄存器一般存储 4Byte(32 位) 或者 8Byte(64 位) 数据

- 一般半个时钟周期(1 / 主频)内读写完成

CPU Cache:使用静态随机存储器(SARM Static Random-Access Memory)

- L1 高速缓存:2 ~ 4 个时钟周期;几十 KB ~ 几百 KB

- L2 高速缓存:10 ~ 20 个时钟周期;几百 KB ~ 几 MB

- L3 高速缓存:20 ~ 60 个时钟周期;几 MB ~ 几十 MB

内存:使用动态随机存储器(DRAM Dynamic Random Access Memory)

- 200 ~ 300 个时钟周期

SSD/HDD 硬盘:

- SSD(固态硬盘):比内存慢 10 ~ 1000 倍

- HDD(机械硬盘):比内存慢 10W 倍

内存映射到 Cache 的方案

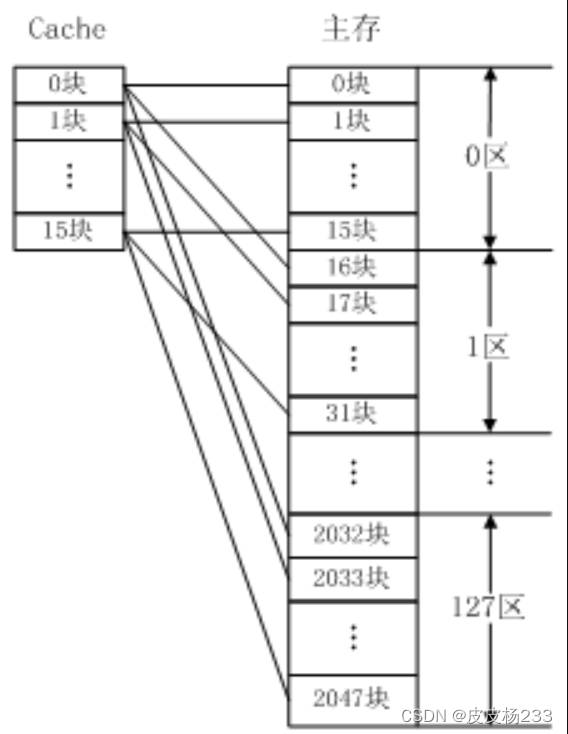

直接映射:

优点:

- 硬件简单,成本低,地址计算速度快

- 不涉及替换算法

缺点:

- 不灵活,每个内存块只有固定位置

- Cache 空间得不到充分利用

- 容易发生冲突,Cache 效率降低

- 只适合大容量 Cache

- 如 0 和 16 都映射到第 0 块,其实其他块空闲也不能占用,这两块会来回替换,降级命中率

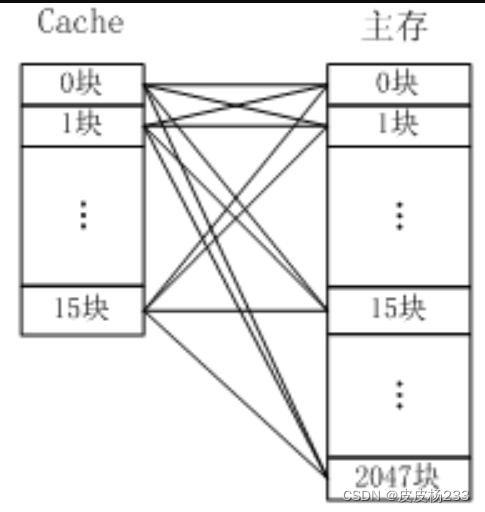

全相联映射:

优点:

- 灵活,可以映射到任意块

- Cache 利用率高

- 冲突率低

缺点:

- Cache 比较电路设计和实现比较困难

- 只适合小容量 Cache

组相联映射: 为前两种的折中方法,组间使用直接映射,组内使用全相联映射

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1074

1074