芯片

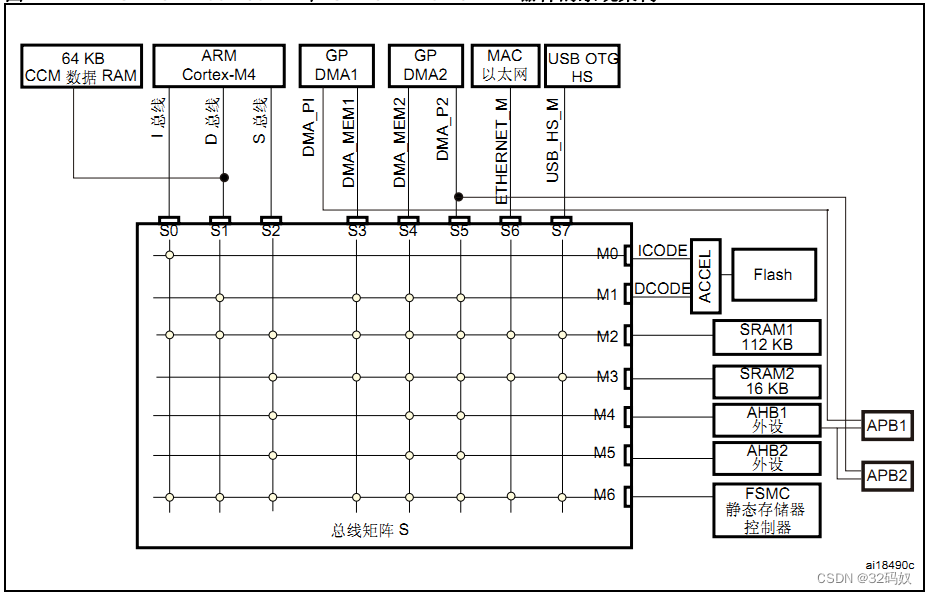

F407总线架构

- 主系统由 32 位多层 AHB 总线矩阵构成。

- 总线矩阵用于主控总线之间的访问仲裁管理。

- 仲裁采取循环调度算法。

- 总线矩阵可实现以下部分互联:

八条主控总线是:

- Cortex-M4 内核 I 总线, D 总线和 S 总线;

- DMA1 存储器总线, DMA2 存储器总线;

- DMA2 外设总线;

- 以太网 DMA 总线;

- USB OTG HS DMA 总线;

七条被控总线:

- 内部 FLASH ICode 总线;

- 内部 FLASH DCode 总线;

- 主要内部 SRAM1(112KB)

- 辅助内部 SRAM2(16KB);

- 辅助内部 SRAM3(64KB) (仅适用 STM32F42xx 和 STM32F43xx 系列器件);

- AHB1 外设 和 AHB2 外设;

- FSMC

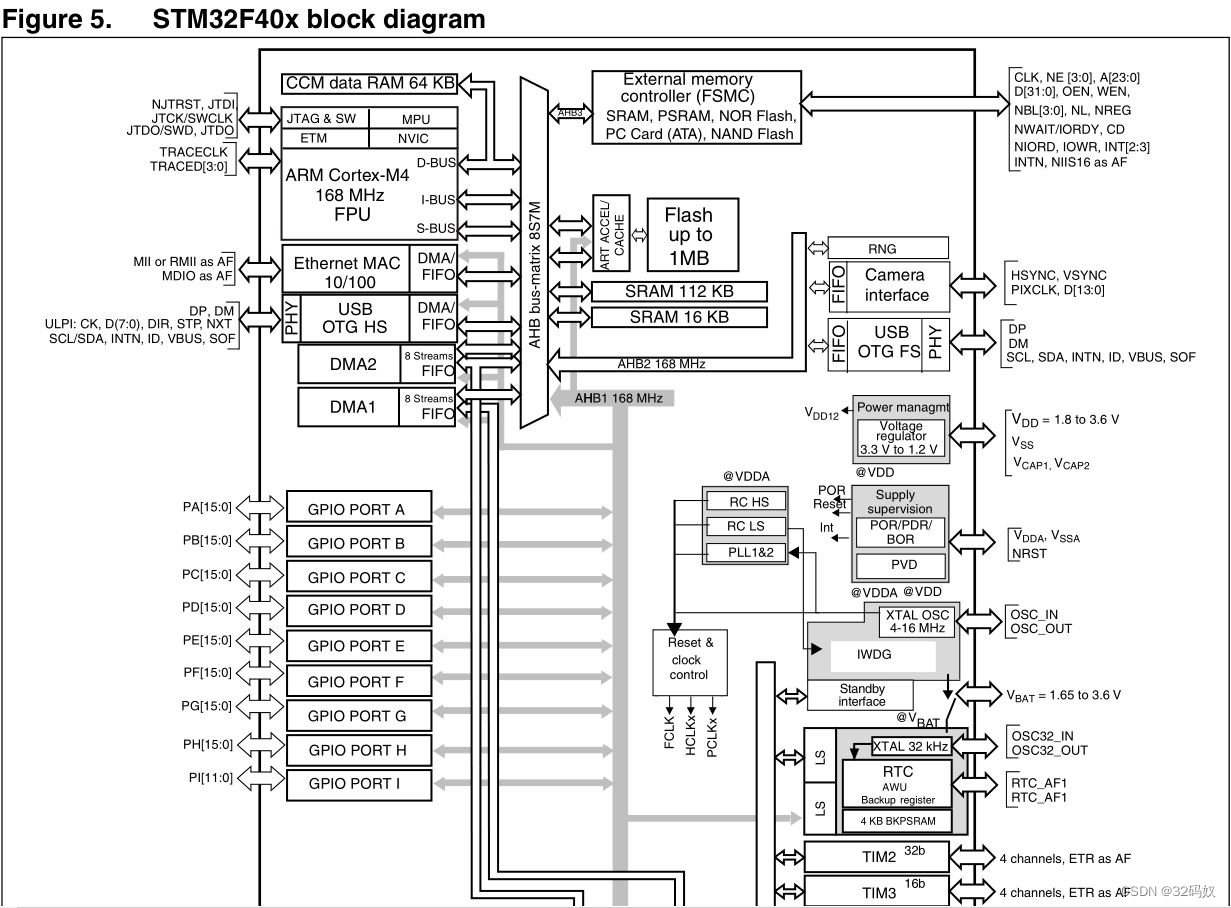

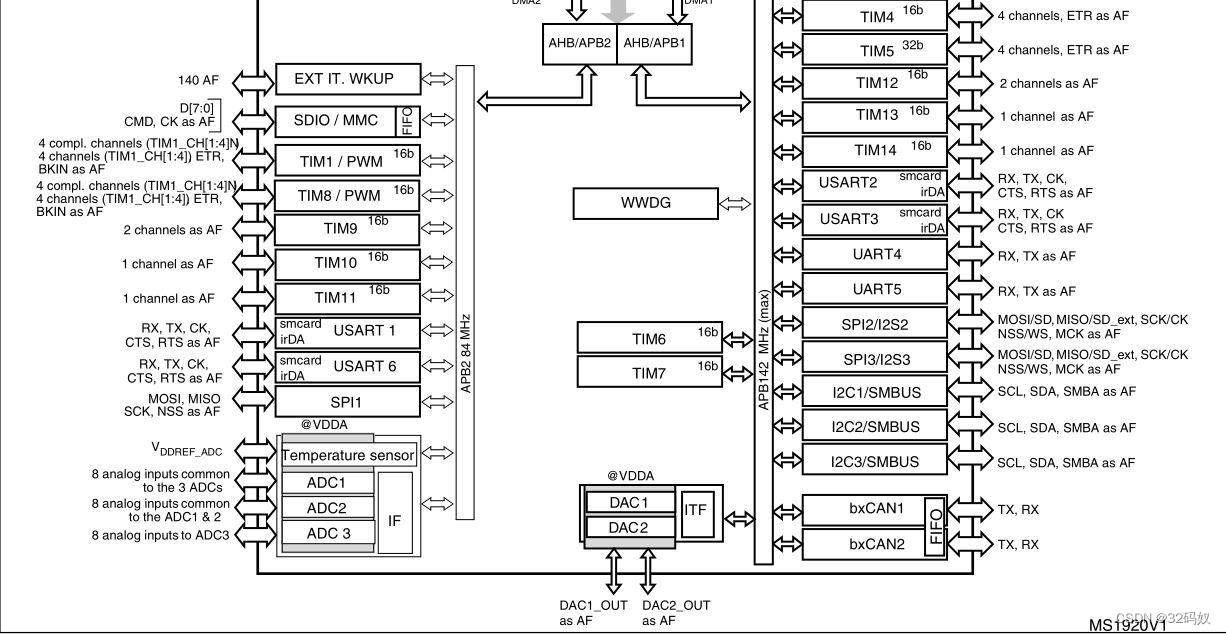

STM32F407系统框图

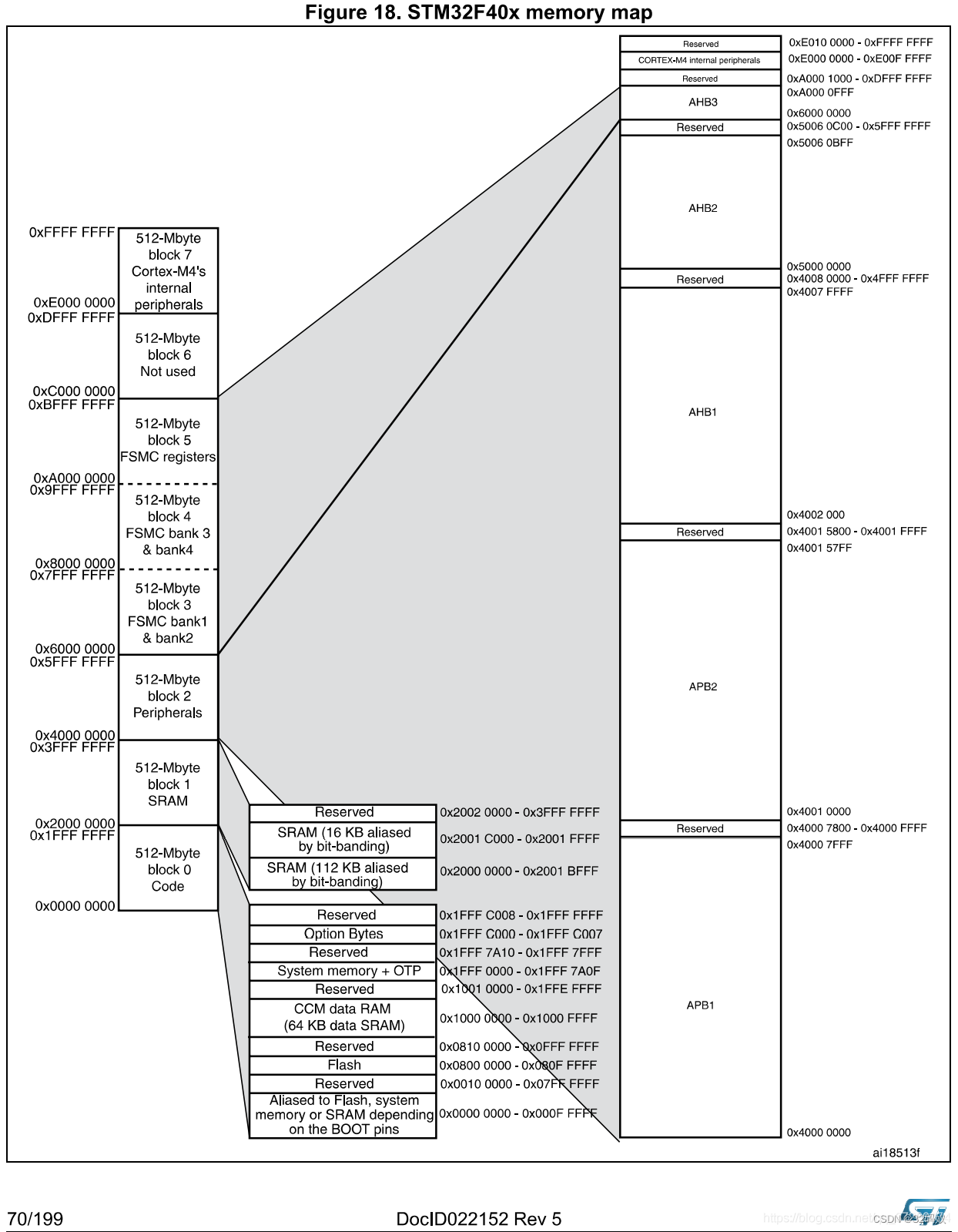

STM32F407地址分配

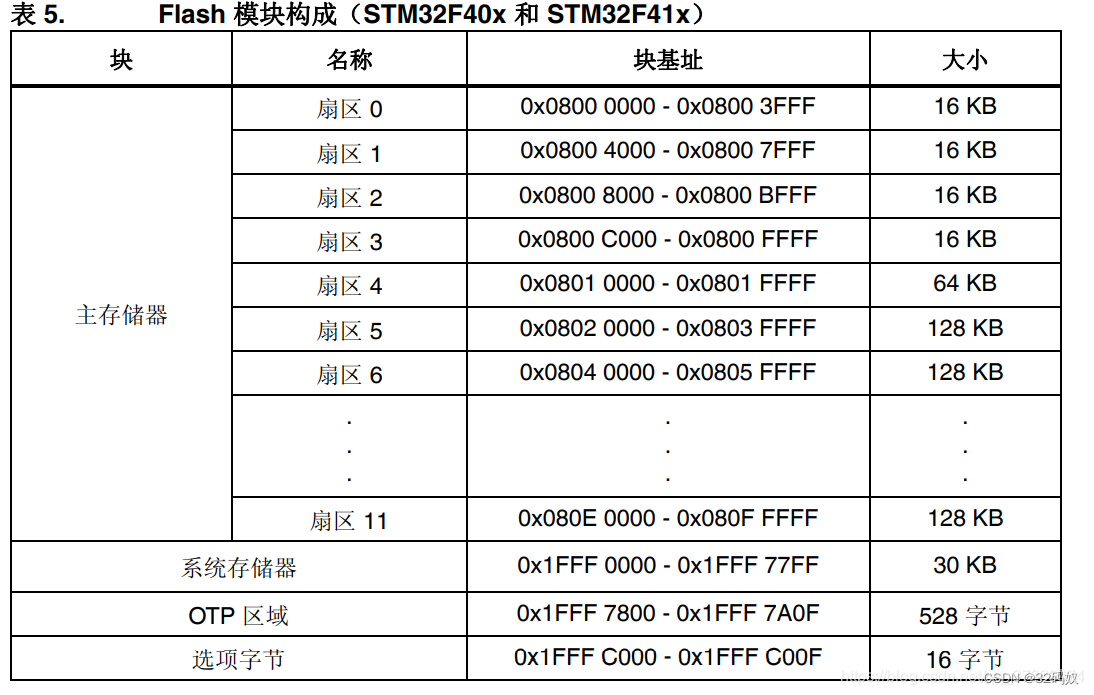

0x0800 0000开始的flash,从0x2000 0000开始的sram这两部分,其中flash是我们代码烧录的地方,sram是我们程序执行的内存地址。

STM32F407 资源分配

STM32F407是意法半导体推出的一款32位 高性能ARM Cortex-M4处理器,以下是其主要资源介绍:

-

处理器内核:采用ARM Cortex - M4内核,主频可达168MHz,具备单周期乘法和硬件除法指令,能够高效处理各种复杂的任务,支持浮点运算单元(FPU)和DSP指令,可加速浮点运算。

-

外部高速晶振(HSE)

- 频率范围:4MHz~26MHz,常用8MHz或25MHz,作为主时钟源28。

- 作用:通过锁相环(PLL)倍频生成系统主频(最高168MHz),确保高精度和高稳定性68。

-

外部低速晶振(LSE)

- 频率:32.768kHz,专用于RTC(实时时钟)和低功耗模式8。

-

内部时钟源(HSI/LSI)

- HSI:16MHz内部RC振荡器,精度较低,可作为备用时钟源48。

- LSI:32kHz,用于独立看门狗或低功耗场景

-

存储器

- 闪存:一般具有512KB到1MB(1024K)的Flash闪存,用于存储程序代码和常量数据,支持在线编程(ISP)和在应用编程(IAP),方便程序的更新和升级。

- SRAM:拥有192KB的静态随机存取存储器(SRAM),用于存放程序运行时的变量、堆栈等数据,数据访问速度快,能满足高速运算的需求。

-

时钟系统:支持多种时钟源,包括内部高速时钟(HSI)、内部低速时钟(LSI)、外部高速时钟(HSE)和外部低速时钟(LSE)。可以通过时钟配置寄存器灵活设置系统时钟频率,以满足不同应用场景对时钟精度和速度的要求。还具备多个 PLL(锁相环),用于对时钟进行倍频和分频,为系统提供稳定的时钟信号。

-

通信接口

- USART:通用同步异步收发器,多达6个USART接口,可用于与其他设备进行串口通信,如连接传感器、模块等,支持多种波特率,最高可达4.5Mbps。

- SPI:串行外设接口,有3个SPI接口,支持全双工、半双工和单工模式,可用于连接闪存、ADC、DAC等外设,最高通信速率可达50Mbps。

- I2C:集成电路总线,有3个I2C接口,支持多主机和多从机模式,可用于连接各种I2C设备,如EEPROM、传感器等,标准模式下速率为100Kbps,快速模式下可达400Kbps,高速模式下可达到1Mbps。

- USB:集成了两个USB接口,其中一个为USB OTG FS(全速)接口,另一个为USB OTG HS(高速)接口,支持USB 2.0协议,可用于连接U盘、鼠标、键盘等USB设备,或与其他设备进行高速数据传输。

- ETH:内置以太网媒体访问控制器(MAC),支持10/100Mbps以太网通信,可通过外接PHY芯片实现网络连接,方便实现设备的网络功能,如远程监控、数据传输等。

- 2个CAN2.0

-

定时器:拥有多个定时器,包括通用定时器、高级定时器和基本定时器。这些定时器可用于各种定时任务,如生成定时中断、PWM输出、测量时间间隔等。

- 定时器多达17个

- 10个通用定时器(TIM2和TIM5是32位)

- 2个基本定时器

- 2个高级定时器

- 1个系统定时器

- 2个看门狗定时器-

-

AD与DA

- ADC:具有3个12位的模数转换器(ADC),可同时进行多通道模拟信号采集,转换速度高达2.4Msps,支持多种采样模式和触发方式。

- DAC:有2个12位的数模转换器(DAC),可将数字信号转换为模拟信号输出,用于产生模拟电压或电流,输出分辨率高,可满足一些对模拟信号精度要求较高的应用。

-

IO

- 144引脚 114个IO口

- 引脚数量:共114~140个可编程IO引脚(具体取决于封装型号,如LQFP144封装提供多达114个GPIO)

- 端口分组:分为GPIOA~ GPIOI共9组,每组最多16个引脚(如GPIOA_Pin0~Pin15)

- 供电电压:所有IO引脚支持3.3V电平,部分引脚支持5V容忍(标记为FT的引脚

DMA 控制器

- STM32F407 包含 2 个 DMA 控制器,分别是 DMA1 和 DMA2。

- 每个 DMA 控制器有多个通道,DMA1 有 7 个通道,DMA2 有 5 个通道。每个通道都可以独立地配置和控制,用于不同的外设或内存之间的数据传输。

1467

1467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?