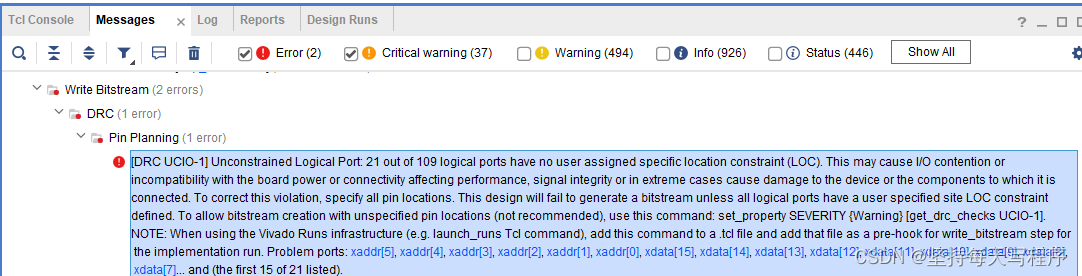

[DRC UCIO-1] Unconstrained Logical Port: 21 out of 109 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: xaddr[5], xaddr[4], xaddr[3], xaddr[2], xaddr[1], xaddr[0], xdata[15], xdata[14], xdata[13], xdata[12], xdata[11], xdata[10], xdata[9], xdata[8], xdata[7]... and (the first 15 of 21 listed).

在网上看到了很多方法,大部分都是说需要重新设置一些文件,或者说是xdc文件的注释不能和代码写在同一行,但是这些我都试了还是不行,我就根据他的建议加了一句 set_property SEVERITY {Warning} [get_drc_checks UCIO-1],然后就可以了

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?