工具:Quartus、Modelsim。

内容:用Verilog语言编写4位二进制计数器,并仿真、下载、通过逻辑分析仪在线调试。

(一)设计原理

设计4位寄存器,使用50M时钟,进行每个clk上升沿加一,完成每次计数0~15,计数器计数到15后,在时序逻辑中下一个clk计数器就归0。

(二)下板子注意事项

由于开发板的工作频率为50Mhz,因此在观察实际上板情况和逻辑分析仪采集结果时,需要加入分频模块。预设寄存器对原时钟信号计数,当记录到预设的值时,寄存器清零并翻转输出信号,由此得到频率较低的时钟。

50Mhz,周期为20ns

4位计数器的的最大值为15。

(三)模块代码

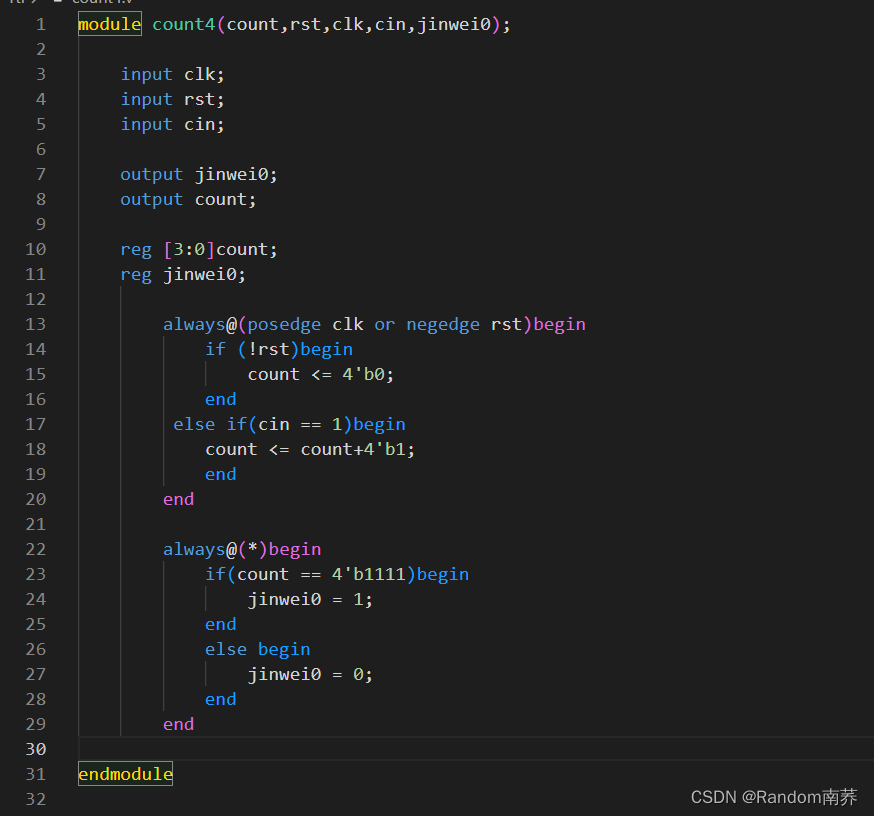

(1)4位计数器

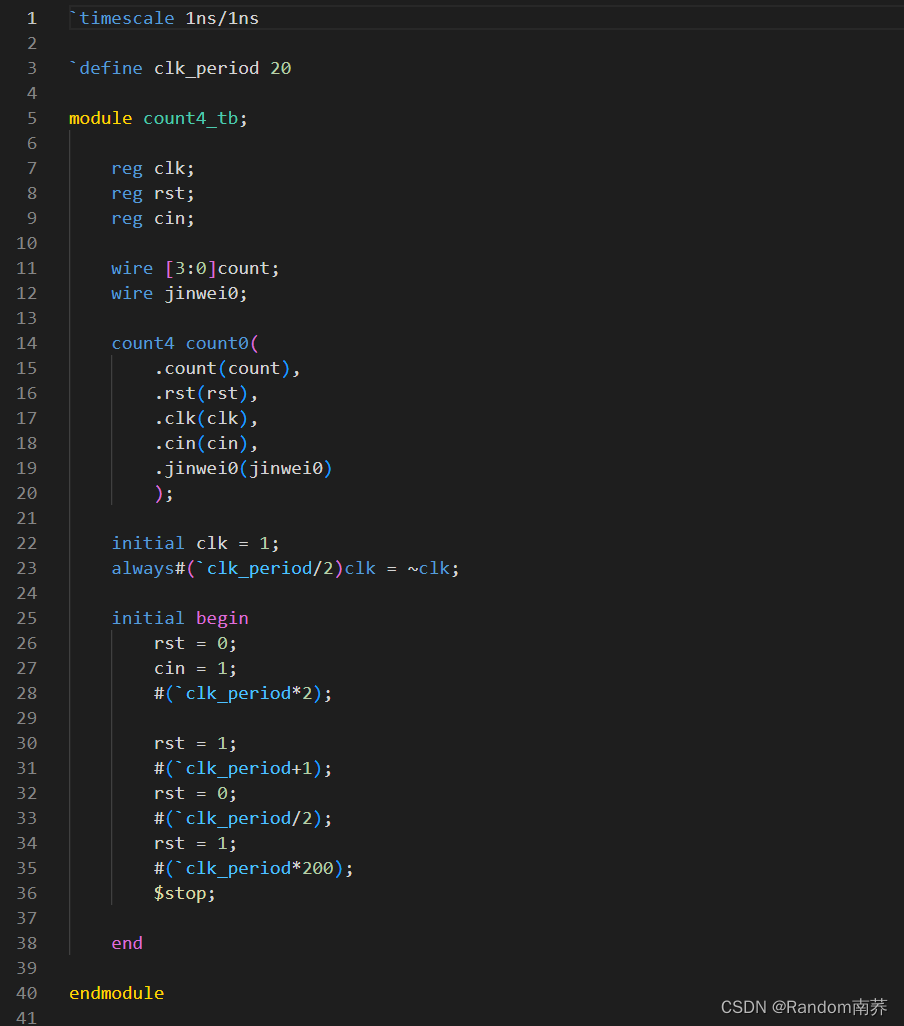

(2)4位计数器仿真tb

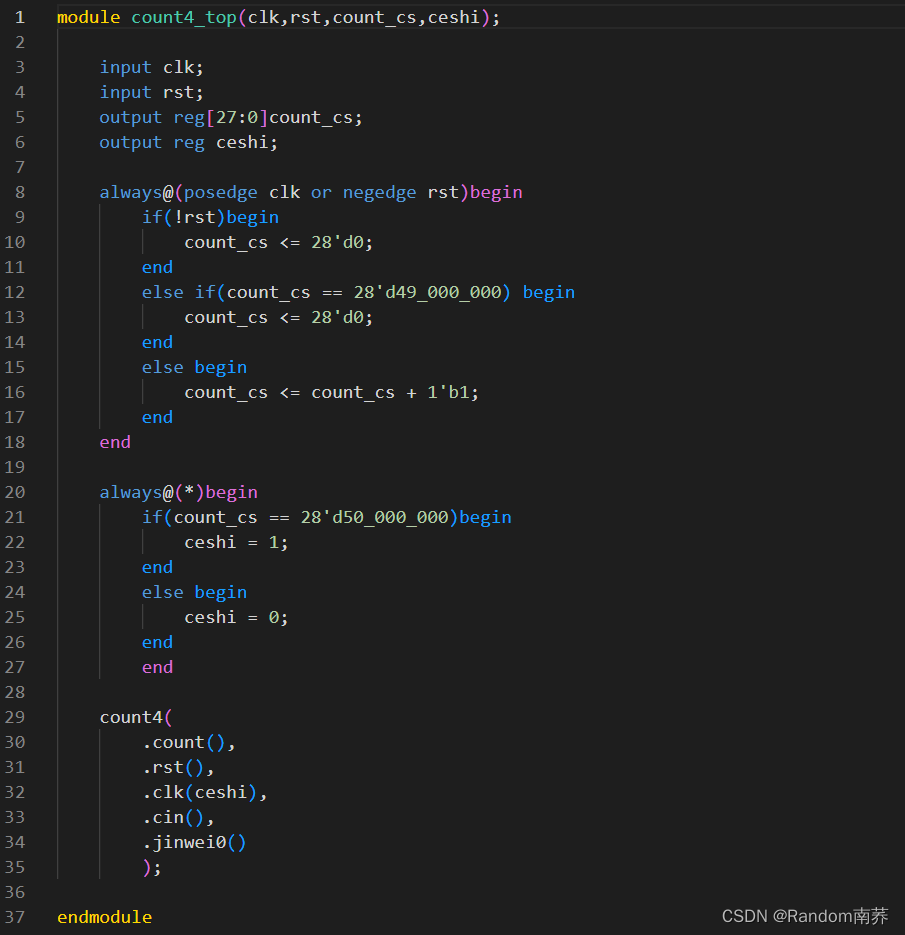

(3)4位计数器下板子

(4)Modelsim仿真图

(5)Chipscope调试图

本文介绍了如何用Verilog语言设计一个4位二进制计数器,该计数器在50MHz时钟上升沿加一,从0计数到15后自动重置。为了在50MHz工作频率的开发板上进行观察和调试,采用了分频模块生成较低频率的时钟。文中包括了计数器的模块代码、仿真测试bench、实际下板子的步骤以及通过Modelsim的仿真图和Chipscope的调试结果。

本文介绍了如何用Verilog语言设计一个4位二进制计数器,该计数器在50MHz时钟上升沿加一,从0计数到15后自动重置。为了在50MHz工作频率的开发板上进行观察和调试,采用了分频模块生成较低频率的时钟。文中包括了计数器的模块代码、仿真测试bench、实际下板子的步骤以及通过Modelsim的仿真图和Chipscope的调试结果。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?