1.AXI架构

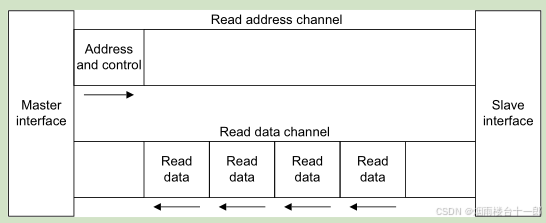

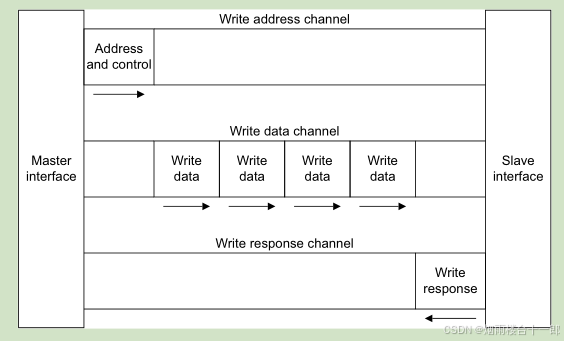

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输。

图 1-1 读架构

写架构

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit)和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的

订阅专栏 解锁全文

订阅专栏 解锁全文

2985

2985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?