模块名称: dpram() IP Core

双口RAM,有俩组数据线和地址线,读写可以同时进行,FIFO读写可以同时进行,可以看作是双口。分为Simple two-dual RAM和true two-dual RAM。简单双口RAM,一个端口只读,另一个端口只写,且写入和读取的时钟可以不同,位宽比可以不是1:1;而双口RAM两个端口都分别带有读写端口,可以在没有干扰的情况下进行读写,彼此互不干扰。

主要功能 :调用内部的资源,实现数据的读/写功能

实验目的 :了解这些芯片专用硬件资源的情况下,将其合理的应用到对应的系统中

FPGA 芯片的内部结构:

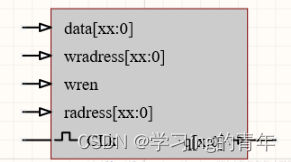

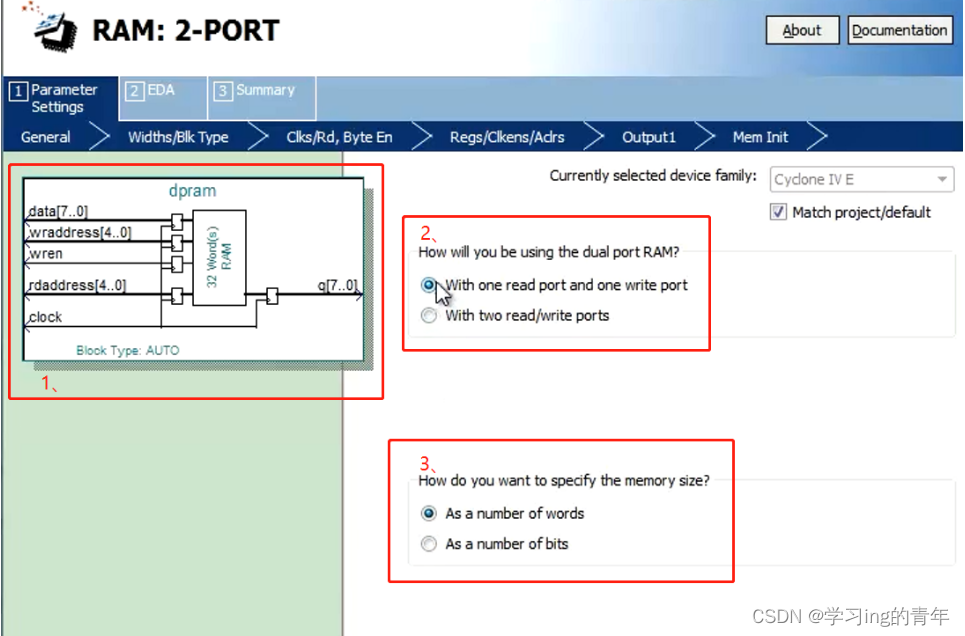

1、针对上面的结构图,我们可以看到 几个信号线

data[7:0],表示的是即将写入的数据

wraddress [4:0]: 表示的是数据要写入或者说是数据要存入的地址

wren : 表示数据写入使能信号

readdress[4:0] : 表示读取数据的地址

q[7:0 ]: 表示的是读取的该地址的数据。

clk : 时钟

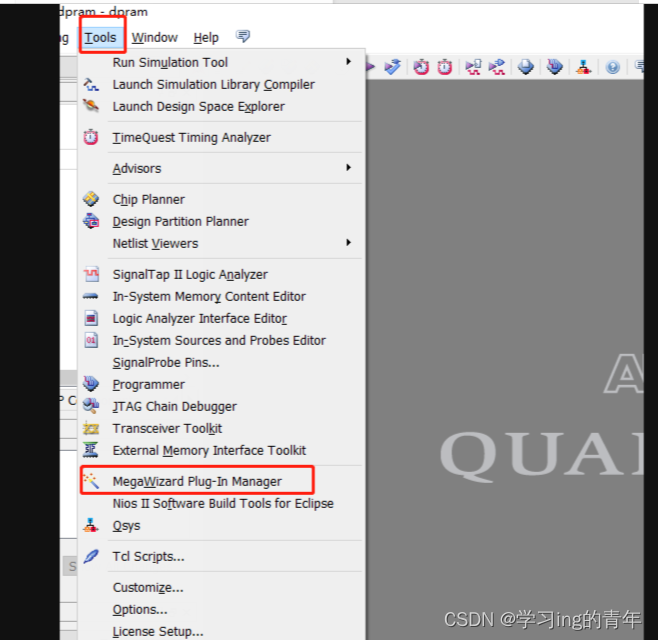

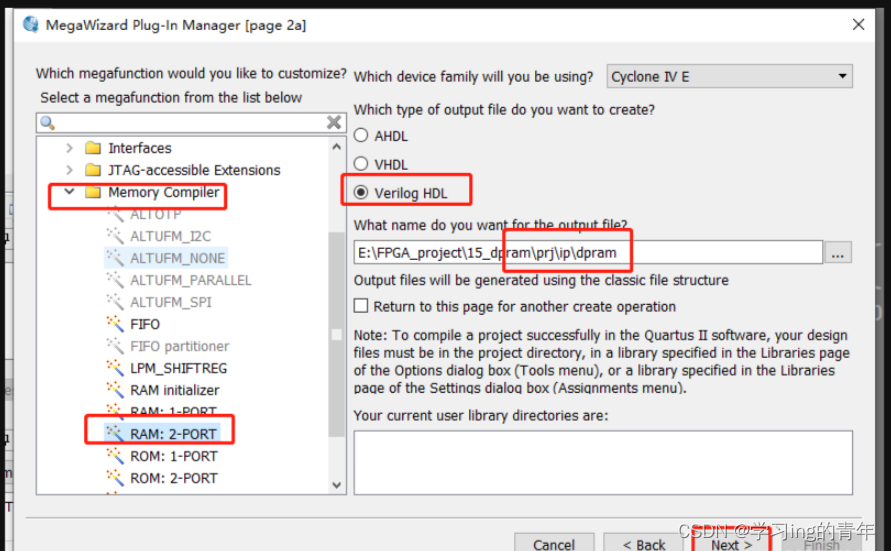

2、如何使用双端口ram模块

① 一个读端口,一个写端口

②两个都是读/写端口

3、内存结构单元的大小

1、使用字节作为一个存取单

2、使用bit作为一个存取单元

ram 配置的类型

对双口RAM【类似与电脑的内存条空间】的解释

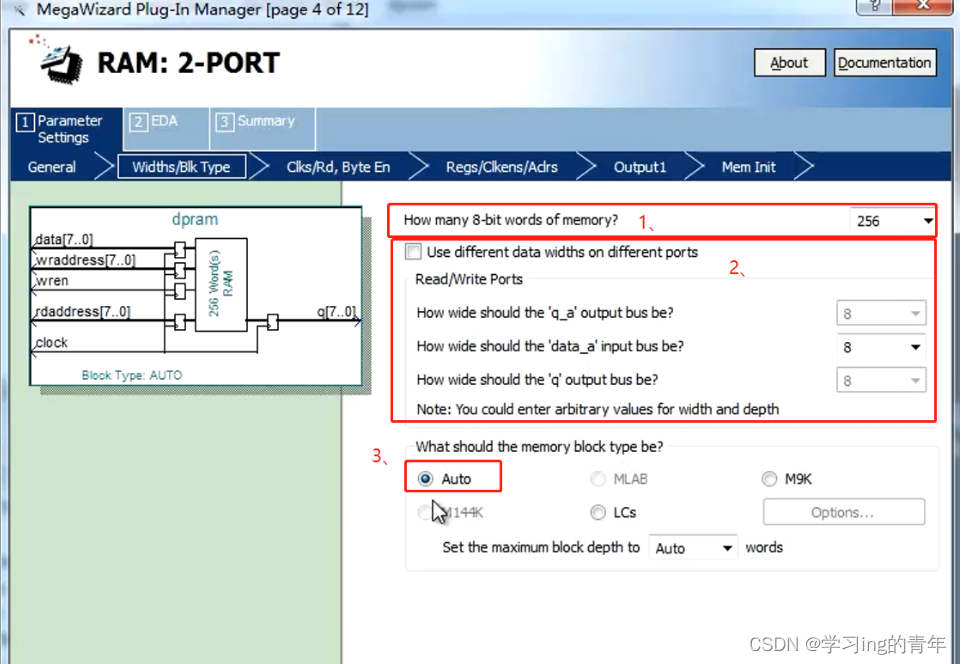

1、选择开辟的8bit(我们在上一张配置的结果中选择的是一个字节)的内存大小,这里是选择了 256字节

2、使用不同的数据对应着不同的位宽

理解: 这个的话就类似与整体的数据大小(size)和address的分配的一种对应关系

由上述 256字节来说

假设我们使用 8位数据输入,那么address就是[7:0]的地址

那么,如果在输出端配置的是:

① 8位数据输出,即q[7:0] ,那么 rdaddress也是 [7:0]

②16位数据输出,即q[15:0],那么 rdaddress就是[6:0]即可

也就是说,输入和输出是不一定都是相匹配的,可以根据自己的需求进行更改。

3、申请内存的分配的结构类型

默认选 auto(自动分配内存), M9K 和LCs的还不太了解。

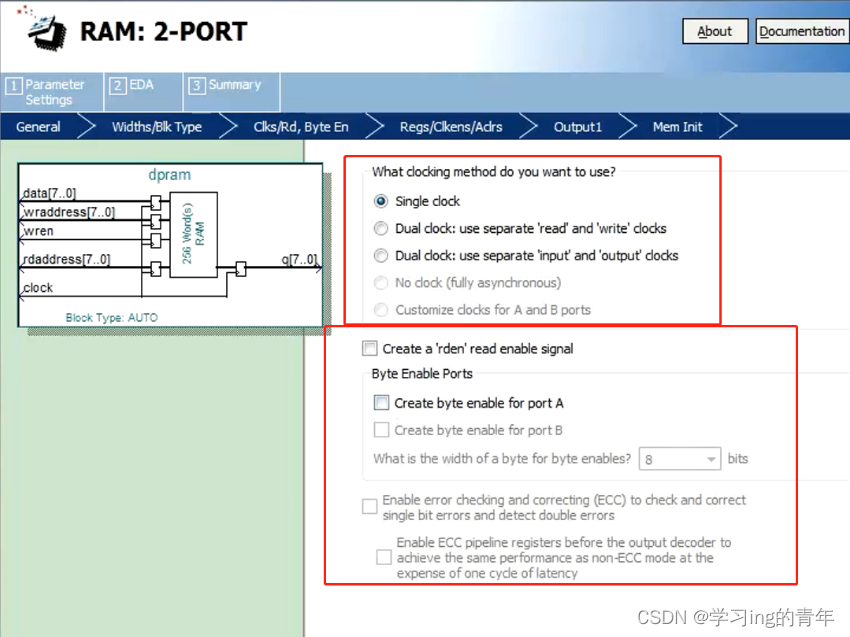

1、第一个是时钟的配置

①选用单时钟

②读和写使用不同的时钟

③输入和输出使用不同的时钟

2、是否要创建读使能信号

下面的配置主要针对的是大于8位的位宽来进行配置的(暂时不管)

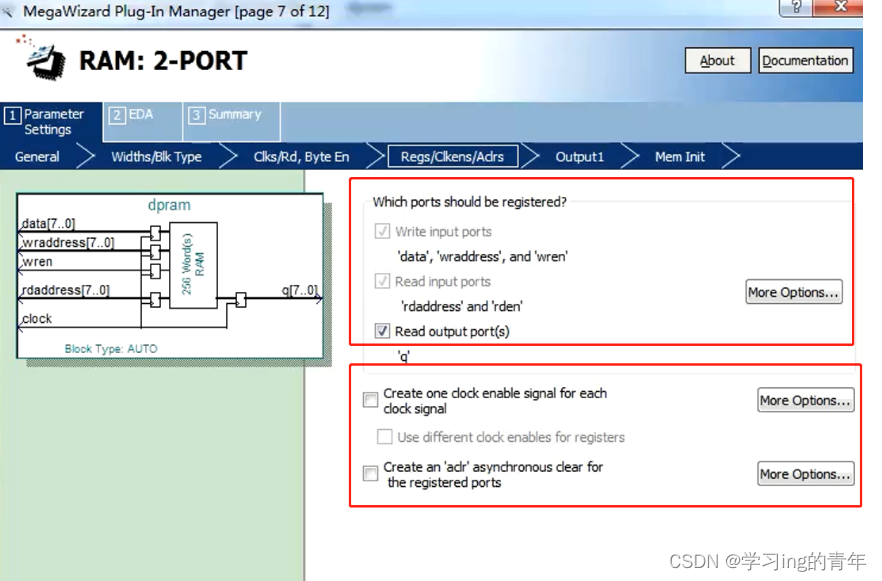

1、是否要使用寄存器(默认选择使用即可)

2、创建一个时钟使能信号(不用)

3、创建一个寄存器清零信号(暂时不用)

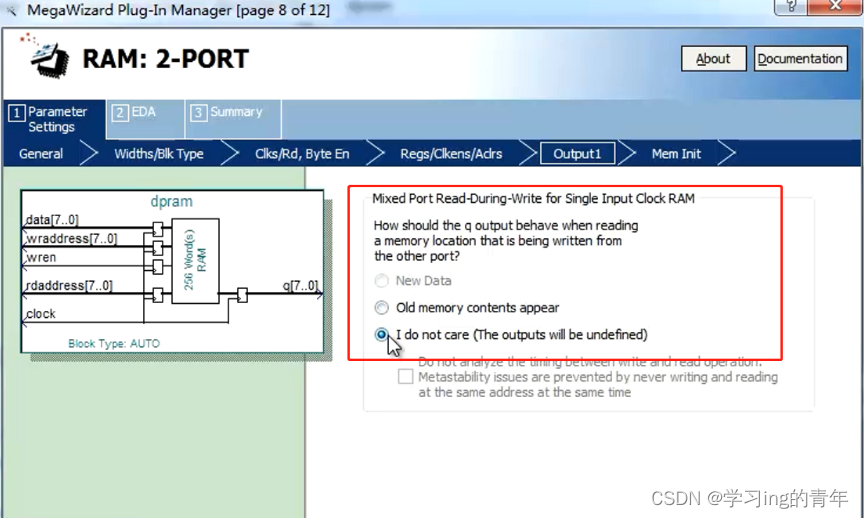

本次我们使用的读和写数据使用的是同一个时钟,当我们同时在读和写同一个地址的数据的时候,我们需要认为此时q输出的数据是:

① 读取之前的数据

② 我不关心是之前的还是当前写入的(本次选用的是下面的方案)

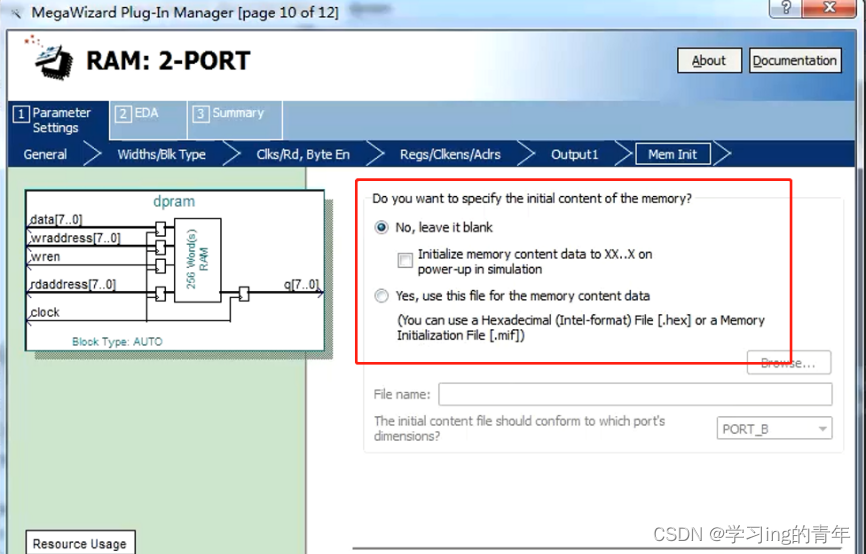

1、如何初始化你的内存(RAM)

① 让其保持空白

②使用mif文件对内存进行初始化

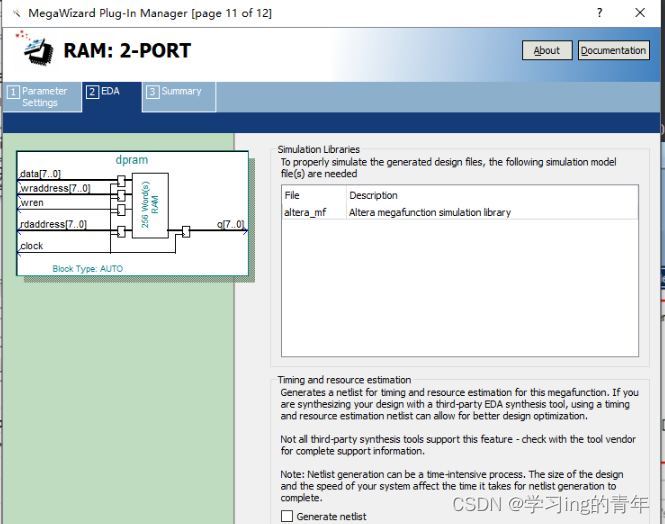

next

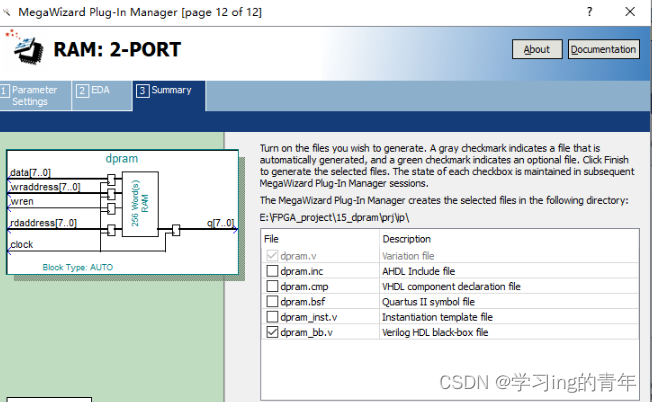

直接finish

本实验主要是熟悉和了解ram的使用:

以下是个人总结:

1、了解ram,其实ram就是我们说的内存,但是在我们实现的时候,就是要对内存执行【读/写】两个操作。

我们一般来说,写操作就是将输入写入到指定的地址中,【读】操作就是将存在在某个地址的数据读取出来。

生活实例:

这个可以理解为我们图书馆里面的书架,每个格子里面都可以存放书本(注:是任意或者非固定目标的书本),然后每个格子里面也各有标号。当我们需要读取的时候,只要对对应的格子编号,就可以找我我们要的书。

这个和ram是类似的,也就是说,地址里面的数据是可以根据自己的想法来改变的。

生成的dpram.v

// megafunction wizard: %RAM: 2-PORT%

// GENERATION: STANDARD

// VERSION: WM1.0

// MODULE: altsyncram

// ============================================================

// File Name: dpram.v

// Megafunction Name(s):

// altsyncram

//

// Simulation Library Files(s):

// altera_mf

// ============================================================

// ************************************************************

// THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

//

// 13.0.0 Build 156 04/24/2013 SJ Full Version

// ************************************************************

//Copyright (C) 1991-2013 Altera Corporation

//Your use of Altera Corporation's design tools, logic functions

//and other software and tools, and its AMPP partner logic

//functions, and any output files from any of the foregoing

//(including device programming or simulation files), and any

//associated documentation or information are expressly subject

//to the terms and conditions of the Altera Program License

//Subscription Agreement, Altera MegaCore Function License

//Agreement, or other applicable license agreement, including,

//without limitation, that your use is for the sole purpose of

//programming logic devices manufactured by Altera and sold by

//Altera or its authorized distributors. Please refer to the

//applicable agreement for further details.

// synopsys translate_off

`timescale 1 ps / 1 ps

// synopsys translate_on

module dpram (

clock,

data,

rdaddress,

wraddress,

wren,

q);

input clock;

input [7:0] data;

input [7:0] rdaddress;

input [7:0] wraddress;

input wren;

output [7:0] q;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_off

`endif

tri1 clock;

tri0 wren;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_on

`endif

wire [7:0] sub_wire0;

wire [7:0] q = sub_wire0[7:0];

altsyncram altsyncram_component (

.address_a (wraddress),

.clock0 (clock),

.data_a (data),

.wren_a (wren),

.address_b (rdaddress),

.q_b (sub_wire0),

.aclr0 (1'b0),

.aclr1 (1'b0),

.addressstall_a (1'b0),

.addressstall_b (1'b0),

.byteena_a (1'b1),

.byteena_b (1'b1),

.clock1 (1'b1),

.clocken0 (1'b1),

.clocken1 (1'b1),

.clocken2 (1'b1),

.clocken3 (1'b1),

.data_b ({8{1'b1}}),

.eccstatus (),

.q_a (),

.rden_a (1'b1),

.rden_b (1'b1),

.wren_b (1'b0));

defparam

altsyncram_component.address_aclr_b = "NONE",

altsyncram_component.address_reg_b = "CLOCK0",

altsyncram_component.clock_enable_input_a = "BYPASS",

altsyncram_component.clock_enable_input_b = "BYPASS",

altsyncram_component.clock_enable_output_b = "BYPASS",

altsyncram_component.intended_device_family = "Cyclone IV E",

altsyncram_component.lpm_type = "altsyncram",

altsyncram_component.numwords_a = 256,

altsyncram_component.numwords_b = 256,

altsyncram_component.operation_mode = "DUAL_PORT",

altsyncram_component.outdata_aclr_b = "NONE",

altsyncram_component.outdata_reg_b = "CLOCK0",

altsyncram_component.power_up_uninitialized = "FALSE",

altsyncram_component.read_during_write_mode_mixed_ports = "DONT_CARE",

altsyncram_component.widthad_a = 8,

altsyncram_component.widthad_b = 8,

altsyncram_component.width_a = 8,

altsyncram_component.width_b = 8,

altsyncram_component.width_byteena_a = 1;

endmodule

// ============================================================

// CNX file retrieval info

// ============================================================

// Retrieval info: PRIVATE: ADDRESSSTALL_A NUMERIC "0"

// Retrieval info: PRIVATE: ADDRESSSTALL_B NUMERIC "0"

// Retrieval info: PRIVATE: BYTEENA_ACLR_A NUMERIC "0"

// Retrieval info: PRIVATE: BYTEENA_ACLR_B NUMERIC "0"

// Retrieval info: PRIVATE: BYTE_ENABLE_A NUMERIC "0"

// Retrieval info: PRIVATE: BYTE_ENABLE_B NUMERIC "0"

// Retrieval info: PRIVATE: BYTE_SIZE NUMERIC "8"

// Retrieval info: PRIVATE: BlankMemory NUMERIC "1"

// Retrieval info: PRIVATE: CLOCK_ENABLE_INPUT_A NUMERIC "0"

// Retrieval info: PRIVATE: CLOCK_ENABLE_INPUT_B NUMERIC "0"

// Retrieval info: PRIVATE: CLOCK_ENABLE_OUTPUT_A NUMERIC "0"

// Retrieval info: PRIVATE: CLOCK_ENABLE_OUTPUT_B NUMERIC "0"

// Retrieval info: PRIVATE: CLRdata NUMERIC "0"

// Retrieval info: PRIVATE: CLRq NUMERIC "0"

// Retrieval info: PRIVATE: CLRrdaddress NUMERIC "0"

// Retrieval info: PRIVATE: CLRrren NUMERIC "0"

// Retrieval info: PRIVATE: CLRwraddress NUMERIC "0"

// Retrieval info: PRIVATE: CLRwren NUMERIC "0"

// Retrieval info: PRIVATE: Clock NUMERIC "0"

// Retrieval info: PRIVATE: Clock_A NUMERIC "0"

// Retrieval info: PRIVATE: Clock_B NUMERIC "0"

// Retrieval info: PRIVATE: IMPLEMENT_IN_LES NUMERIC "0"

// Retrieval info: PRIVATE: INDATA_ACLR_B NUMERIC "0"

// Retrieval info: PRIVATE: INDATA_REG_B NUMERIC "0"

// Retrieval info: PRIVATE: INIT_FILE_LAYOUT STRING "PORT_B"

// Retrieval info: PRIVATE: INIT_TO_SIM_X NUMERIC "0"

// Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E"

// Retrieval info: PRIVATE: JTAG_ENABLED NUMERIC "0"

// Retrieval info: PRIVATE: JTAG_ID STRING "NONE"

// Retrieval info: PRIVATE: MAXIMUM_DEPTH NUMERIC "0"

// Retrieval info: PRIVATE: MEMSIZE NUMERIC "2048"

// Retrieval info: PRIVATE: MEM_IN_BITS NUMERIC "0"

// Retrieval info: PRIVATE: MIFfilename STRING ""

// Retrieval info: PRIVATE: OPERATION_MODE NUMERIC "2"

// Retrieval info: PRIVATE: OUTDATA_ACLR_B NUMERIC "0"

// Retrieval info: PRIVATE: OUTDATA_REG_B NUMERIC "1"

// Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0"

// Retrieval info: PRIVATE: READ_DURING_WRITE_MODE_MIXED_PORTS NUMERIC "2"

// Retrieval info: PRIVATE: READ_DURING_WRITE_MODE_PORT_A NUMERIC "3"

// Retrieval info: PRIVATE: READ_DURING_WRITE_MODE_PORT_B NUMERIC "3"

// Retrieval info: PRIVATE: REGdata NUMERIC "1"

// Retrieval info: PRIVATE: REGq NUMERIC "0"

// Retrieval info: PRIVATE: REGrdaddress NUMERIC "1"

// Retrieval info: PRIVATE: REGrren NUMERIC "1"

// Retrieval info: PRIVATE: REGwraddress NUMERIC "1"

// Retrieval info: PRIVATE: REGwren NUMERIC "1"

// Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0"

// Retrieval info: PRIVATE: USE_DIFF_CLKEN NUMERIC "0"

// Retrieval info: PRIVATE: UseDPRAM NUMERIC "1"

// Retrieval info: PRIVATE: VarWidth NUMERIC "0"

// Retrieval info: PRIVATE: WIDTH_READ_A NUMERIC "8"

// Retrieval info: PRIVATE: WIDTH_READ_B NUMERIC "8"

// Retrieval info: PRIVATE: WIDTH_WRITE_A NUMERIC "8"

// Retrieval info: PRIVATE: WIDTH_WRITE_B NUMERIC "8"

// Retrieval info: PRIVATE: WRADDR_ACLR_B NUMERIC "0"

// Retrieval info: PRIVATE: WRADDR_REG_B NUMERIC "0"

// Retrieval info: PRIVATE: WRCTRL_ACLR_B NUMERIC "0"

// Retrieval info: PRIVATE: enable NUMERIC "0"

// Retrieval info: PRIVATE: rden NUMERIC "0"

// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all

// Retrieval info: CONSTANT: ADDRESS_ACLR_B STRING "NONE"

// Retrieval info: CONSTANT: ADDRESS_REG_B STRING "CLOCK0"

// Retrieval info: CONSTANT: CLOCK_ENABLE_INPUT_A STRING "BYPASS"

// Retrieval info: CONSTANT: CLOCK_ENABLE_INPUT_B STRING "BYPASS"

// Retrieval info: CONSTANT: CLOCK_ENABLE_OUTPUT_B STRING "BYPASS"

// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E"

// Retrieval info: CONSTANT: LPM_TYPE STRING "altsyncram"

// Retrieval info: CONSTANT: NUMWORDS_A NUMERIC "256"

// Retrieval info: CONSTANT: NUMWORDS_B NUMERIC "256"

// Retrieval info: CONSTANT: OPERATION_MODE STRING "DUAL_PORT"

// Retrieval info: CONSTANT: OUTDATA_ACLR_B STRING "NONE"

// Retrieval info: CONSTANT: OUTDATA_REG_B STRING "CLOCK0"

// Retrieval info: CONSTANT: POWER_UP_UNINITIALIZED STRING "FALSE"

// Retrieval info: CONSTANT: READ_DURING_WRITE_MODE_MIXED_PORTS STRING "DONT_CARE"

// Retrieval info: CONSTANT: WIDTHAD_A NUMERIC "8"

// Retrieval info: CONSTANT: WIDTHAD_B NUMERIC "8"

// Retrieval info: CONSTANT: WIDTH_A NUMERIC "8"

// Retrieval info: CONSTANT: WIDTH_B NUMERIC "8"

// Retrieval info: CONSTANT: WIDTH_BYTEENA_A NUMERIC "1"

// Retrieval info: USED_PORT: clock 0 0 0 0 INPUT VCC "clock"

// Retrieval info: USED_PORT: data 0 0 8 0 INPUT NODEFVAL "data[7..0]"

// Retrieval info: USED_PORT: q 0 0 8 0 OUTPUT NODEFVAL "q[7..0]"

// Retrieval info: USED_PORT: rdaddress 0 0 8 0 INPUT NODEFVAL "rdaddress[7..0]"

// Retrieval info: USED_PORT: wraddress 0 0 8 0 INPUT NODEFVAL "wraddress[7..0]"

// Retrieval info: USED_PORT: wren 0 0 0 0 INPUT GND "wren"

// Retrieval info: CONNECT: @address_a 0 0 8 0 wraddress 0 0 8 0

// Retrieval info: CONNECT: @address_b 0 0 8 0 rdaddress 0 0 8 0

// Retrieval info: CONNECT: @clock0 0 0 0 0 clock 0 0 0 0

// Retrieval info: CONNECT: @data_a 0 0 8 0 data 0 0 8 0

// Retrieval info: CONNECT: @wren_a 0 0 0 0 wren 0 0 0 0

// Retrieval info: CONNECT: q 0 0 8 0 @q_b 0 0 8 0

// Retrieval info: GEN_FILE: TYPE_NORMAL dpram.v TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL dpram.inc FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL dpram.cmp FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL dpram.bsf FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL dpram_inst.v FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL dpram_bb.v TRUE

// Retrieval info: LIB_FILE: altera_mf

测试代码:

`timescale 1ns/1ns

`define clk_period 20

module dpram_tb;

reg clock;

reg [7:0]data;

reg [7:0]rdaddress;

reg [7:0]wraddress;

reg wren;

wire [7:0]q;

integer i;

dpram dpram0(

.clock(clock),

.data(data),

.rdaddress(rdaddress),

.wraddress(wraddress),

.wren(wren),

.q(q)

);

initial clock = 1;

always#(`clk_period/2)clock = ~clock;

initial begin

data = 0;

rdaddress = 30;

wraddress = 0;

wren = 0;

#(`clk_period*20 +1 );

for (i=0;i<=15;i=i+1)begin

wren = 1;

data = 255 - i;

wraddress = i;

#`clk_period;

end

wren = 0;

#(`clk_period*20);

for (i=0;i<=15;i=i+1)begin

rdaddress = i;

#`clk_period;

end

#(`clk_period*20);

$stop;

end

endmodule

本文详细介绍了FPGA芯片中的双口RAM模块,包括Simple双口RAM和True双口RAM的区别,以及它们在数据读写、时钟配置和内存分配方面的特点。实验目的是理解如何合理利用这些硬件资源。文中还提供了配置示例,如时钟选择、内存大小和位宽设置,并给出了一个简单的测试代码来演示双口RAM的使用。

本文详细介绍了FPGA芯片中的双口RAM模块,包括Simple双口RAM和True双口RAM的区别,以及它们在数据读写、时钟配置和内存分配方面的特点。实验目的是理解如何合理利用这些硬件资源。文中还提供了配置示例,如时钟选择、内存大小和位宽设置,并给出了一个简单的测试代码来演示双口RAM的使用。

3365

3365

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?