文章目录

AXI:Advanced eXtensible Interface 高级可扩展接口

AXI是AMBA总线协议的一种,AMBA是ARM公司1996年首次推出的微控制器总线协议。

概述

AXI的三类接口

通常所说的AXI指AXI4,有三类接口:

- AXI4-Full:用于高性能内存映射需求。

- AXI4-Lite:用于简单的地吞吐量内存映射通信(例如,进出控制寄存器和状态寄存器)

- AXI4-Stream:用于高速流数据

从Spartan-6和Virtex-6器件开始,Xilinx的IP开始采用AXI接口。后续的UltraScale架构、Zynq-7000系列全部使用AXI总线。

AXI总线在Xilinx产品中被广泛采用,主要是高效、灵活、便捷。

AXI的特点

高效:

通过对AXI接口进行标准化,开发人员只需学习用于IP的单一协议。

灵活:

AXI4适用于内存映射接口,仅一个地址阶段就允许高达256个数据传输周期的高吞吐量爆发。

AXI4-Lite是一个轻量级的传输接口,逻辑占用很小,在设计和使用上都是一个简单的接口。

AXI4-Stream完全取消了对地址阶段的要求,并允许无限的数据突发大小。

便携:

使用AXI协议,不仅可以访问Vivado IP目录,还可以访问ARM合作伙伴的全球社区。许多IP提供商支持AXI协议。

一个强大的第三方AXI工具供应商集合,提供许多验证、系统开发和性能表征工具。

AXI的五个通道

AXI4和AXI4-Lite接口都有5个不同的通道组成,每个通道有若干个接口信号。

- 读地址通道

- 写地址通道

- 读数据通道

- 写数据通道

- 写响应通道

AXI的时序

为了理解AXI的读写时序,首先需要理解基于valid-ready的握手机制,然后理解AXI的读/写流程,接着理解给出AXI所有接口信号的含义,

最后理解AXI读写的时序图,并以一个简单的AXI接口的block design为例进行仿真,查看波形图。

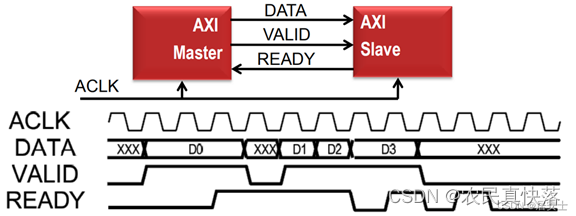

AXI的握手机制

AXI 基于valid-ready的握手机制:

发送方(主)通过置高 vaild 信号表示地址/数据/控制信息已准备好,并保持在消息总线上;

接收方(从)通过置高 ready 信号表示接收方已做好接收的准备。在 ACLK 上升沿,若 vaild、ready 同时为高,则进行数据传输。

注意①:

valid和ready不能相互依赖,避免产生相互等待的死锁, 通常建议ready和valid完全独立,这样主从双方都有终止通信的能力。 若想要从机接收全部的来自主机的数据,可设 ready = H 。

注意②:

根据 valid、ready 到达时间,可以分为 3 种情况,如右图。 应当注意到,在 valid 置高的同时,发送方就应该给出有效数据,并将有效数据保持在总线,而在之后的 ACLK 上升沿,若 valid、ready 均有效,则应更新有效数据。

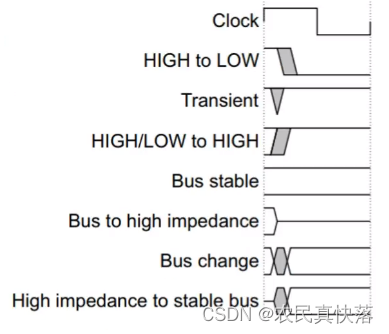

关键时序图形的约定

AXI的读写流程

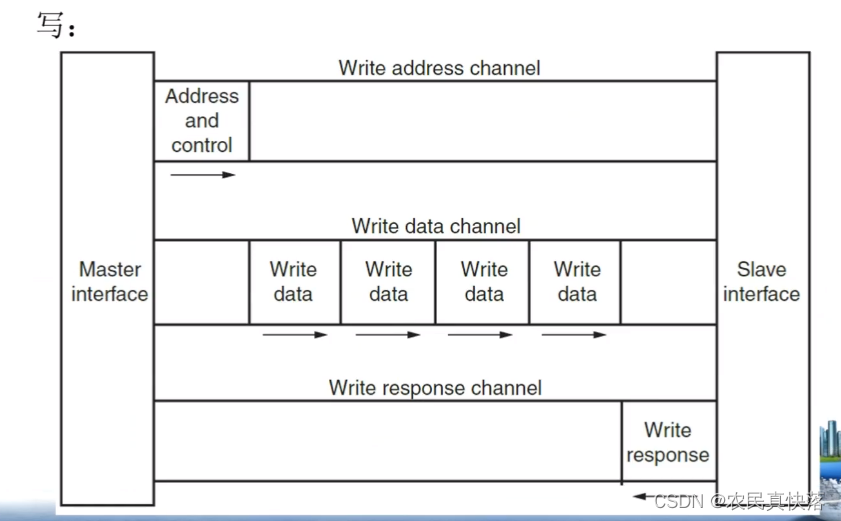

写操作

写流程如图,涉及到写地址通道 AWC、写数据通道 DWC、写回复通道 RC 三个通道。

- 首先, master 在 写地址通道 上给出写地址和控制信息。

- 然后,在 写数据通道 上传输数据,AXI 的数据传输是突发性的,一次可传输多个数据,在传输最后一个数据时,须同步给出 last 信号以表示数据传输即将终止。

- 最后, slave 将在 写响应通道 上给出写响应消息,对本次数据传输表示确认。

读操作

**读流程如图,**涉及读地址通道 ARC、读数据通道 DRC 两个通道。

4. 首先, master 在 读地址通道 上给出读地址和控制消息,

5. 然后,slave 将在 读数据通道 上给出数据。

值得注意的是,读数据通道 集成了读回复功能,且是从 slave 发送给 master 的,在 slave 完成数据传输后,会在读数据通道 上给出回复消息,标志一次读取结束。

此外,AXI 可以连接成多对多的拓扑,这可以借助 AXI Interconnect IP 来实现。

本文详细阐述了AXI协议的分类、三种接口(AXI4-Full,AXI4-Lite,AXI4-Stream)特点,以及其五个通道和高效的时序机制。通过AXI读写实例和BlockDesign仿真展示了协议的工作流程,适合理解和应用AXI技术的开发者。

本文详细阐述了AXI协议的分类、三种接口(AXI4-Full,AXI4-Lite,AXI4-Stream)特点,以及其五个通道和高效的时序机制。通过AXI读写实例和BlockDesign仿真展示了协议的工作流程,适合理解和应用AXI技术的开发者。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1594

1594