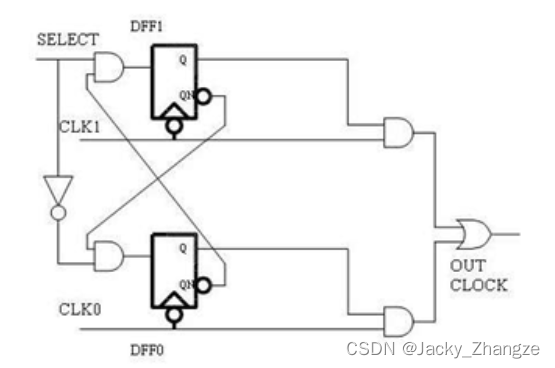

倍数时钟切换:使用下降沿保证切换发生在本clk低电平时候,引入输入反馈,保证另一路时 钟为低电平时候切换。

为什么在低电平时进行时钟切换?

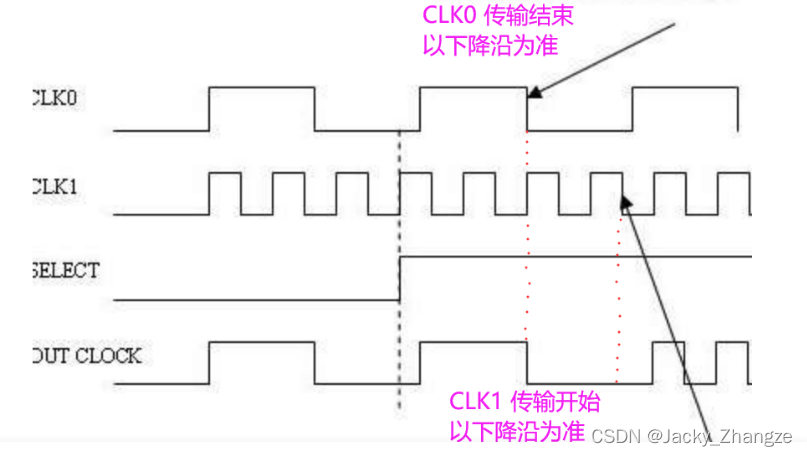

在两个电平相反的时候切换时钟,肯定有毛刺;电平相同的时候,即使不产生毛刺,时钟切换后的第一个时钟的周期或占空比也不是理想的。所以,为避免毛刺的产生,需要在两个时钟都为低电平的时候进行时钟切换。

module clk_switch(

input clk1,

input clk2,

input rst_n,

input sel,

output clk

);

reg out1,out2;

always@(negedge clk1 or negedge rst_n)begin

if(!rst_n)

out1<=0;

else

out1<=sel&~out2;

end

always@(negedge clk2 or negedge rst_n)begin

if(!rst_n)

out2<=0;

else

out2<=~sel&~out1;

end

assign clk=(out1&clk1)|(out2&clk2);

endmodule异步时钟无缝切换

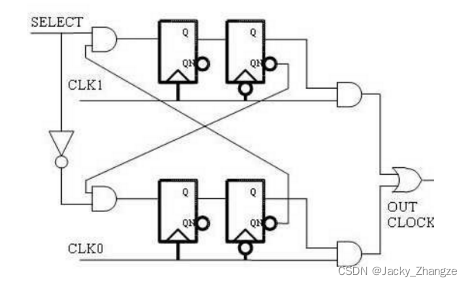

DFF1和DFF3打一拍降低亚稳态发生的概率

DFF2和DFF4下降沿采样是为了避免产生glitch(毛刺)。

1、select选择信号有DFF延迟

2、什么在下降沿采样:SELECT与反馈输出相与,下降沿采样反馈可以保证一个时钟被完全取消选择后,输出才输出另一个时钟,从而避免产生毛刺。

1.SELECT为0时,下面两个触发器的输出为1,CLK0被开启。

2.当SELECT在第一条虚线处变为高电平时,在下一个到来的CLK0的上升沿,左下角寄存器的输出变为0,下一个CLK1的下降沿到来时,右下角QN的输出还未被更新,输出仍为0,因此SELECT和它相与后为0。

3.直到CLK0的下降沿到来,右下角寄存器的输出更新为0,从而QN为1,左上角寄存器的输出端D变为1.

4.这之后CLK1的上升沿,左上角的寄存器采样到D=1,因此Q=1。

5.CLK1的下一个下降沿,右上角的寄存器采样到D=1,因此输出Q=1,CLK1开启。至此,完成了时钟的切换。

————————————————

波形图原链接

原文链接:https://blog.youkuaiyun.com/qq_40268672/article/details/123340678

module clk_switch(

input clk1,

input clk2,

input rst_n,

input sel,

output clk

);

reg out1,out2;

reg out1_reg,out2_reg;

always@(posedge clk1 or negedge rst_n)begin

if(!rst_n)

out1<=0;

else

out1<=sel&~out2;

end

always@(negedge clk1 or negedge rst_n)begin

if(!rst_n)

out1_reg<=0;

else

out1_reg<=out1;

end

always@(posedge clk2 or negedge rst_n)begin

if(!rst_n)

out2<=0;

else

out2<=~sel&~out1;

end

always@(negedge clk2 or negedge rst_n)begin

if(!rst_n)

out2_reg<=0;

else

out2_reg<=out2;

end

assign clk=(out1_reg&clk1)|(out2_reg&clk2);

endmodule

844

844

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?