一、AD7175-8介绍

AD7175-8是一款比较新的ADC器件了,至今还没有找到完整的FPGA的驱动例程,从get新板到最终调试OK也花了快一个月的时间了,终于调试完成。当然,产品介绍在ADI官网上更加详细,我只是简单说几个比较重要,我们经常考虑的几个特点吧:

通道扫描数据速率:50 kSPS

可配置通道数:1-16个

输出数据位宽:24位宽(最高位为符号位,剩下23位就都是数据位了,因此精度是相当高的)

二、调试过程

1.Verilog源代码链接:

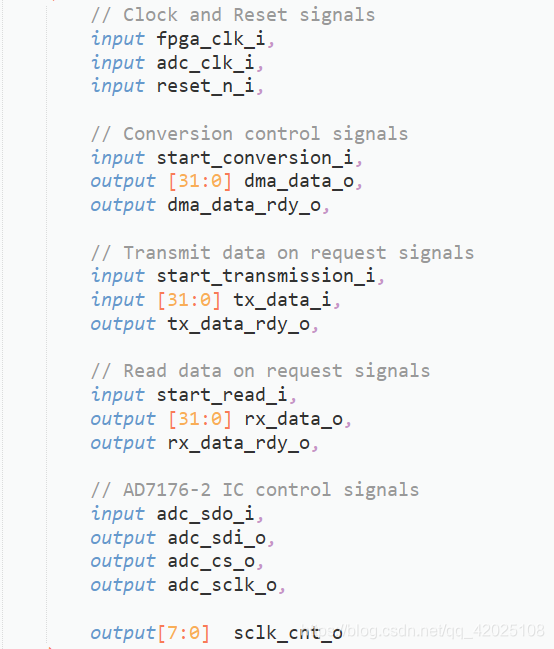

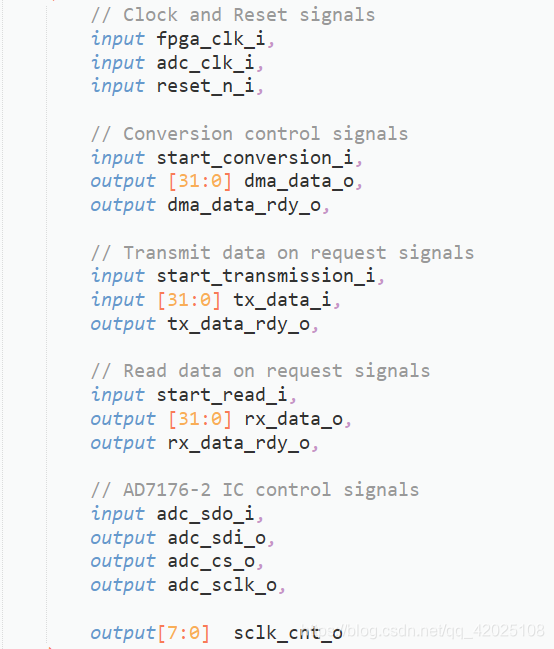

输入输出如下图所示:

2.使用介绍:

fpga_clk_i:外部FPGA模块的主控时钟;

adc_clk_i:将要输出给ADC器件的SCLK的数据传输时钟,即SPI时钟信号线,一般为20MHz;

reset_n_i:复位信号;

start_conversion_i:读取数据寄存器使能,即将该变量置1时,该模块将读取AD7175-8采样到的电压数值;

dma_data_o:该变量32位宽,高8位为对应通道数值,低24位为采样到的电压数值;

dma_data_rdy_o:读取数据寄存器完成信号线,读完后拉高,即表示dma_data_o中存储了电压数值;

start_transmission_i:写寄存器使能,拉高有效;

tx_data_i:寄存器的地址与配置数值;

tx_data_rdy_o:一个寄存器配置完成信号,配置完后拉高,即表示该寄存器配置完成;

start_read_i:读寄存器使能,高有效;

rx_data_o:要读取的寄存器的地址;

rx_data_rdy_o:寄存器读取完成信号,读取完成后拉高,即该数值中为要读取的寄存器地址;

adc_sdo_i:来自ADC器件的SPI输入信号

adc_sdi_o:给ADC器件的SPI输出信号

adc_cs_o:SPI片选信号,低有效

adc_sclk_o:SPI时钟信号

sclk_cnt_o:给顶层输出的当前模块状态判断

3.调试过程:

小编建议,如下调试步骤:

1.读懂上述代码的具体作用与功能;

2.读取ADC器件的ID寄存器,若为3CDX,则表示时序无问题;

3.写入寄存器,再读取写入的寄存器,若两者一致表示寄存器读写完全OK;

4.配置单通道,并完成电压信号的采集

5.配置多通道,完全Ok

小编也是花了一个多月的时间才调试OK,中途肯定会遇到很多莫名其妙的问题,但一定要有耐心解决噢,终于可以松一口气啦!

3257

3257

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?