[sv] region & timeslot_sv timeslot-优快云博客

1. 引言

verilog 语法中的assign always initial 描述语句均是并行发生的,然而计算机的仿真只能按照串行执行,通过串行去模拟硬件的并行行为,试想如果在一个时刻同时发生了多种变化,势必会产生冲突的行为。为了去解决这个问题,仿真器会有一种调度机制,对同一时刻的多种行为按照优先级依次运行。

2. Verilog 的调度机制

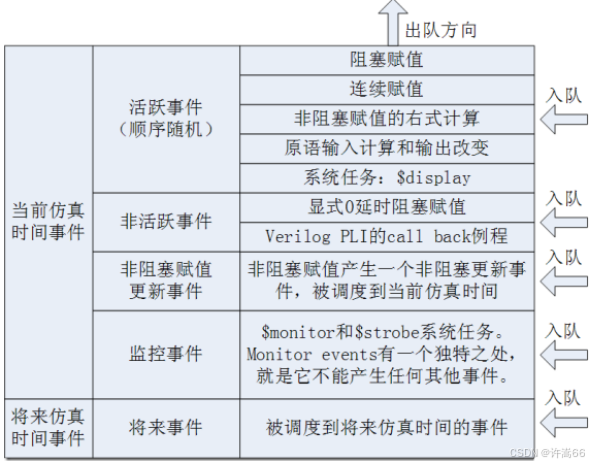

verilog 的仿真调度将同一时刻的事件按照下图方式进行分层,只有等待更高优先级的事件执行结束之后,才可以运行后一等级的事件。

这种仿真调度机制存在设计平台和验证平台竞争的情况,比如在同一个时间片(slot) 100ns处,设计平台存在 prdata <= 200(前一拍为0)的赋值事件, 验证平台存在[ wait(data_reday); rdata = prdata; $display("rdata is %d",rdata); ] 的采样行为

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

903

903

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?