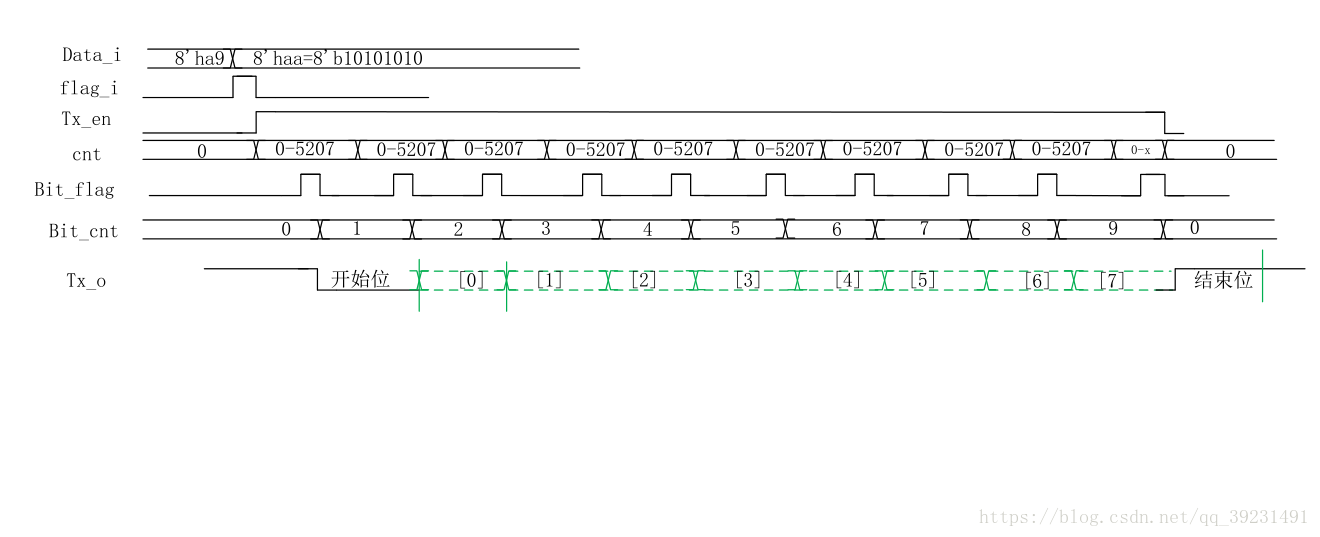

当数据传来的时候会伴随一个标志信号,当识别到tx_en的时候,数据便会被一位位的发送。

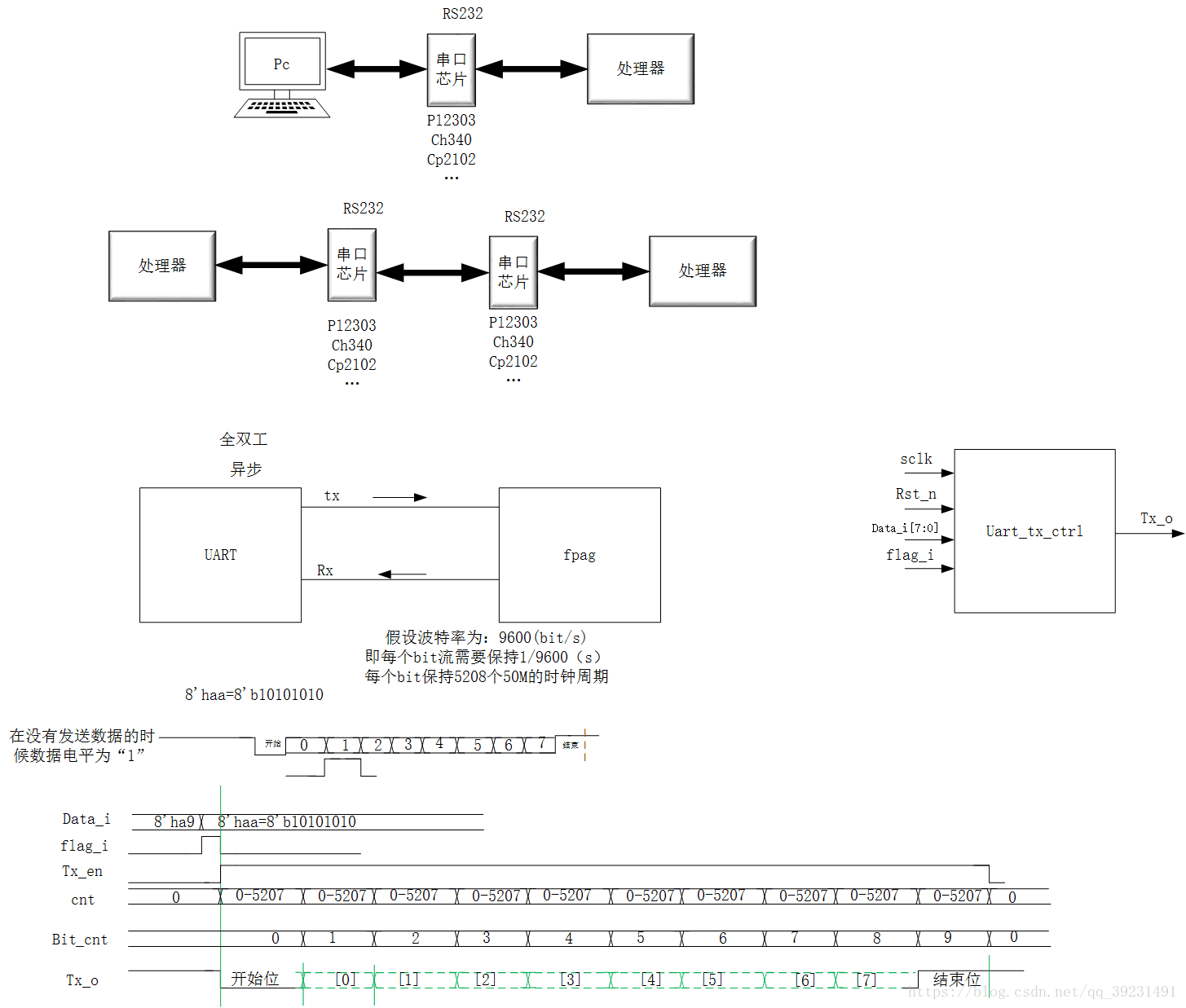

假设传输速率为9600bit/s,系统时钟为50MHZ,则每个bit需保持的时钟周期个数为50M/9600=5207。因为数据在保持的时间内,中间是最稳定的,因此可以记到一半的时候把数据读出来。根据串口的协议,这个串口在无数据传输的时候,tx为高电平,因此复位时为高点平。

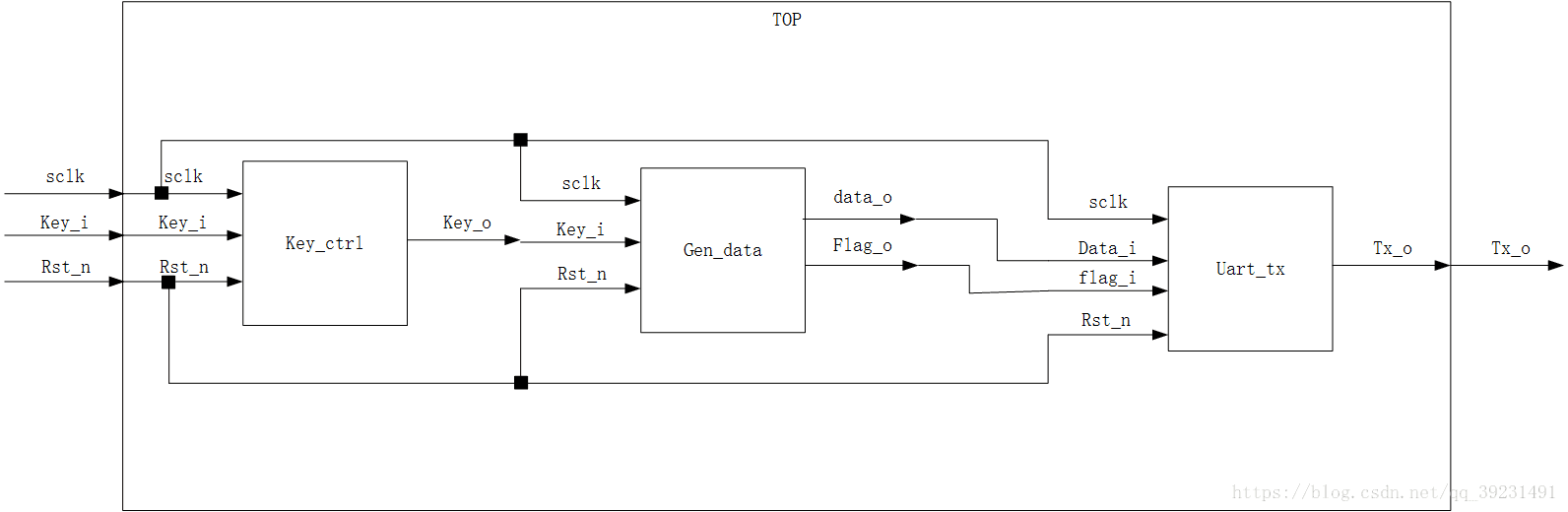

编写一个程序:按键按下去发送一个数据,在电脑端显示出来

module xiaodou(

input wire clk ,

input wire rst_n ,

input wire key,

output reg key_out

);

//按下消抖

reg[18:0] cnt ;

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 19’b0;

else if(key==1)

cnt <= 19’b0;

else if(cnt==500000)

cnt <=500000;

else if(key==0)

cnt <= cnt +19’b1;

always@(posedge clk or negedge rst_n)

该博客介绍了如何使用FPGA实现串口的基本原理,特别是在TX端的数据发送。通过按键触发,每次按键按下时发送一个数据,并在计算机端显示。文中详细阐述了如何处理按键消抖,生成数据并按照串口协议进行位移位发送,以及如何设置合适的时钟周期以匹配9600bps的传输速率。

该博客介绍了如何使用FPGA实现串口的基本原理,特别是在TX端的数据发送。通过按键触发,每次按键按下时发送一个数据,并在计算机端显示。文中详细阐述了如何处理按键消抖,生成数据并按照串口协议进行位移位发送,以及如何设置合适的时钟周期以匹配9600bps的传输速率。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

163

163

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?