分频 :利用系统周期来重新自己定义一个时钟周期

偶数分频:

假如系统周期频率50M,分频后的频率为F,计数器为N

则N_MAX=(50M/f)/2-1

实际编程,要求分频后频率为1M

module fenpin(

input wire clk ,

input wire rst_n ,

output reg clk_n

);

reg[4:0] cnt ;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

cnt <= 0;

else if(cnt==24)

cnt <= 0;

else

cnt <= cnt +1;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

clk_n <= 0;

else if(cnt==24)

clk_n <= ~clk_n;

endmodule

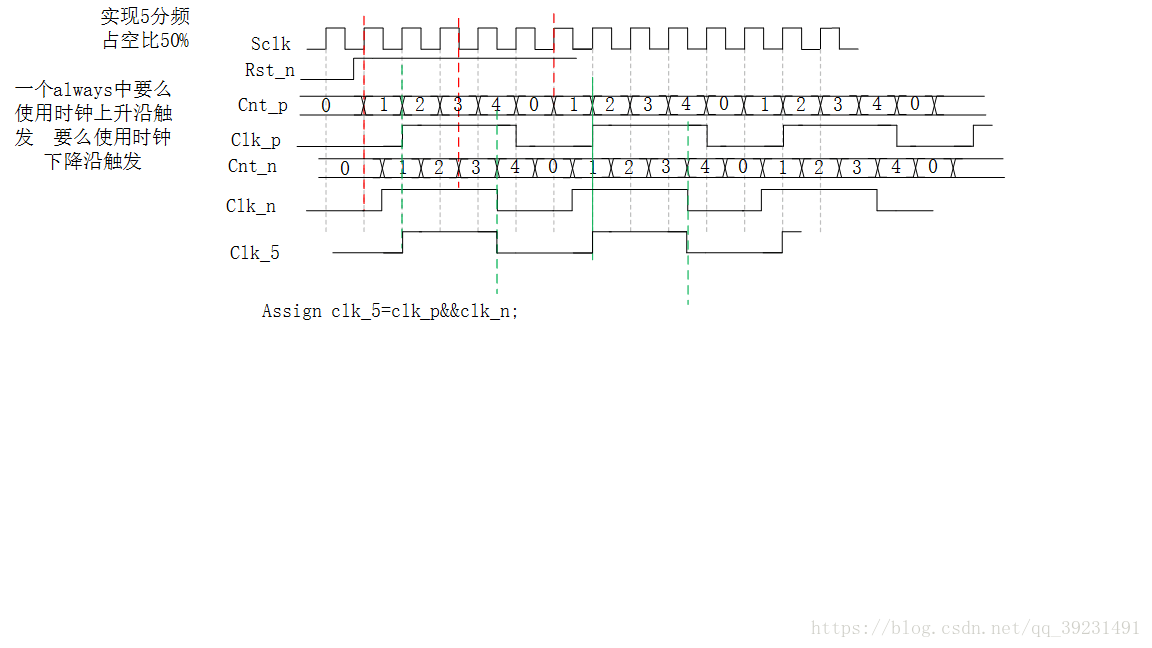

奇数分频,需要用到上升沿和下降沿,使高低电平的占空比不一样,通过两个信号的相与或者相或来实现分频

列如设计一个5分频

先画图分析

程序编写

module fenpin(

input wire clk ,

input wire rst_n ,

output wire clk_N

);

reg[2:0] cnt_p ;

reg[2:0] cnt_n ;

reg clk_p ;

reg clk_n ;

//cnt_p

always@(posedge clk or negedge rst_n)

if(rst_n==0)

cnt

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1714

1714

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?