1.LOCK寄存器的值,毫无疑问,是0xfff,及更大的值

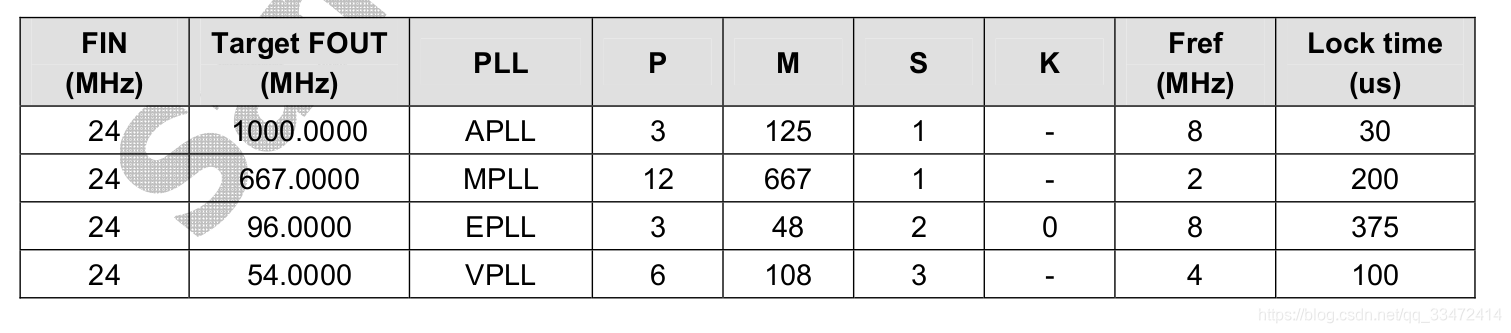

2.CON寄存器的值也是可以确定的,根据下面的图很容易把 P M S的值配出来

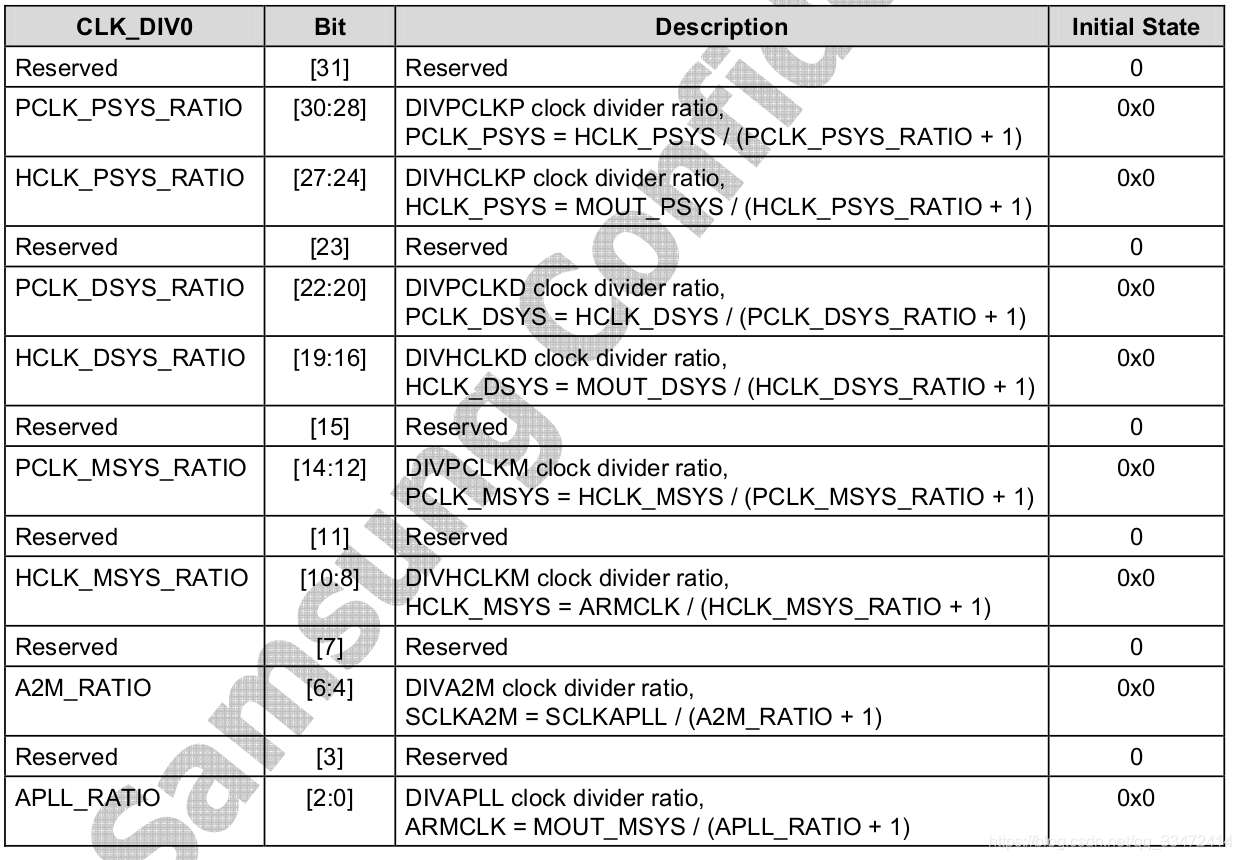

3.DIV分频器就有一些疑惑了,

3.DIV分频器就有一些疑惑了,

朱老师设置值可以是:0x14131440

也可以是:0x14131400

我们看一下这个寄存器:

分析:

分析:

1.MOUT_MSYS 的值可以从两个地方来:0代表APLL倍频出来了的 1代表MPLL倍频出来的,APLL才能倍频到1000M,MPLL只能倍频到667M,ARMCLK需要1000M,那么就只能选0了,然后APLL_RATIO的值也是0.

2.SCLK_APLL的值是1000M,SCLKA2M的值要配置是多少,我们不清楚,有的地方给0,有的地方给4,都可以吧,没有特别要求

3.HCLK_MSYS = 200M ARMCLK = 1000M,HCLK_MSYS_RATIO=4

4.PCLK_MSYS = 100M HCLK_MSYS = 200M,PCLK_MSYS_RATIO = 1

5.HCLK_DSYS = 166M MOUT_DSYS = 667M HCLK_DSYS_RATIO = 3

6.PCLK_DSYS = 86M HCLK_DSYS = 166M PCLK_DSYS_RATIO = 1

7.HCLK_PSYS = 133M MOUT_PSYS是从MPLL来的=667M HCLK_PSYS_RATIO = 4 其实他也可以设置从A2MCLK来

需要MUX寄存器和DIV寄存器可以配合上,下面的MUX寄存器配置我们使用了MPLL,所以就是667M

8.PCLK_PSYS = 66M,HCLK_PSYS = 133M 所以 PCLK_PSYS_RATIO = 1

至于DIV寄存器的配置是需要和MUX寄存器配合起来的

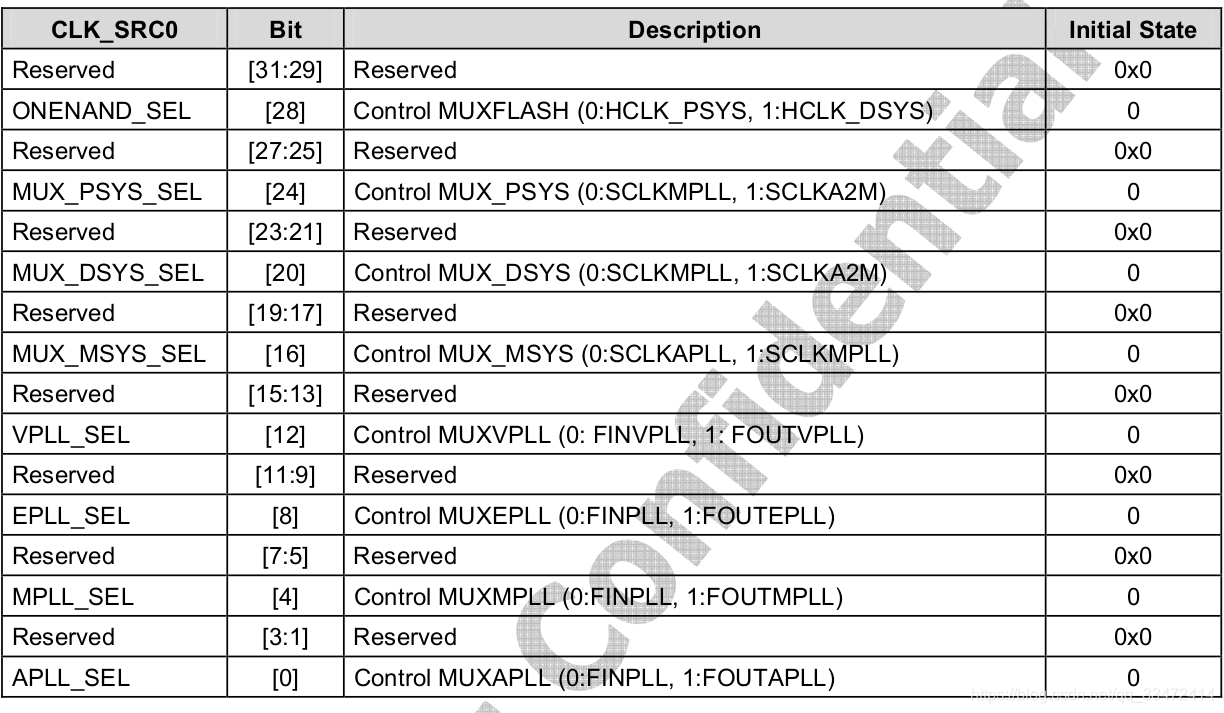

下面我们看MUX寄存器怎么配置:

有人设置了 0x1111

朱老师设置:0x10001111

1.最低的4位:1111,毫无疑问使用PLL,所以设置都是1

2.上面3位,使用PLL所以设置都是0

最高位:SCLK_ONENAND要设置为166/133M,那么0和1都可以,而且DIV_FLASH=1

1对应166M

0对应133M

所以最后总结一下:

所以最后总结一下:

SRC寄存器:0x10001111或者0x1111都是可以的

DIV寄存器:0x14131440 或者0x14131400都是可以的

本文详细解析了嵌入式系统中时钟配置的关键参数,包括LOCK寄存器、CON寄存器和DIV分频器的设置,以及如何通过MUX寄存器配置实现不同频率需求,为读者提供了深入理解嵌入式系统时钟管理的实践指南。

本文详细解析了嵌入式系统中时钟配置的关键参数,包括LOCK寄存器、CON寄存器和DIV分频器的设置,以及如何通过MUX寄存器配置实现不同频率需求,为读者提供了深入理解嵌入式系统时钟管理的实践指南。

4698

4698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?