二选一多路器为数字电路中讲过,如果SEL=1,out=a;如果SEL=0,out=b;

真值表达式如下:

| SEL | out |

| 1 | a |

| 0 | b |

用verilog语言有两种写法:

module mux2(

input SEL,

input a,

input b,

output reg out

);

always @ (*)

if(SEL)

out = a;

else

out = b;

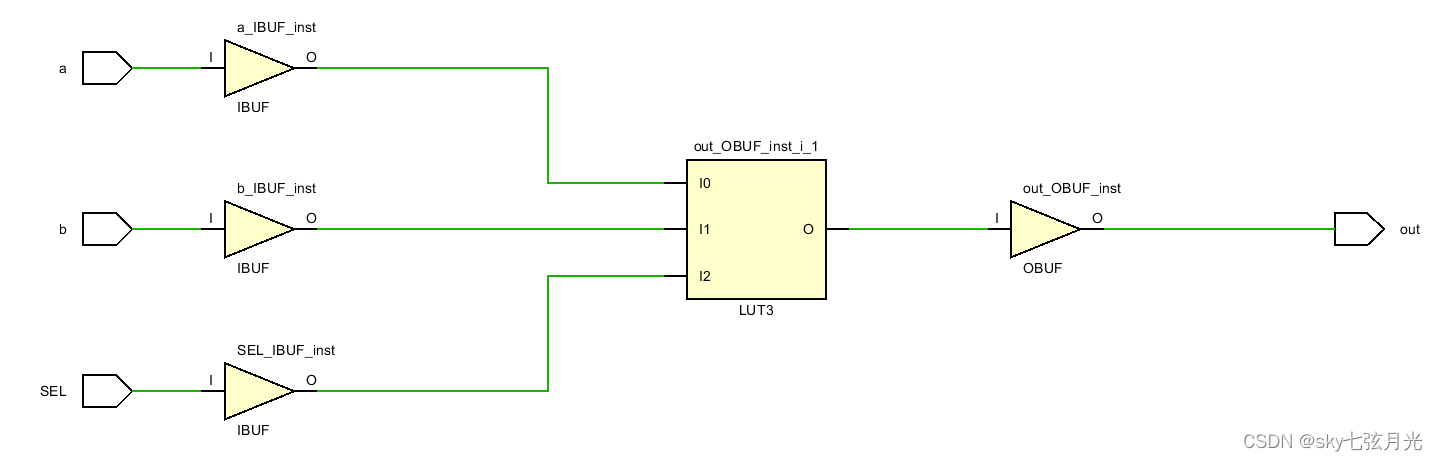

endmoduleRTL视图如下

第二种仿真代码写法如下

module mux2(

input SEL,

input a,

input b,

output out

);

assign out=(SEL==1)?a:b;

endmoduleRTL视图如下:

本文介绍了如何使用Verilog语言设计和实现一个二选一多路器,通过两种不同的代码写法展示了其工作原理。第一种是结构化文本,第二种是直接赋值语句。详细解析了两个代码版本,并提供了它们的RTL视图。适合学习数字电路设计的学生和工程师参考。

本文介绍了如何使用Verilog语言设计和实现一个二选一多路器,通过两种不同的代码写法展示了其工作原理。第一种是结构化文本,第二种是直接赋值语句。详细解析了两个代码版本,并提供了它们的RTL视图。适合学习数字电路设计的学生和工程师参考。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?