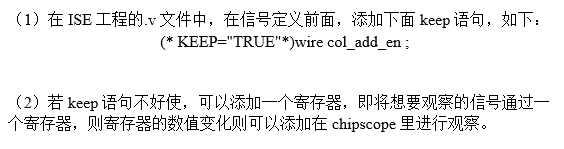

在ISE工程的Verilog文件文件中,在需要保持的观察信号前面,添加

(*KEEP="TRUR"*) 如下所示:

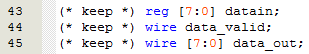

在quartus工程的Verilog文件中,在需要保持的观察信号前面,添加(*KEEP*)。如下所示:

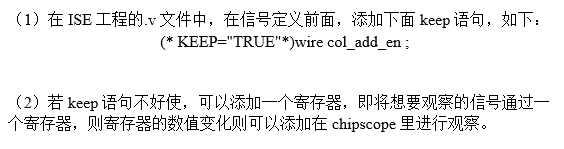

在ISE工程的Verilog文件文件中,在需要保持的观察信号前面,添加

(*KEEP="TRUR"*) 如下所示:

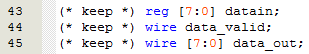

在quartus工程的Verilog文件中,在需要保持的观察信号前面,添加(*KEEP*)。如下所示:

1092

1092

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?