一、8086微处理器内部结构

8086CPU由两部分即指令执行部件( Execution Unit, EU)和总线接口部件(Bus Interface Unit, BIU) 组成,在图中用点画线隔开。指令执行部件主要由算术逻辑运算单元(ALU)、标志寄存器(FR)、 通用寄存器组和EU控制电路4个部件组成,其主要功能是执行指令。总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数来参加EU运算或存放运算结果等。

-

8086组成:

算数逻辑单元ALU、累加器、专用和通用寄存器、指令

寄存器、指令译码器、定时和控制电路。 -

特点:

- 采用并行流水线工作方式

- 对内存空间实行分段管理

- 支持协处理器

-

8086组成(按功能) :

-

总线接口单元( BIU )

构成:

4个段寄存器、一个指令寄存器、-一个与EU通信的内部

暂存器、先入先出队列、总线控制逻辑、一个用于计算

实际物理地址的20位加法器二。

功能:

负责与存储器及/O接口传送消息。 -

执行单元( EU )。

构成:

8个通用寄存器、1个标志寄存器、算数逻辑单元ALU、

EU控制电路。

功能:

EU从指令队列中取出指令代码,将其译码,发出相应的

控制信号。

-

-

总线接口单元与执行单元的配合

- 相互独立

- 并行工作

8086和8088内部结构上的区别

- 相同处:

- 均由BIU和EU组成,两部件并行工作。

- 内部数据总线都是16位。

- 区别:

- 8086指令队列有6字节, 而8088只有4字节。

- 8086指令队列空出2字节则BIU执行一次取指令而8088则是空出1字节便执行一次取指令。

- 8086的外部数据总线是16位,而8088只有8位。

8086的内部寄存器

-

8086内部共14个16位的寄存器。

-

分类:

通用寄存器: 8个

段寄存器: 4个

指令寄存器: 1个

标志寄存器: 1个 -

通用寄存器

包括数据寄存器、地址指针寄存器和变址寄存器。

1 )数据寄存器AX、BX、CX、DX

存放参与运算的数据或运算的结果。

16位寄存器。

高8位、低8位作为独立8位寄存器,AH、AL、BH、BL、CH、CL、 DH、 DL。4个数据寄存器的各自习惯用法:

AX,累加器,字乘法、字除法、字I/O;AL, 字节乘法、

字节除法、字节I/O等。

BX , 基址寄存器,查表转换和间接寻址时存放基址。

CX , 计数寄存器,串操作和循环中的计数器。

DX , 数据寄存器,寄存器间接寻址存放I/O端0号。2 )地址寄存器SP和BP

栈指针寄存器SP :

确定栈顶在内存中的位置;

栈的实际位置由SS、SP共同确定。

基址指针寄存器BP :

存放当前栈段的一个数据区的基地址。 -

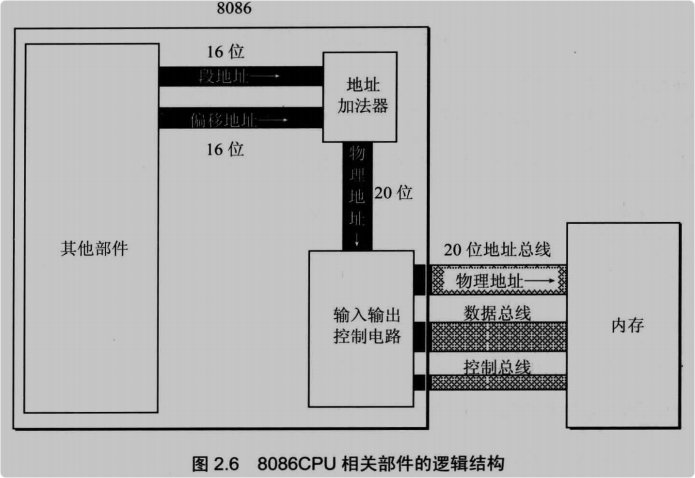

8086CPU给出物理地址的方法

8086CPU有20位地址总线,可以传送20位地址,达到1MB寻址能力。8086CPU 又是16 位结构,在内部一次性处理、 传输、暂时存储的地址为16位。从8086CPU的内部结构来看,如果将地址从内部简单地发出,那么它只能送出16位的地址,表现出的寻址能力只有64KB。

8086CPU采用一种在内部用两个16位地址合成的方法来形成一一个20位的物理地址。8086CPU相关部件的逻辑结构如图2.6所示。“段地址x16(10H)+偏移地址=物理地址”

题型:如果给定一个段地址,仅通过变化偏移地址来进行寻址,最多可定位多少个内存单元?

结论:偏移地址16位,变化范围为0- FFFFH,仅用偏移地址来寻址最多可寻64KB个内存单元。

比如给定段地址1000H,用偏移地址寻址,CPU的寻址范围为:100004~1FFFH。

段寄存器

当8086CPU要访问内存时由这4个段寄存器提供内存单元的段地址 ,这4个寄存器分别为CS、DS、SS、ES。

最小模式下的总线连接示意图

最大模式下的总线连接示意图

两种工作模式的选择方式

-

8086/8088可以在两种工作模式下工作,即最小模式和最大模式。

-

最小模式--即系统中只有8086(或8088)一个微处理器。最小模式是单处理器系统。系统中所需要的控制信号全部由8086(或8088)CPU本身直接提供。

-

最大模式--系统中有两个或两个以上的微处理器,即除了主处理器8086(或8088)以外,还有协处理器(8087算术协处理器或8089 输入/输出协处理器)。最大模式可构成多处理器系统,系统中所需要的控制信号由总线控制器8288提供。

最大模式是相对最小模式而言的。最大模式用在中等规模的或者大型的8086/8088系统中。在最大模式系统中,总是包含有两个或多个微处理器,其中一个主处理器就是8086或者8088,其他的处理器称为协处理器,它们是协助主处理器工作的。

-

-

和8086/8088配合的协处理器有两个,一个是数值运算协处理器8087,一个是输入/输出协处理器8089。

8087是一种专用于数值运算的处理器,它能实现多种类型的数值操作,比如高精度的整数和浮点运算,也可以进行超越函数(如三角函数、对数函数)的计算。

-

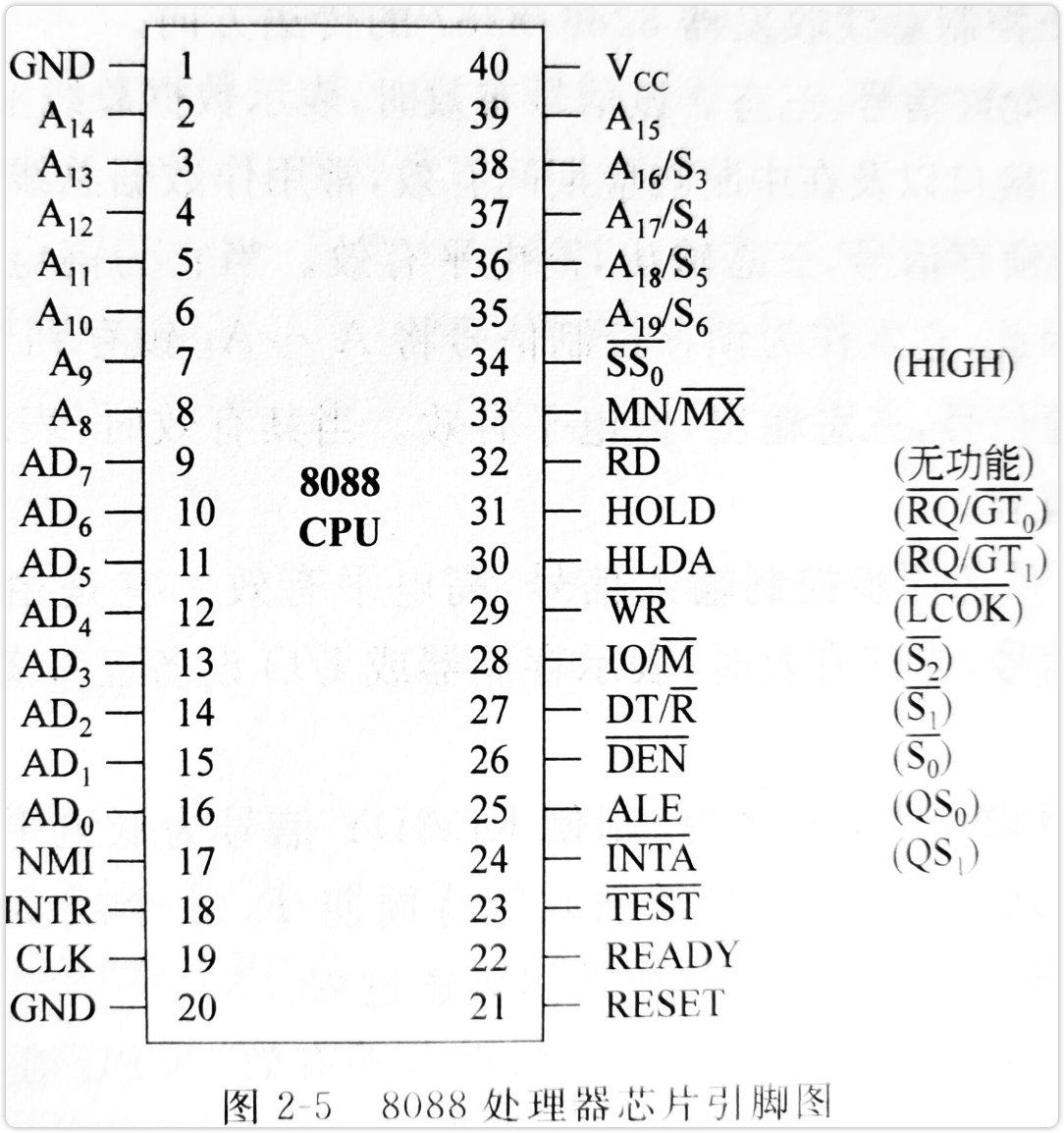

CPU工作模式的选择是由硬件决定的,将8086/8088的第33号引脚接地,则工作于最大模式,第33号引脚接高电平,则工作于最小模式。8086/8088CPU有8条引腿(第24号~31号)在两种不同工作模式中具有不同的功能。

-

8088是工作在最小还是最大模式由MN/ MX ‾ \overline{\text{MX}} MX引线的状态决定。

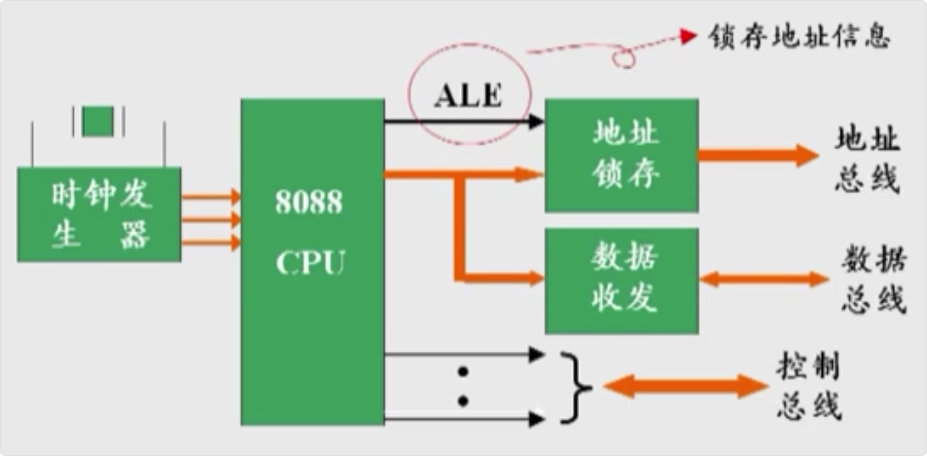

- 8086/8088最小模式的典型配置 当8086/8088的第33引脚MN/ MX ‾ \overline{\text{MX}} MX接高电平(或直接接+5V)时,系统工作于最小模式,即单处理器模式 配套的寄存器8284A为时钟发生器,8282为地址锁存器,8286为数据总线收/发器。

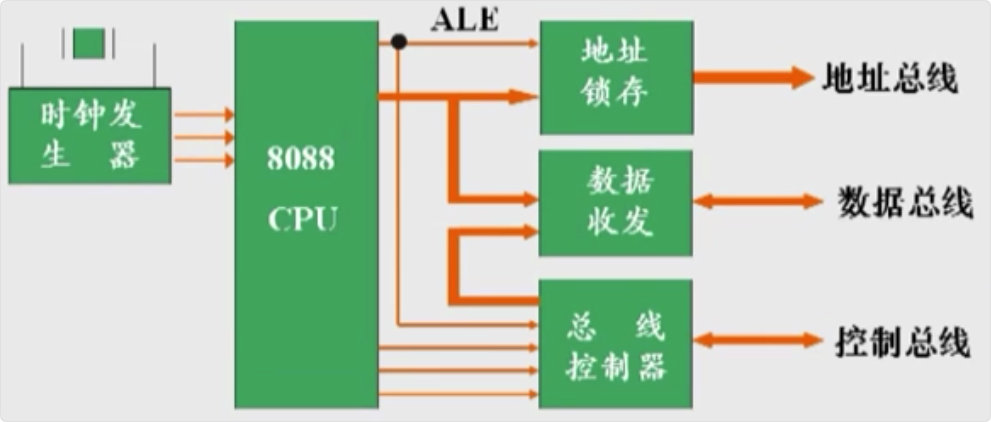

- 8086/8088最大模式的典型配置 当8086/8088的第33引脚MN/ MX ‾ \overline{\text{MX}} MX接低电平(或直接接地)时,系统工作于最大模式, 即多处理器模式 8288为总线控制器

8088处理器的外部引脚及其功能

- 8088和8086

- 8088的最大和最小两种工作模式可以通过在MN/ MX ‾ \overline{\text{MX}} MX输入引脚加上不同的电平来进行选择。当MN/ MX ‾ \overline{\text{MX}} MX=1时,8088工作在最小模式,此时,构成的微型机中只包括一个8088处理器,且系统总线由8088的引线直接引出形成;当MN/ MX ‾ \overline{\text{MX}} MX=0时,8088工作在最大模式,在此模式下,构成的微型计算机中除了有8088 CPU之外,还可以接另外的处理器(如8087数字协处理器)构成多微处理器系统。在最大模式下,微机的系统总线要由8088和总线控制器(8288)共同形成。

8088CPU最小模式下的主要引脚信号

- 8088最小模式下的主要引脚信号 → 4组

- 完成一次访问内存或接口所需要的主要信号

- 与外部同步控制信号

- 中断请求和响应信号

- 总线保持和响应信号

最小模式系统中8086CPU的总线周期

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-TmfM1YbG-1600850186035)(https://i.loli.net/2020/08/22/yc7CZUaTR6XvKfA.png)]](https://i-blog.csdnimg.cn/blog_migrate/5bb937c4c233324f8cedeaf95d80e16a.png#pic_center)

3459

3459

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?