基于电压模式和电流模式逻辑的四进制逻辑电路设计

摘要

在VLSI技术中,设计者主要关注器件所需的面积和性能。在VLSI设计中,由于芯片密度持续增加、 CMOS电路尺寸不断缩小以及电路工作频率的提高,功耗成为一个主要问题。基于这些参数,逻辑 电路采用四进制电压模式逻辑和四进制电流模式逻辑进行设计。与二进制相比,四进制电压模式逻辑所需的功耗减少了51.78%。在晶体管数量方面,四进制电压模式逻辑所需的面积是二进制的3倍。

虽然四进制电压模式电路相比四进制电流模式电路需要更大的面积,但其功耗低于四进制电流模式 电路所需的功耗。

关键词

多值逻辑(MVL),四进制电压模式,四进制电流模式,最小值,最大值

引言

过去几十年中,集成电路产业呈现出指数增长趋势。随着单位面积晶体管数量的增加,该 产业面临了一些新的问题。为了维持这一增长,产业必须解决的主要问题是互连(包括片 上和芯片之间)以及这些互连的布线。用于这些互连的硅面积可能大于用于有源逻辑元件 的面积。

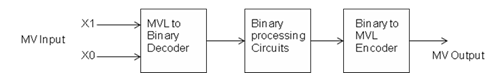

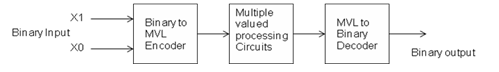

使用具有超过两个逻辑电平的电路已被提出作为解决这些互连问题的方法。多值逻辑( MVL)电路在减少超大规模集成(VLSI)中互连布线和功能单元所占用的芯片面积方面 具有潜力。将具有超过两个电平的信号应用于单根导线,可在相同数据范围内减少导线数 量,这种减少进而降低了所需集成电路引脚的数量。随着互连长度和所用导线数量的减少, 在不增加总硅面积的情况下,任意两根导线之间的间距增大,从而降低了接触点和互连的 电阻与电容,互连延迟可显著降低。从MVL逻辑角度来看,有两种基本方案:第一种方 案接受多值输入并产生多值输出[1,2],其内部处理为二进制。当多值逻辑用于降低互连复 杂性时,该方案非常有用。另一种方案接受二进制输入并产生二进制输出,其内部处理采 用多值电路,如图1和图2所示。

在任何数制系统中,基数越小,表示给定数量所需的数字就越多。

表示范围为 N 所需的数由 N = R^d 给出

(1)

其中 R 是基数,d 是所需的数字位数,必要时向上取整到下一个最高的整数值。

如果假设系统硬件的成本或复杂度C与数字容量R × d成正比,那么

C = k(R × d) (2)

= k [R log N / log R]

其中k为某个常数。对R求导可知,当成本C最小时,R应等于e = 2.718。由于在实际中R必 须为整数,通过比较可得R = 3 (三进制)比R = 2(二进制)更经济。

或者,假设处理一个信号线的电路成本和复杂度C与基数无关且保持不变,则系统总成本 C仅与d成正比。在这种情况下

C = k × d = k [ log N / log R] (3)

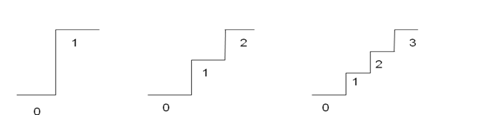

随着基数R的增加,成本逐渐降低[1] 。在基于2的幂的基数中,基于4的系统显示出相当大 的潜力。二进制、三进制和四进制逻辑的逻辑电平如图3所示。

多值逻辑,四进制电路可根据电路的复杂性和操作以电压和电流模式实现。

电压模式

:在电压模式中,信号通过电压电平进行传输。电压模式电路通过电压电平传递 信息。电压模式设计的最大允许基数由电源电压决定。

电流模式

:1983年提出的电流模式CMOS MVL电路被证明符合电路超大规模集成电路 (VLSI)的要求。根据不同的逻辑电平值,考虑使用特定的参考电流单元来确定[3]。

本文的第一部分介绍了四进制逻辑。第二部分介绍了四进制电压和电流模式下的逻辑电路 设计,最后一部分描述了结果与结论。

2. 四进制逻辑

四进制是基数为4的数字系统。它使用数字0、1、2和3来表示逻辑电平。它能够用规范表示[4]表示任 何实数。

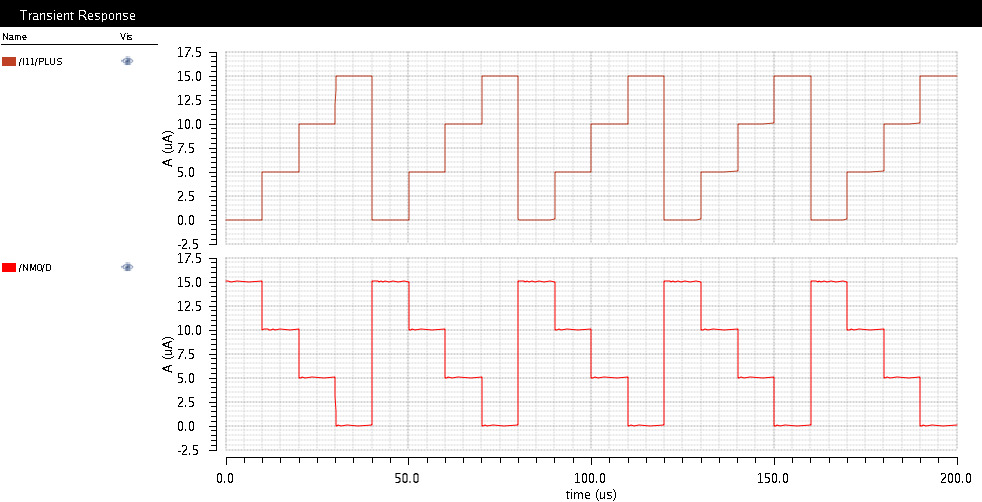

在电流模式下,电平根据参考电流确定。所提出的电路设计的参考电流为5微安,四进制电平依赖于 此,如表1所示。

表1. 四进制电流逻辑电平

| 逻辑电平 | 电流(微安) |

|---|---|

| 0 | 0 uA |

| 1 | 5 uA |

| 2 | 10 微安 |

| 3 | 15 微安 |

在电压模式下,电平根据电压确定,四进制电平取决于此,如表2所示。

表2. 四进制电压逻辑电平

| 逻辑电平 | 电压 |

|---|---|

| 0 | 0 V |

| 1 | 1 V |

| 2 | 2 V |

| 3 | 3 V |

3. 四值逻辑算子的设计

3.1 使用电压模式设计逻辑电路

3.1.1 四值反相器

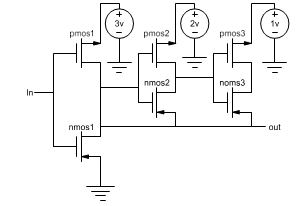

四值反相器由6个晶体管组成,包括三个NMOS和三个PMOS,如图4所示。这些NMOS和 PMOS工作在不同的阈值电压下。当输入值为0伏特时,PMOS1导通,使输出变为3 V,而 NMOS1、NMOS2和NMOS3截止,切断其余路径。当输入值为1 V时,PMOS1截止,而 NMOS2导通,使输出变为2 V。当输入值为2 V时,PMOS2截止,而NMOS3导通,从而 使输出变为1 V。只有当输入值为3 V时,PMOS3截止且NMOS1将输出拉低至零[5]。

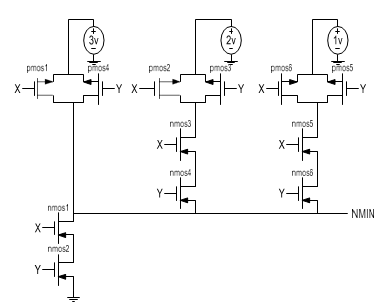

3.1.2 四值MIN门的设计

在四进制逻辑中,NMIN门相当于二值逻辑中的NAND门,MIN门相当于二值逻辑中的与门。

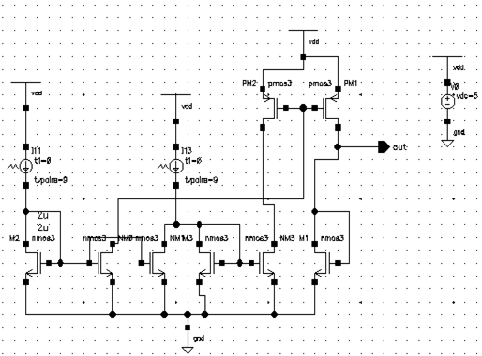

在二值AND中,只有当两个输入值均为高电平时输出才为高电平,其他所有情况输出均为低电 平。但在MIN门中,输出被设置为输入值中的最小值。NMIN门的功能则相反,即NMIN是 MIN门的非。因此,反相器与MIN门的组合构成NMIN门,或者在NMIN门的输出端加上反相 器即可构成MIN门。NMIN门的电路图[5] 如图5所示。

3.1.3 四进制最大门的设计

在四进制逻辑中,NMAX门相当于二值逻辑中的或非门,最大门相当于二进制中的或门。在二进制或门中, 只要有一个输入值为高电平,则输出为高电平,其他所有情况输出为低电平。但在最大门中,输出被设置 为输入值中的最大值。

与NMAX门功能相反的是MAX门,即NMAX是MAX门的非。因此,反相器与MAX门的组合构成 NMAX门,或者通过在NMAX门的输出端连接反相器形成MAX门 [5] 。NMAX门的电路图如图6所示。

3.2 使用电流模式设计逻辑电路

3.2.1 互补算子

互补算子充当基本反相器电路。无论输入为何值,在电路输出端均得到取反结果。它基本定义为

(4)

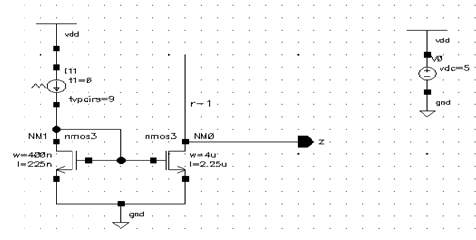

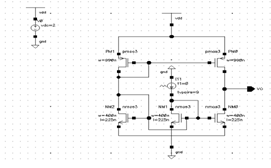

此处输入为x,输出也为x。互补算子的电路图如图7所示。

表3. 反相器真值表

| In | 0 | 1 | 2 | 3 |

|---|---|---|---|---|

| Out | 3 | 2 | 1 | 0 |

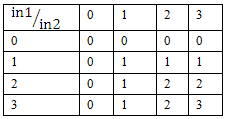

3.2.2 最小门的设计

在电流模式下,最小门[6]充当与门,接收不同的输入值,并输出其中的最小值作为输出信号。假设输入为(x1, x2, x3 …xn),则输出结果为其中的最小值。

(5)

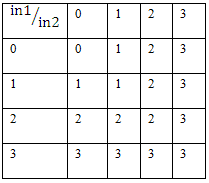

表4:最小门的真值表

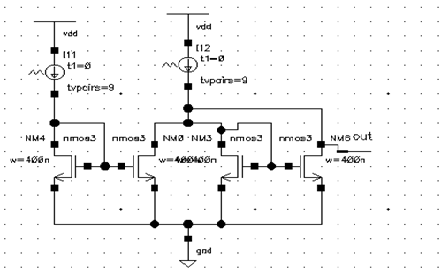

3.2.3 最大门的设计

在电流模式最大门中,[6]充当或门,接收不同的输入值,并输出其中的最大值作为输出信号。假设输入为(x1, x2, x3 …xn),则输出为其中的最大值。最大门的电路图如图9所示。

(6)

表5. 最大门真值表

3.2.4 电流比较器设计

在提出的电流比较器电路中,输入二极管连接的NMOS‐PMOS晶体管对产生阈值电流。该 参考电流被镜像为输出Ith,输入电流被镜像为输出Iin。当输入电流小于阈值电流时,比较器电路的输出为逻辑高电平(输出节点与电源具有相同电位);当输入电流大于阈值电流时,比较器电路的输出为逻辑低电平(输出节点与地具有相同电压)。若需要,可通过 PMOS晶体管镜像施加输入电流,NMOS施加阈值电流,以产生输出电压的反相版本[7]。

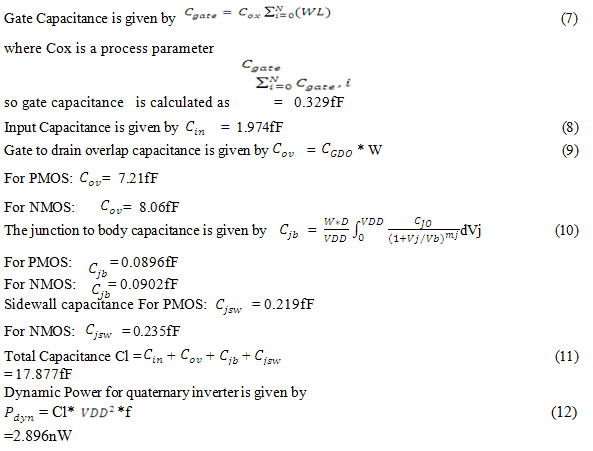

3.3 四元反相器的电容估算

任何电路的输入电容都可以通过简单地计算连接到特定输入信号的所有栅极电容之和来近似。

4. 结果与结论

提出的电路通过使用Cadence工具在0.18微米技术下进行提取,仿真结果如下:

表6. 四进制电压模式电路平均功耗分析

| 电路类型 | 二进制[10] | 四进制 |

|---|---|---|

| 反相器 | 0.1 nw | 27.1 pw |

| Min | 38.9 μw | 2.1 μw |

| Max | 67.1 μw | 0.4 μw |

| Nmin | 11.5 nw | 0.1 nw |

| Nmax | 67.1 μw | 0.28 μw |

表7. 四进制电压模式电路的面积分析

| 电路类型 | 二进制(晶体管数量)[10] | 四进制(晶体管数量) |

|---|---|---|

| 反相器 | 2 | 6 |

| Min | 6 | 18 |

| Max | 6 | 18 |

| Nmin | 4 | 12 |

| Nmax | 4 | 12 |

表8. 四元电流模式电路的面积分析

| 门电路 | 传统的[7] | 提出 | 二进制 |

|---|---|---|---|

| Min | 7[7] | 4 | 6 |

| Max | 8[7] | 8 | 6 |

| 面积(晶体管数量) |

表9. 四进制电流模式电路平均功耗分析

| 门电路 | 传统的[7] | 提出 | 二进制 |

|---|---|---|---|

| Min | 0.23 | 0.02 | 0.03 |

| Max | 0.29 | 0.03 | 0.06 |

| 平均功耗(毫瓦) |

基于功耗和晶体管数量,对二进制、四进制电压模式电路进行了比较分析。如表6所示, 四进制电压模式逻辑所需的功耗比二进制低51.78%。如表7所示,四进制电压模式逻辑在 晶体管数量方面的面积比二进制多3倍。基于功耗和面积,对提出的四进制电流模式电路、 传统电路和二进制电路进行了比较分析。如表8所示,提出的四进制电流模式电路的面积 小于传统电路和二进制电路。提出的四进制电流模式电路所需的功耗也低于传统电路和二 进制电路。虽然四进制电压模式电路所需的面积大于四进制电流模式电路,但四进制电压 模式电路所需的功耗小于四进制电流模式电路。

1798

1798

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?