用于超声治疗CMUT阵列的定制集成电路设计

引言

超声系统技术在过去几十年中发展迅速,具有广泛的应用,可用于实时三维成像和治疗性医疗用途。微机电系统(MeMS)和微电子学技术的进步使得微加工器件与集成电路(Ic)相结合,为日常生活中的医学应用带来了巨大进展。MEMS技术在微型结构、传感器、执行器和微电子学方面取得了商业成功,在医学应用中需求巨大。其中一些应用涉及医学成像(超声波检查)和治疗。超声成像和治疗正成为现代医学技术中的重要工具,以实现高分辨率和高灵敏度系统。

这些技术可用于利用声波和回波获取患者体内的三维医学成像(彩色或黑白图像),或用于治疗应用,例如检测癌细胞、通过 firing它们来清除体内的癌细胞、粉碎肾结石等。超声技术还可用于结构和产品的无损检测、物体和障碍物的探测以及它们之间距离的测量、清洗、混合以及加速化学过程。

医学成像应用由发射和接收系统组成。发射器发出声波,声波反射回接收器后形成图像。声波通过超声换能器发送。这些换能器在受到电信号激励后会产生机械响应。在成像应用中,反射的声波使换能器产生机械位移,并生成电信号,进而形成图像。另一方面,在治疗应用中的超声换能器通过高能信号激发。这些信号在穿过组织进入体内时是无害的。在近期的临床应用中,高强度聚焦超声(hIFU)系统使用基于 PZT‐8和PZT‐4(压电材料)的超声换能器,频率范围为1–4兆赫(ebbini等,1999)。

在传统超声系统中,换能器阵列与电子仪器通过多芯物理电缆分离。然而,连接电缆使系统过于庞大,并由于长电缆的电容导致超声三维成像应用中的接收灵敏度下降。相控阵超声系统(成像或治疗)的接口电子器件利用超声换能器阵列在被 fired或成像的区域内实现聚焦波束的偏转,从而消除笨重的电缆。在现有类型的超声换能器中,cMUT阵元(电容式微加工超声换能器)因其与压电对应器件相比不存在自热效应而受到特别关注。因此,将cMUT阵元与前端电子器件集成可用于高强度聚焦超声(hIFU)等高功率和连续波(cW)应用。尽管已有许多研究致力于设计和实现用于医学治疗应用的超声换能器,但针对c MUT治疗应用所需配合使用的接口电子器件性能提升的研究仍较少。本文介绍了一种用于超声治疗应用的 cMUT换能器的灵活且完全可控的波束形成器接口电子器件的设计。

系统架构

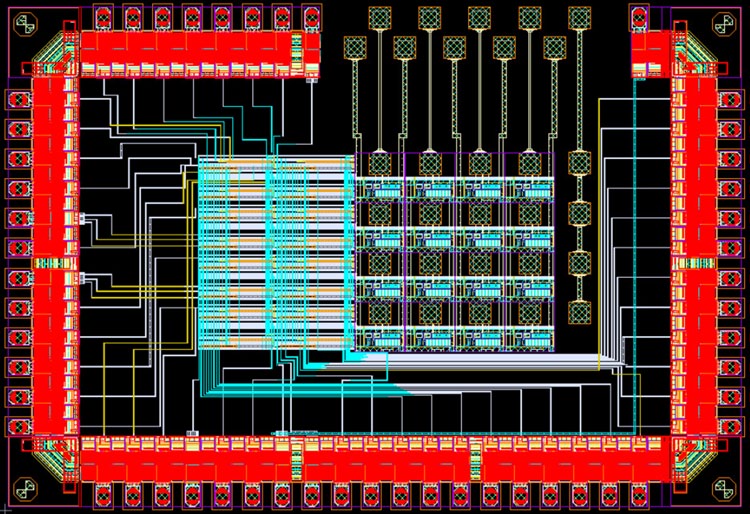

所提出的超声治疗集成电路包含多种模块,这些模块被实现在同一芯片上。对于每个cMUT单元,均配置一个完整的模块,该模块包含所有设计的电路,因此芯片的最终尺寸完全取决于cMUT阵元的数量。图1展示了专用集成电路设计的顶层设计视图,其中不同的模块已被设计并实现。所设计集成电路的框图如图2所示。该集成电路采用4 × 4个cMUT单元换能器阵列用于治疗应用。该集成电路由16个发射波束成形器组成,对应16个超声换能器。该系统为每个16个 cMUT元件提供一个8位移位寄存器(SIPO)、一个8位比较器、一个单稳态电路、一个带有5位数字控制延迟元件(DCDE)的数控振荡器(DcO)、一个频率下变频(FDc)电路、一个使用厚氧化物晶体管(ThKOX)的45伏脉冲电路以及组合逻辑(图2)。高压(HV)模块的输出应通过芯片外引线焊盘逐个连接到cMUT阵元。每当需要对任意点进行聚焦时,需通过现场可编程门阵列(FPGA)串行地将聚焦延迟值加载到移位寄存器中。同时,FPGA全局控制波束成形模块的选择线。

如图3所示,波束成形电路包含三个主要模块。第一个模块由8位移位寄存器和8位比较器组成,用于生成延迟信息以选择cMUT阵元。如果我们希望用单脉冲激励cMUT单元,应激活第一条线路,该线路包含一个单稳态触发器电路。根据cMUT单元的工作频率,可通过外部电流源或片上数字到模拟转换器(DAC)调节信号的脉冲宽度。

在某些情况下,我们希望使用脉冲串而不是单脉冲来激励cMUT阵元。这类信号在彩色多普勒成像应用中也有用处(athanasopoulos等人 2011)。此外,我们设计的波束成形器虽然考虑了治疗应用,但也可用作三维彩色多普勒成像应用的发射部分。对于我们的应用,需要频率范围为1–10 MHz的可调频率脉冲串,因此我们决定采用带有数字控制延迟单元和频率下变频模块的数字控制振荡器。最后,所产生的低压(LV)信号(无论是单脉冲还是脉冲串)的幅度被提升至45伏特。实际上,高压信号的幅度可以通过外部线路进行控制。

电容式微机械超声换能器选择方法

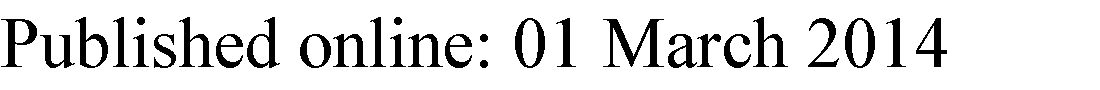

该集成电路从现场可编程门阵列获取延迟信息,并生成具有可调脉冲宽度的高压单脉冲或具有任意频率的高压脉冲串。对于cMUT单元的选择,可以使用移位寄存器和比较器。在生成每个新的 firing波束成形之前,现场可编程门阵列串行地将8位聚焦延迟值通过集成电路中不同线路的数据端口载入每个移位寄存器。由于每行包含四个cMUT阵元,因此将四个移位寄存器以串联方式依次考虑。图4展示了一位动态移位寄存器,该寄存器具有两个输入时钟、一个数据输入和一条复位线。每个寄存器包含两个传输门(T‐Gate)用于存储发射延迟信息的一位移位寄存器。当所有8位移位寄存器从FPGA接收到延迟信息后,它们将以并行模式将数据传输给8位比较器。8位比较器会比较其输入端口的数据,如果两者相同,则向下一阶段发送使能信号。图5展示了4位伪nMOS比较器的原理图(Wang等,2003)。尽管这类比较器的栅极会引入直流电流,但它们速度快且在芯片上占用面积小。在我们设计的集成电路中,共有16个比较器。每个比较器有两个输入端口,其中一个端口具有八个引脚,用于从移位寄存器接收延迟信息,另一个具有八个引脚的端口用于获取全局计数器的信息。现场可编程门阵列提供8位全局计数器的值。在每个波束成形电路中,当移位寄存器的值与全局计数器的值相同时,比较器生成使能信号,其输出变为高电平。将比较器的输出连接到缓冲门可提高电路的可靠性,并使输出电压在全范围内摆动,但同时会增加集成电路的面积。

图6显示了在200 MHz时钟频率下电容式微机械超声换能器选择电路的仿真结果。现场可编程门阵列生成的延迟信息的脉冲宽度(PW)应等于时钟频率的周期。

具有可调脉冲宽度的单脉冲发生器

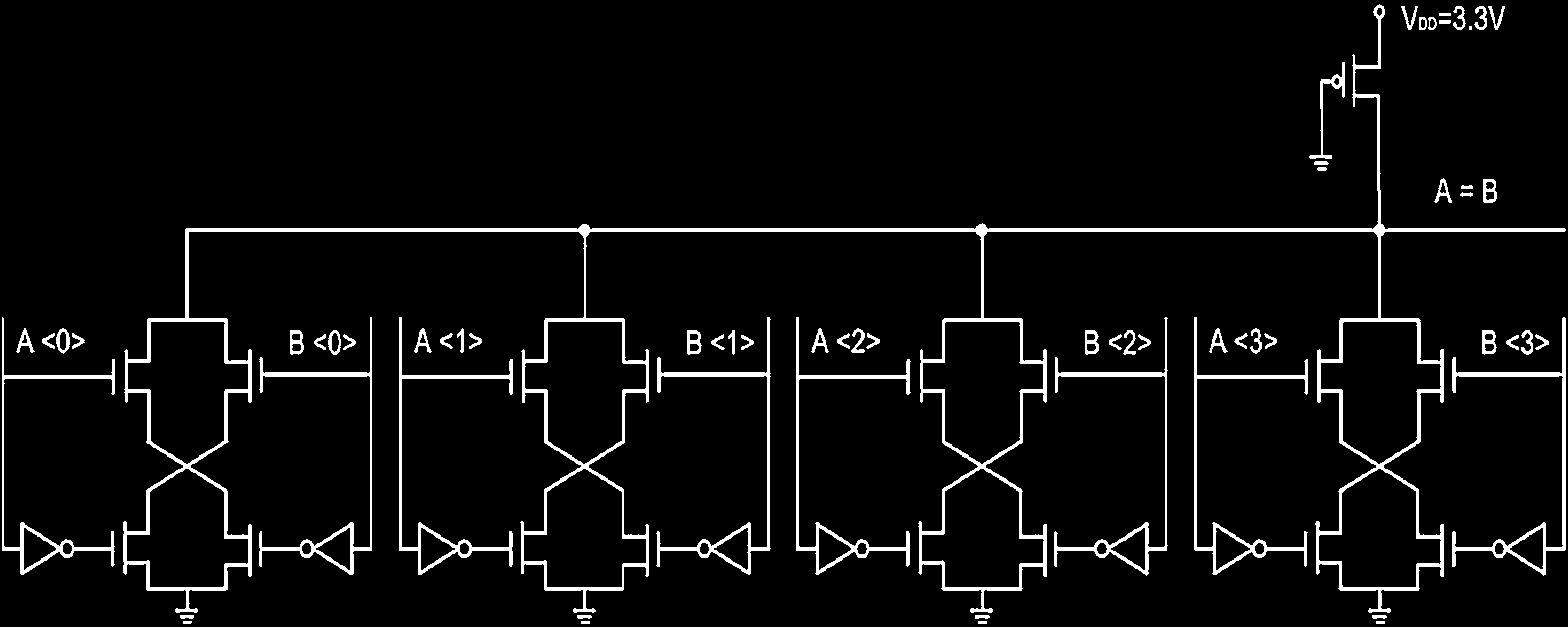

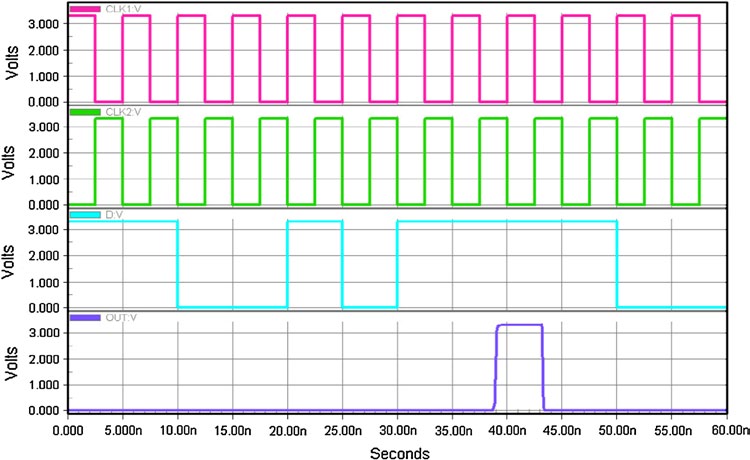

由于不同的cMUT阵元具有不同的工作频率,我们需要调整输出信号的脉冲宽度(Wygant等人,2009)。在我们提出的接口电子设备中,为了调节脉冲宽度,使用了单稳态电路。图7展示了所提出的单稳态电路。在我们设计的单稳态电路中,通过M0晶体管控制脉冲的宽度。通过控制流经电容c的电流(ISeT)fl,我们可以调节输出脉冲的宽度。在我们的设计中,输出信号的脉冲宽度与ISeT/c之比成正比,这意味着通过增大ISeT,可以生成具有较大脉冲宽度的信号。电容c被固定为fi2皮法,因此脉冲宽度仅与ISeT成正比。在我们设计的用于为5兆赫超声换能器生成信号的单稳态电路中,需要将ISeT调整到约75 μa。

图8显示了所设计的单稳态电路的仿真结果。显然,当我们将ISeT从70增加到78 μa时,输出脉冲的宽度从20至650纳秒发生变化。

可控频率脉冲串发生器

如果想使用单脉冲激励cMUT阵元,我们需要选择脉冲生成的第一模式。在对于其他情况,例如治疗或3D彩色多普勒成像应用,我们更倾向于使用脉冲串而非单脉冲来激励cMUT阵元。生成的脉冲串的频率应根据cMUT阵元的工作频率进行选择。由于可以设计出工作频率范围在1–10 MHz内的各种cMUT阵元,因此我们尝试设计一种具有优良频率分辨率的灵活脉冲序列生成电路。

提出的带DcDe电路的数控振荡器

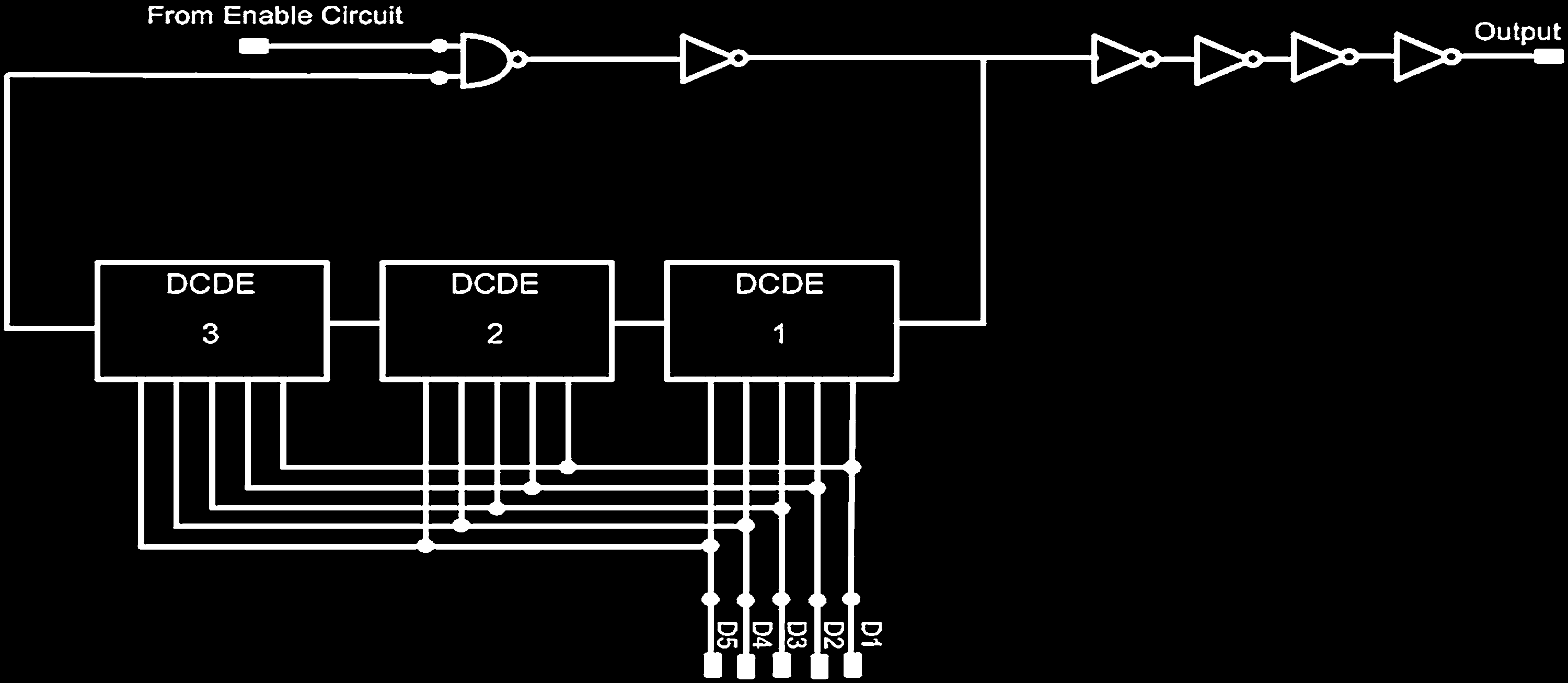

数字控制延迟单元(DcDes)在集成电路中具有多种应用。在我们的治疗应用中,我们希望使用脉冲序列而非单脉冲来激励ficMUT阵元。对于脉冲序列生成模式,可采用数控振荡器(DcOs)与数字控制延迟单元(DcDes)的组合。图9展示了提出的DcO–DcDe电路。DcO作为数字控制振荡器电路,在每个周期改变输出状态,并生成具有50%占空比的脉冲串。所生成脉冲串的脉冲宽度、周期和频率完全取决于设计的可变元件。实际上,脉冲串的周期是通过数字控制延迟元件(DcDes)产生的延迟时间的两倍。显然,如果我们想要控制脉冲串的周期,则需要控制可变延迟元件的延迟值。此处使用了三个DcDe来控制脉冲串的频率。设计的数字控制延迟元件可通过现场可编程门阵列(FPGA)使用5位数字输入向量进行控制,因此我们共有2^5= 32种不同频率的脉冲串。

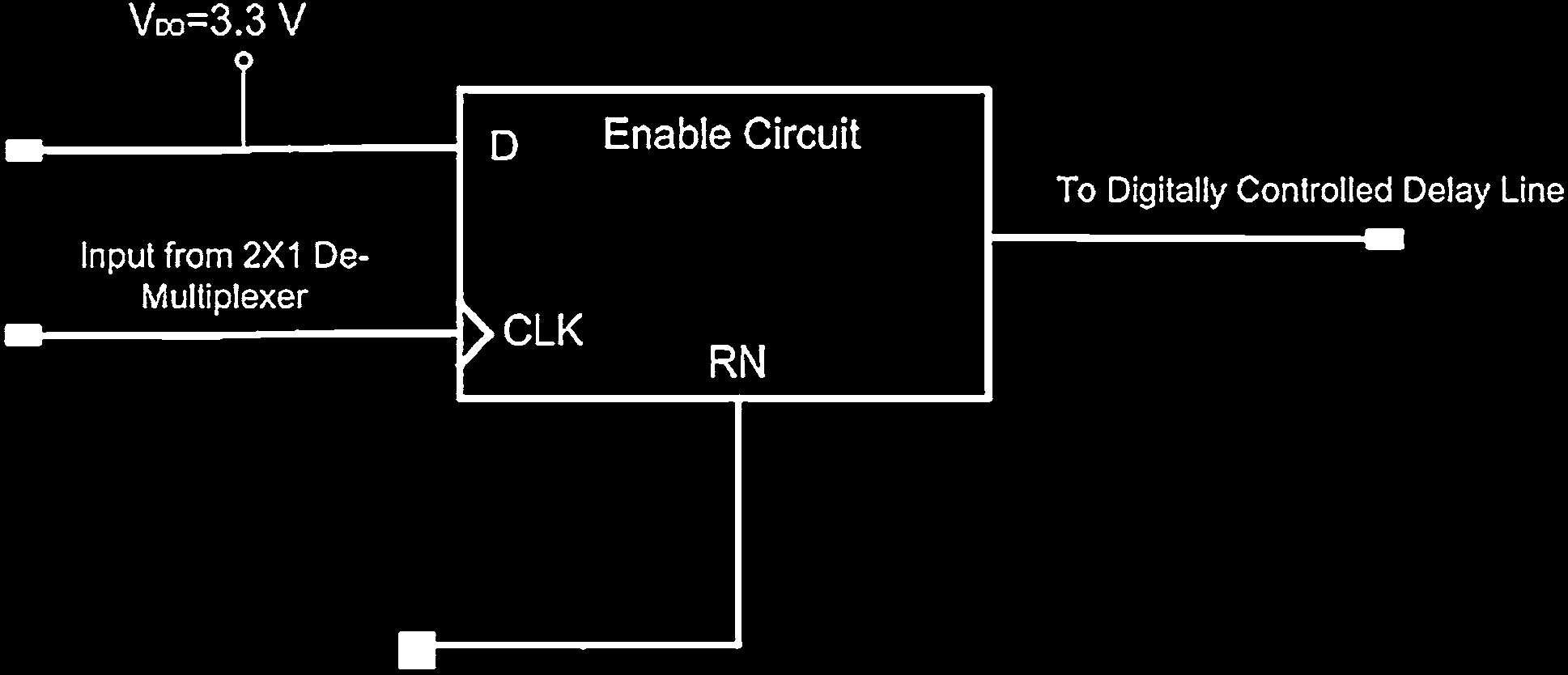

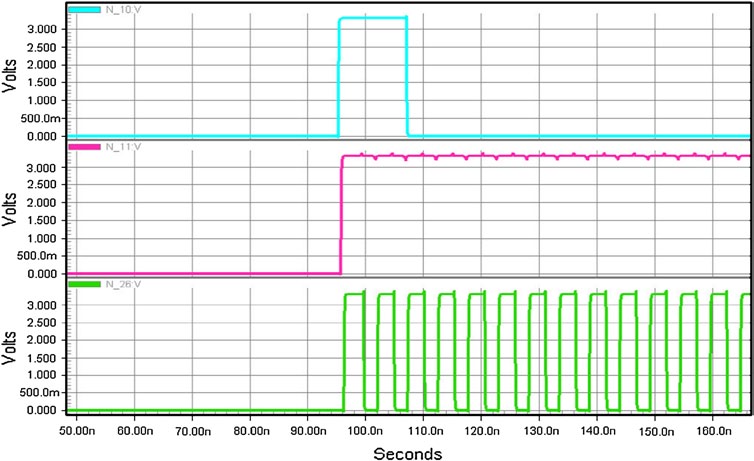

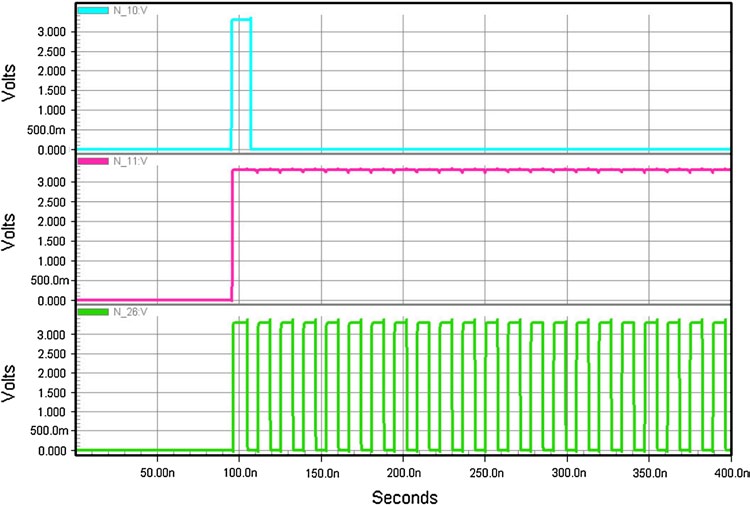

如图9所示,有一个名为“来自使能电路”的引脚。如果该引脚为零,则我们将没有输出端原本没有任何信号,但如果通过使能电路启用该引脚,并通过FPGA提供DcDe电路的5位信号,则可在DcO–DcDe的输出端观察到所选频率的脉冲序列。DcO–DcDe的使能引脚应保持高电平,直到我们希望在输出端产生脉冲序列为止。当该引脚处于低电平时,输出将变为零,因此应使用使能电路将该引脚保持在高电平状态。为此,使用了一个简单的DFF电路,如图10所示。如该fi图所示,使能电路通过其时钟端口从8位比较器获取激活信号。该电路的数据线(D)应保持高电平,且fi最终rn控制脉冲序列的持续时间。

具有5位数字输入向量的数字控制延迟元件(DcDe)

图11显示了5位数字控制的延迟单元(Maymandi‐nejad和Sachdev 2005)。该电路由三个主要部分组成。M10、M11、M12和M13晶体管的组合构成了电流受限反相器电路。晶体管M10和M13分别控制下降时间和上升时间。通过调节M10和M13晶体管的电流,可以调整电路的延迟。在我们的应用中,输出信号具有相同的上升和下降时间(50%占空比)非常重要,因此在设计电流镜电路时,应考虑M7、M8和M9晶体管。M7从数字控制的晶体管获取电流,并将相同的值复制到M10和M13。最后一级的电流可以通过M1、M2、M3、M4和M5晶体管进行控制。通过使用FPGA向控制晶体管(M1–M5)提供特定的二进制向量,可使这些晶体管的组合导通,从而为电流饥饿级提供不同的电流。这些晶体管通过外部线路利用FPGA实现导通或关断。

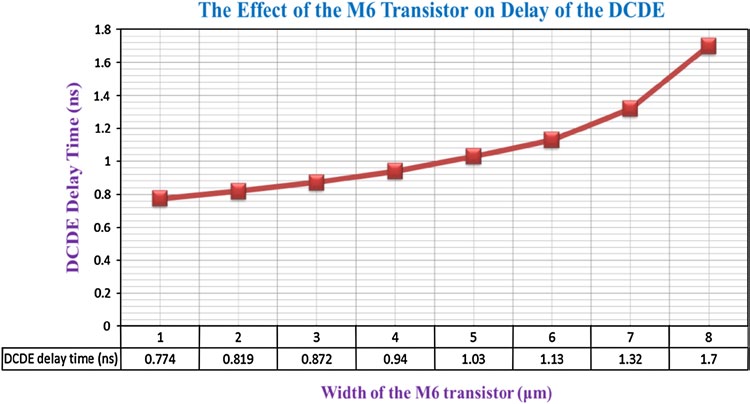

由于控制晶体管的W/l比决定了DcDe电路的延迟值,因此应评估这些晶体管对延迟时间的影响。fi根据图11,M6晶体管应保持导通状态。为了fi分析M6晶体管对DcDe电路延迟值的影响,假设M1–M5控制晶体管保持不变。稍后将解释,在我们的fi最终设计中,M6的W/l比为1/9.75,这适合我们的应用。图12显示了M6晶体管宽度(W)从1到8 μm变化时的影响,其长度为9.75 μm,数字输入向量为00000。从该fi图可以看出,M6主要影响DcDe电路的最大延迟。当M6的宽度增加,流入M7的电流fl也随之增强,因此DcDe电路的延迟值增加。从图12可以看出,在我们设计的DcDe电路中,这种变化是轻微且单调的。

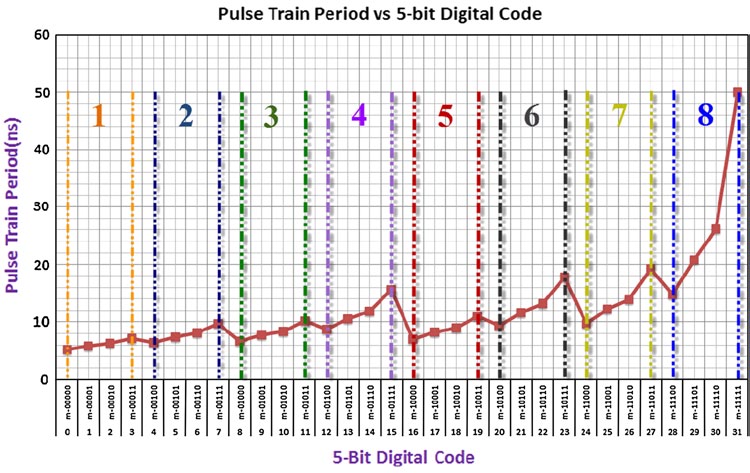

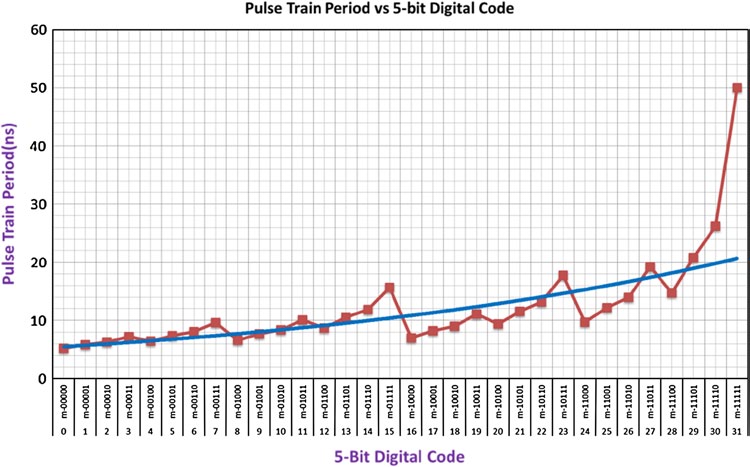

当我们fi固定M6晶体管的尺寸为1/9.75并调整M1–M5晶体管的尺寸时,我们观察到这些控制晶体管仅影响DcDe电路的最小延迟,而对电路的最大延迟没有任何影响。由于DcDe可通过fi位数字输入向量进行控制,因此可以获得32种不同频率。尽管我们可以设计一个完全线性且单调的DcDe,但由于我们决定生成特定频率(而不仅限于递增模式),因此我们设计了DcDe,使其在划分的小区域中具有线性关系(图13)。实际上,通过为我们的应用设计完全单调的DcDe,可能会丢失1–10 MHz范围内的某些重要频率。可以看出,在所有划分的小区域中,数字输入向量与脉冲序列的周期之间均存在单调递增关系。在每个区域中,其起始点相较于前一个区域的末尾点均有下降,因为如图fi14所示,我们希望在进入下一点之前不丢失所需的频率。所设计的带两个缓冲器的5位DcDe的平均功耗分别为165和844 μW,当电路生成21 ns延迟(在数字输入向量为11111时用于产生20兆赫脉冲串)和1.54皮秒延迟(在数字输入向量为00000时用于产生650吉赫脉冲串)时。

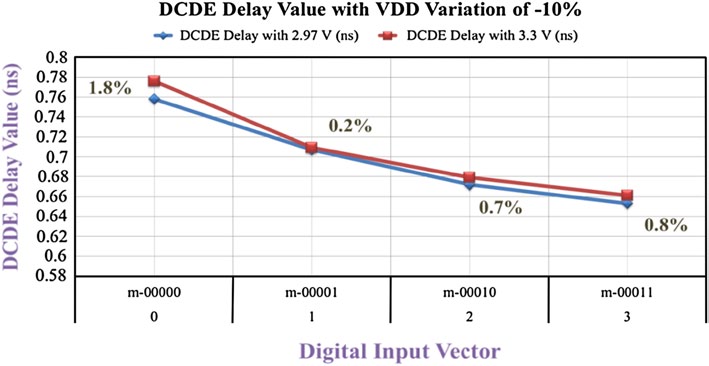

数字控制延迟元件的稳定性非常重要。DcDe最重要的性能参数之一是电源电压(VDD)变化对DcDe输出的影响。我们已在−10百分比 VDD变化下对DcDe进行了仿真,作为最坏情况。我们在布局部分采用了一些技术,通过短而低电阻的金属线直接为延迟元件提供电源电压。这些技术显著降低了VDD变化对DcDe电路性能的影响,但尽管如此,我们仍设计了一种对电源变化不敏感的DcDe。图15显示了在−10百分比电源变化下,一个较小的分区域中设计的数字控制延迟元件的延迟值。从该fi图可以看出,变化值为<2百分比。同时,图16和17显示了DcO–DcDe电路的仿真结果。如图所示,当比较器的输出变为高电平时,DcO的使能信号以可忽略的延迟时间生成,最终实现占空比为50%的脉冲序列。可以看出,当DcDe的数字输入向量分别为00000和11010时,可生成频率为190和71.5兆赫的脉冲序列。除了电源(VDD)变化外,温度变化作为DcO–DcDe最重要的性能参数之一,也会影响电路。

表1 温度(T = 50 °c)对设计的DcO–DcDe周期的影响

| 数字输入向量 | 温度 = 25 °c (ns) | 温度 = 50 °c (ns) | % of 变化 |

|---|---|---|---|

| 11101 | 20.8 | 21.5 | 3.3 |

| 10101 | 11.6 | 12 | 3.4 |

| 11111 | 50 | 51.9 | 3.8 |

| 00000 | 5.2 | 5.4 | 3.8 |

| 11110 | 26 | 26.9 | 3.4 |

表2 温度(T = 75 °c)对设计的DcO–DcDe周期的影响

| 数字输入向量 | T = 25 °c (ns) | T = 75 °c (ns) | % of 更改 |

|---|---|---|---|

| 11101 | 20.8 | 21.7 | 4.3 |

| 10101 | 11.6 | 12.1 | 4.3 |

| 11111 | 50 | 52.4 | 4.8 |

| 00000 | 5.2 | 5.45 | 4.8 |

| 11110 | 26 | 27.2 | 4.6 |

DcO–DcDe电路在− 10百分比 VDD变化以及25、50和75摄氏度下分别进行了仿真。表1总结了DcO–DcDe电路在25和50摄氏度下生成的脉冲串的周期。可以看出,通过对fi个样本5位数字输入向量进行DcO–DcDe电路仿真,在25和50摄氏度之间的变化值为<5百分比。另一方面,表2总结了DcO–DcDe电路在25和75摄氏度下生成的脉冲串的周期。可以看出,通过仿真DcO–DcDe相同电路的 five样本5位数字输入向量,在25和75摄氏度之间的变化值为<5百分比。表3显示了DcO–DcDe电路在− 10百分比电源变化下生成的脉冲串周期。从该表可以看出,变化值为<5百分比。

表3 电源电压(−10%)对设计的DcO–DcDe周期的影响

| 数字输入向量 | VDD = 3.3 V (ns) | VDD = 2.97 V (ns) | % of 变化 |

|---|---|---|---|

| 11101 | 20.8 | 21.5 | 3.3 |

| 10101 | 11.6 | 11.9 | 2.5 |

| 11111 | 50 | 52.3 | 4.6 |

| 00000 | 5.2 | 5.44 | 4.6 |

| 11110 | 26 | 27.1 | 4.2 |

频率下变频(FDc)电路

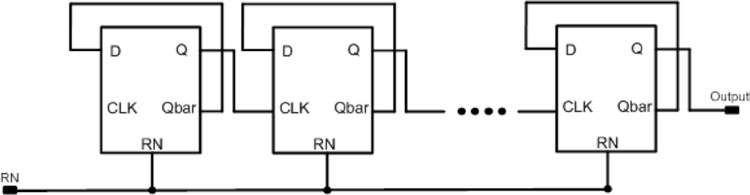

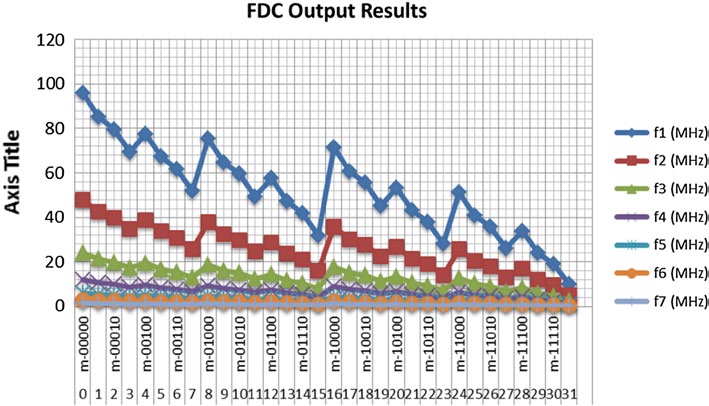

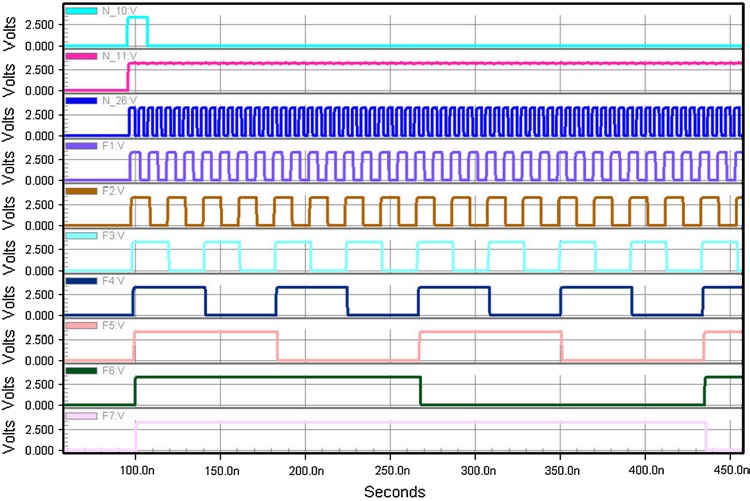

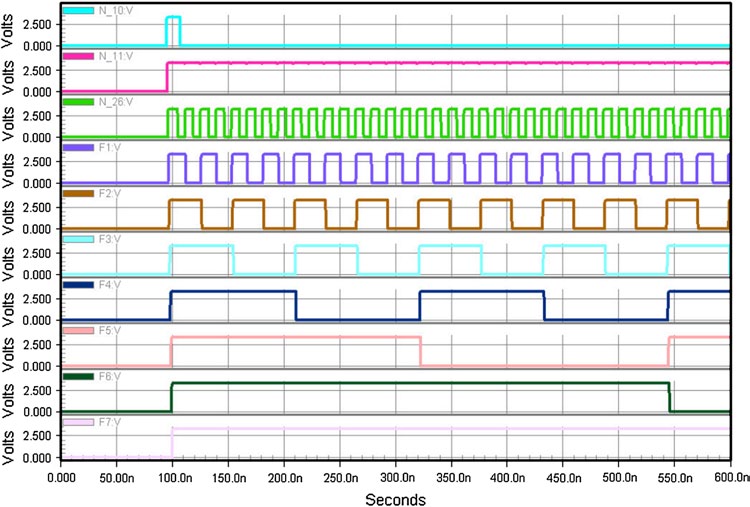

由于我们生成的频率处于较高频率范围,需要将其降低至1–10 MHz,因为我们设计的超声换能器的工作频率在该频率范围内。图18展示了用于产生适合我们治疗应用的频率下变频(FDc)电路使用七个并排的D触发器的应用。图19显示了七级FDc电路的仿真结果。由于使用DcO–DcDe电路生成了32种不同的脉冲序列,且FDc电路中有八种不同的输出,因此可获得256种不同频率的脉冲串。最后,通过同时使用DcO–DcDe–FDc电路,可在1–10 MHz范围内以良好分辨率生成各种频率的脉冲序列。

以00000和11010作为数字输入向量的FDC电路的仿真结果分别如图20和21所示。从这些fi图中可以看出,每当FDC电路接收到脉冲串时,信号频率在七个不同的阶段被二分。实际上,该电路在fi最后一步将频率降低了128倍。DcO–DcDe电路与FDC电路的组合连接到一个8 × 1多路复用器,用于选择不同应用所需的生成频率。例如,通过生成频率为20 MHz的脉冲序列,我们可以获得10、5、2.5、1.25、0.625、0.3125和0.15625 MHz的频率。使能电路与DcO以及三个5位DcDe电路的组合在20和190 MHz下消耗的平均功耗分别为1.98和3.9 mW。

采用THKOX晶体管的45V高压脉冲电路

在前面的章节中,讨论了我们专用集成电路设计中的低压模块。fi环形系统为16个cMUT阵元中的每一个提供一个驱动电路。正如我们提到的,cMUT阵元由具有可调脉冲宽度的单脉冲和根据其工作频率可控频率的脉冲串来激励。图22显示了所用高压脉冲电路的示意图,采用高压0.35 μm CMOS工艺设计(hatfield和chai 2001)。

这些脉冲发生器的输出连接到flip‐芯片焊盘。设计的脉冲发生器配置为源极跟随器。一个包含M7和M8晶体管的强反相器连接到Sn节点和Sp节点。来自集成电路驱动部分的传输信号(单脉冲或脉冲串)被传送到脉冲发生器的Sp节点。当Sp从零跳变到VDD(3.3 V)时,Sn以相反模式变化,因此M4的栅极电压降低。

M4的源极‐栅极间允许的最大电压由所使用的CMOS工艺决定(对于我们采用的工艺为18伏特)。当M4导通时,该晶体管的输出开始向hVDD(45伏特)上升,并fi最终使作为源极跟随器的晶体管M6跟随该转换过程,从而使脉冲发生器的输出升至hVDD。由于反相器的输出处于低电平状态,M3和M4处于关断状态。

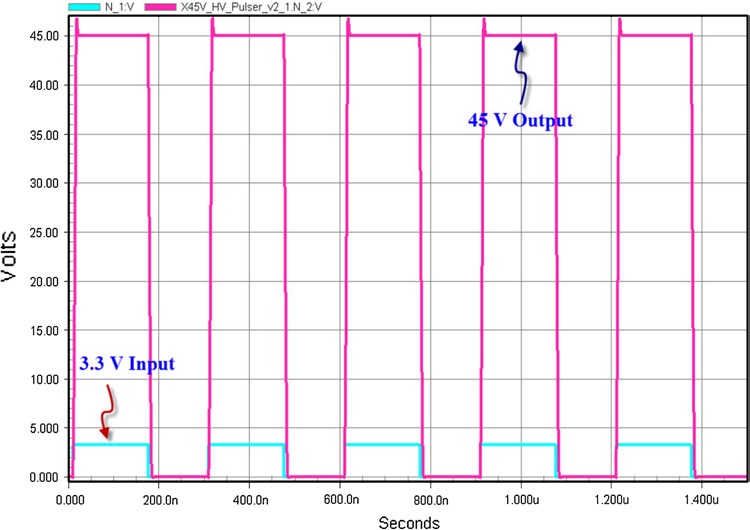

在反向模式下,当S_P降至地电平时,S_n节点上的电压从零跳变为VDD,使M3和M4导通,因此脉冲发生器的输出降至地电平。高压脉冲电路的设计已优化,以满足我们应用的基本要求。图23显示了高压脉冲电路的仿真结果,该电路已经采用厚氧化层(ThKOX)晶体管设计。如图所示,该电路的输出为45伏特(hV),而其输入为3.3 V(l V)。

表4总结了45伏脉冲电路的一些重要参数,例如上升/下降时间、转换速率、功耗和fi品质因数。这些参数的数值分别针对输出幅度为15伏、30伏和45伏特的情况进行了展示。根据表5,所设计的该电路与他人的先前工作(Khorasani等人 2008年)相比,表现出良好的结果。

表4 用于在3.33兆赫下驱动2.5皮法电容负载时最高达45伏特的高压脉冲发生器的设计规格

| 参数 | 仿真结果 | 单位 |

|---|---|---|

| 上升时间(10–90%)在 V hV= 15 V | 3.85 | ns |

| 下降时间(90–10%)在 V hV= 15 V | 2.75 | ns |

| 上升时间(10–90%)在 V hV= 30 V | 4.45 | ns |

| 下降时间(90–10%)在 V hV= 30 V | 5.53 | ns |

| 上升时间(10–90%)在 V hV = 45 V | 5.13 | ns |

| 下降时间(90–10%)在 V hV = 45 V | 8.7 | ns |

| 转换速率(上升)在 VhV= 30 V | 2.33 | V/μs |

| 转换速率(下降)在 VhV= 30 V | 1.52 | V/μs |

| 转换速率(上升)在 VhV= 45 V | 3.9 | V/μs |

| 转换速率(下降)在 VhV= 45 V | 1.89 | V/μs |

| Pav(功耗)在VhV= 15 V时 | 13.77 | mw |

| Pav(功耗)在VhV= 30 V时 | 29.04 | mw |

| Pav(功耗)在VhV= 45 V时 | 51.66 | mw |

| 优值 = D/(l V) 在 VhV= 15 V时 | 1.08 | 纳秒/(μm V) |

| 优值 = D/(l V) 在 VhV= 30 V时 | 0.66 | 纳秒/(μm V) |

| 优值 = D/(l V) 在 VhV= 45 V | 0.51 | 纳秒/(μm V) |

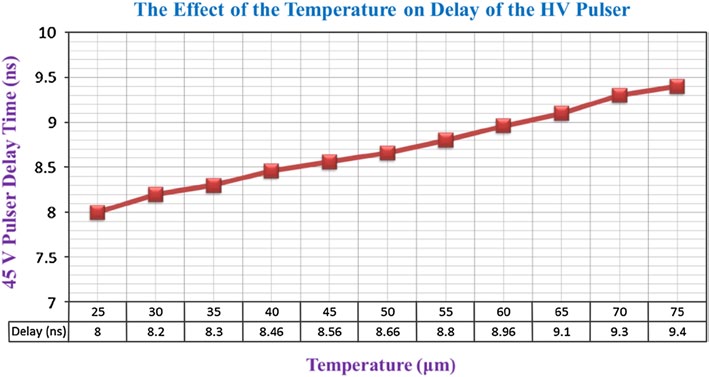

设计的高压脉冲电路应保持对温度变化的稳定性。如图24所示,该电路的总延迟时间在25至75摄氏度范围内变化了1.4纳秒,即延迟时间有17.5%的变化。此外,该电路的fi品质因数从0.51变化到0.59纳秒/(μ毫伏)。

电容式微机械超声换能器阵元的直流偏置

通过在电容式微机械超声换能器的顶部和底部电极之间施加直流电压,顶部电极板会被吸引向下方基板由于静电吸引力的作用。在芯片上考虑了一些用于阵列直流偏置电压的焊盘。从图fl中可以看出,这些焊盘通过贯穿晶圆互连与cMUT阵列的顶部电极相连。实际上,25所示的顶部电极cMUT阵列与所有换能器元件共用,并通过集成电路为cMUT阵元提供直流偏置。cMUT阵元的底电极通过flip芯片 bonding pads逐个连接到高压脉冲发生器的输出端。电阻r和电容c由所有超声换能器共用,其阻值范围分别为数百千欧和数百纳法或更大。该电阻用于将电源与短路元件隔离。在电容fi滤除高压电源噪声并为电容式微机械超声换能器提供交流地的同时,限制电流。

面向4 × 4电容式微机械超声换能器阵列的超声治疗集成电路布局概述

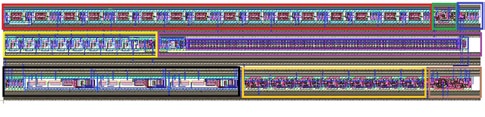

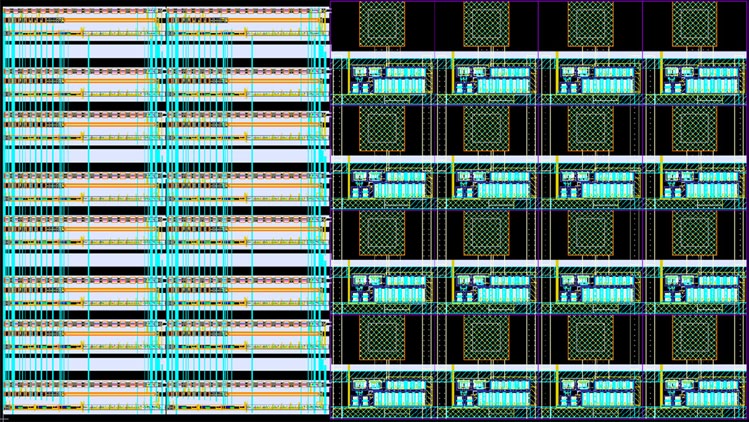

根据图26所示,该fi集成电路的布局分为两个主要部分。布局的左侧包含cMUT驱动电路和需要精确绘制、布线和连接的低压模块,右侧则包括高压脉冲发生器以及应逐个连接到cMUT阵元的芯片焊盘。在芯片的驱动部分,设有16个独立的模块,用于16个高压脉冲电路。由于我们的fi设计中包含16个cMUT阵元,因此需要在fl集成电路中放置16个完整的模块,每个模块包含低压模块、高压模块以及芯片焊盘。fi集成电路。

图27显示了芯片驱动部分的布局。波束成形系统为每个cMUT单元提供一个低压模块。这些模块以四乘四的配置尽可能紧凑地排列在一小块区域内。根据此fi图,驱动部分的芯片已分布在三个fl层。在fi一层,放置了8位移位寄存器、使能电路和MU2X1。在第二层有8位比较器和单稳态电路,fi后在第三fl层放置了DcO–DcDe、FDC和MU8X1模块。驱动部分的芯片裸芯片面积为43283.7 μm²(94.3 × 459 μm)。

图28显示了芯片核心的布局。显然,芯片核心被分为两个完全不同的部分:一部分用于驱动电路,另一部分用于高压脉冲发生器和片上焊盘。如图所示,每两个相邻的片上焊盘之间的中心到中心距离为flfl个片上焊盘之间的中心到中心距离是300 μm。该规格对我们非常重要,因为cMUT阵列需要以相同的配置键合到该布局区域。用于ficMUT单元的芯片核心裸芯片面积为2.57 mmfi,其中芯片核心的裸芯片面积为4 × 4cMUT阵元为2.57 mm² (2 × 2.1428 mm)。

如图29所示,设计的集成电路包含四个主要区域:低压焊盘、高压焊盘、cMUT直流焊盘和芯片核心。低压焊盘用于实现芯片驱动部分与现场可编程门阵列的通信。高压焊盘为脉冲发生器提供高压电源,而直流焊盘则通过片上焊盘与电容式微机械超声换能器相连,以向cMUT阵元提供直流电压。为了从集成电路获取一些测试结果,部分焊盘同时布置在低压和高压区域。fl

最后,fi用于超声治疗应用的所设计集成电路的最终布局如图30所示。该最终集成电路包含45个I/O低电压(3.3 V)焊盘、7个3.3 V电源焊盘、9个高压焊盘,以及1个用于电容式微机械超声换能器超声换能器的直流电源焊盘。低电压焊盘用于通过现场可编程门阵列对集成电路进行测试和驱动,高压焊盘用于测试并支持集成电路的高压电源,fi最后,直流焊盘应通过芯片级焊盘连接到微机电系统部分,并通过该焊盘为电容式微机械超声换能器阵元提供直流电源。用于电容式微机械超声换能器治疗应用的最终设计芯片的裸芯片面积为13.5725 mm²(4,450 × 3,050 μm)。

用于具有任意焦点的4 × 4电容式微机械超声换能器阵列的波束形成和脉冲延迟计算MATLAB程序

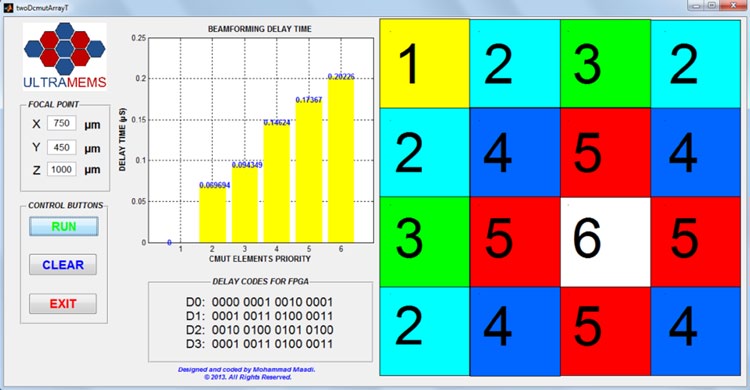

在像本研究中考虑的完全填充的二维cMUT阵列中,通过电激励获得超声波的聚焦波束按照预定顺序对阵列元件进行操作。该软件专注于对4 × 4 cMUT阵列的接口电子器件进行仿真,其中预定序列由现场可编程门阵列生成。用户指定焦点坐标(x,y,z),然后软件计算每个cMUT单元的延迟,并生成现场可编程门阵列应发送给移位寄存器的预期代码。现场可编程门阵列代码以二进制形式显示,延迟以条形图绘制,激励序列通过动画展示。

为了提供更好的视野,此处给出一个示例。在此示例中,仿真针对位于cMUT阵列平面上方1000 μm处的位置进行,x和y的值分别为750和450 μm。计算出的波束成形延迟汇总于表6中。

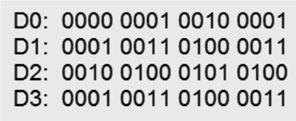

从该表可以看出,如果第一个cMUT元件在零时刻被激励,则下一个元件应在69.694 ns后被触发。对于假定的焦点,我们需要生成五种不同的延迟时间。除了精确的延迟时间计算外,该程序还会生成建议的数字输入信息,这些信息应由FPGA提供给集成电路。由于接口电子器件通过四条独立的延迟线加载,因此需要提供四个数字码。如图31所示,D0、D1、D2、D3分别对应从上到下四行cMUT阵元的数字延迟码。每个半字节对应于要移入专用集成电路中相应元件移位寄存器内容的最低有效半字节。ficant nibble to be shifted into theshift register content for the corresponding element in theaSIc。

如图32所示,触发序列通过开启特定颜色及相应的优先级编号来表示。可以观察到,对于所考虑的焦点,必须生成六种不同的延迟时间。

的输出)

表6 计算的波束成形延迟

| 元件触发优先级和颜色 | 波束成形延迟 (μS) |

|---|---|

| 1—黄色 | 0 |

| 2—浅蓝色 | 0.069694 |

| 3—绿色 | 0.094349 |

| 4—蓝色 | 0.14624 |

| 5—红色 | 0.17367 |

| 6—白色 | 0.20226 |

结论

本文提出了一种用于超声治疗应用的、基于0.35 μμm CMOS高压工艺的高灵活性和可编程发射波束成形专用集成电路(ASIC),适用于cMUT阵列。每个cMUT单元均配备有一个8位移位寄存器、一个8位比较器、一个具有可调脉冲宽度的单稳态电路、一个可编程脉冲序列发生器以及一个高压脉冲发生器电路。所设计的单稳态电路能够将脉冲宽度从几纳秒调节至650 ns,具备足够的分辨率以适应超声换能器不同的工作频率;而数控振荡器(DcO)、DCDE电路和FDC电路的组合则可提供频率在1–10 MHz范围内可控的脉冲串。在DCDE电路中,根据5位数字输入向量,可实现32种不同的延迟设置,5–50纳秒的范围可以实现。为了便于根据给定的数字输入向量预测DcDe的延迟时间,我们尝试在不同小区域内生成随着二进制输入模式递增而单调变化的延迟行为。由于设计的DcO–DcDe电路的稳定性非常重要,该电路被设计为在−10% VDD变化以及25、50和75摄氏度温度范围内保持稳定。25–50摄氏度和25–75摄氏度的温度变化值分别为<5%。此外,当电源电压降低−10%时,电路表现出<5%的变化。所设计的带两个缓冲器的5位DcDe平均功耗分别为165毫瓦和844 μ毫瓦,分别对应于当数字输入向量为11111时产生21纳秒延迟(用于生成20兆赫脉冲串)和当数字输入向量为00000时产生1.54皮秒延迟(用于生成650吉赫脉冲串)的情况。为了提高脉冲串频率的分辨率,我们在DcO–DcDe中增加了频率下变频(FDc)电路。通过使用一个8 × 1路多路复用器可以选择FDc电路的输出,从而在1–10兆赫范围内以良好的分辨率生成256种不同的脉冲串频率。单脉冲和脉冲串模式通过一个1 × 2路解复用器相互分离。在fi最后阶段,利用带有ThKOX模块的高压脉冲发生器将单脉冲或脉冲串的幅度提升至45伏特。当脉冲幅值为45伏特时,对于2.5皮法电容负载,输出信号的上升和下降时间分别为5和8纳秒。该电路在V hV= 45 V下的转换速率和fi品质因数分别为1.89伏特/μ微秒和0.51纳秒/(伏特μ米)。这类电路具有显著的功耗。我们设计的高压脉冲电路在输出45伏特信号时消耗51.66毫瓦。

3099

3099

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?