72~78卡诺图

强烈建议大家去看看HDLBits 中文导学,原文在知乎

链接: link.

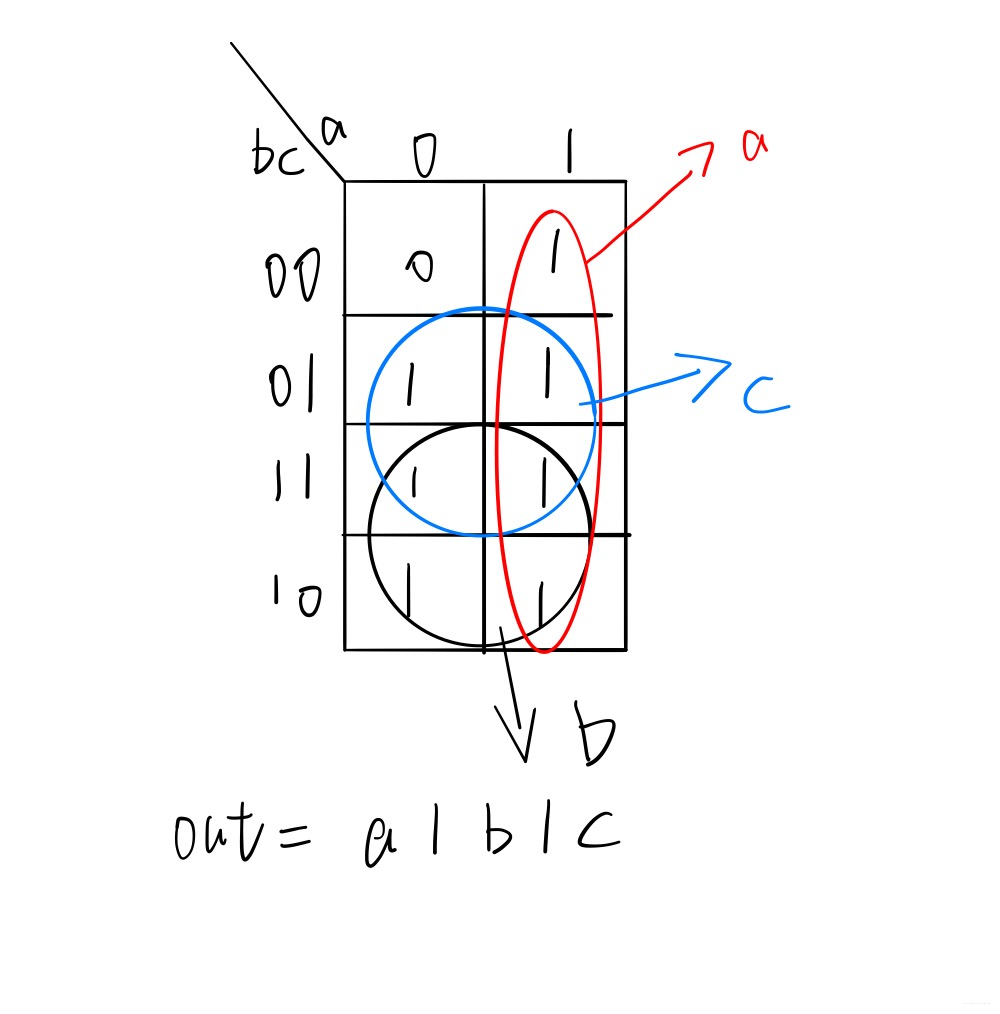

72.3-variable Karnaugh map

module top_module(

input a,

input b,

input c,

output out );

assign out=b|(!b&c)|(a&!b);

endmodule

我的一开始化简出来,并不是最简的,

module top_module(

input a,

input b,

input c,

output out );

assign out = a | b | c;

endmodule

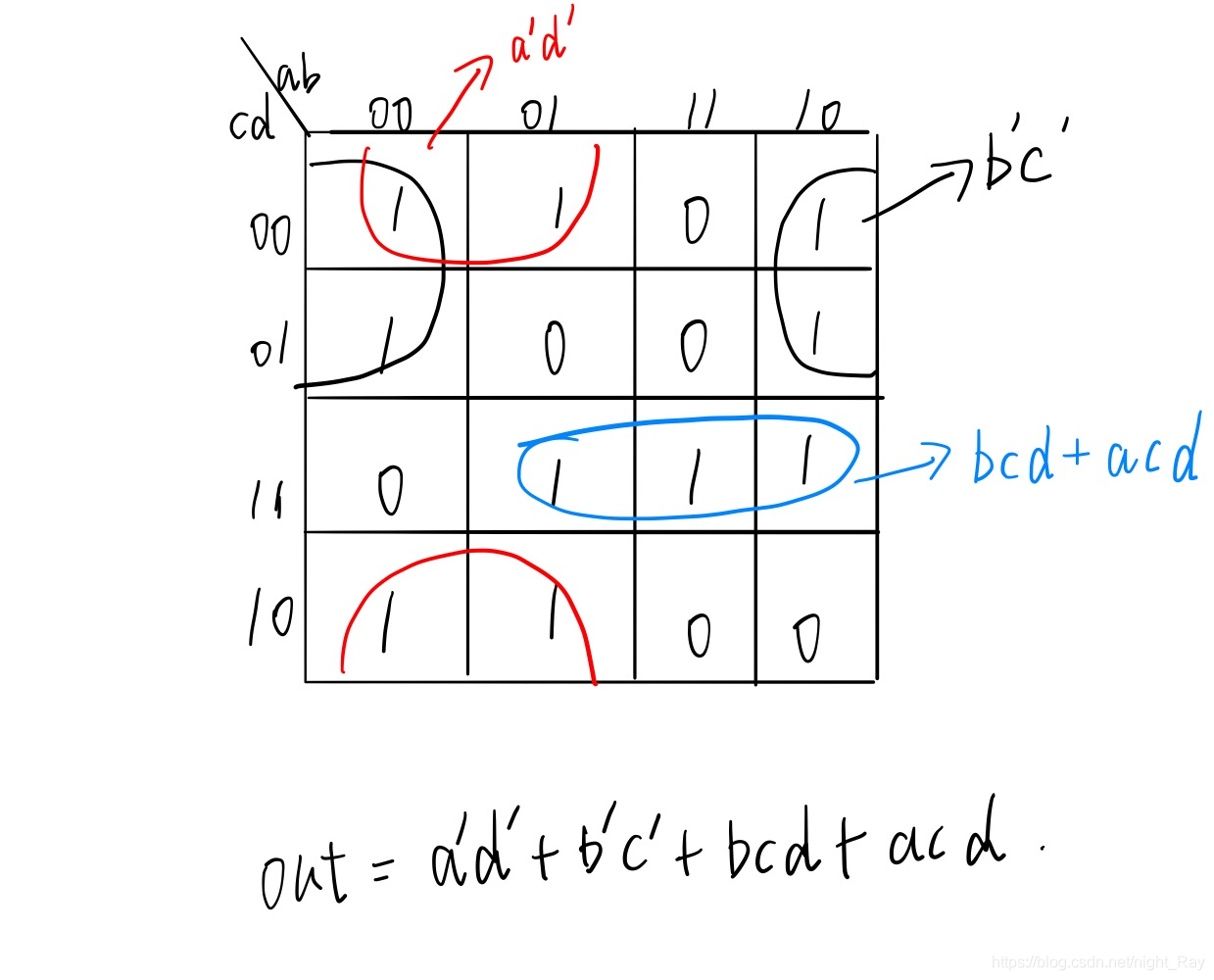

73.4-variable Karnaugh map

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out=(!a&!d)|(!b&!c)|(b&c&d)|(a&c&d);

endmodule

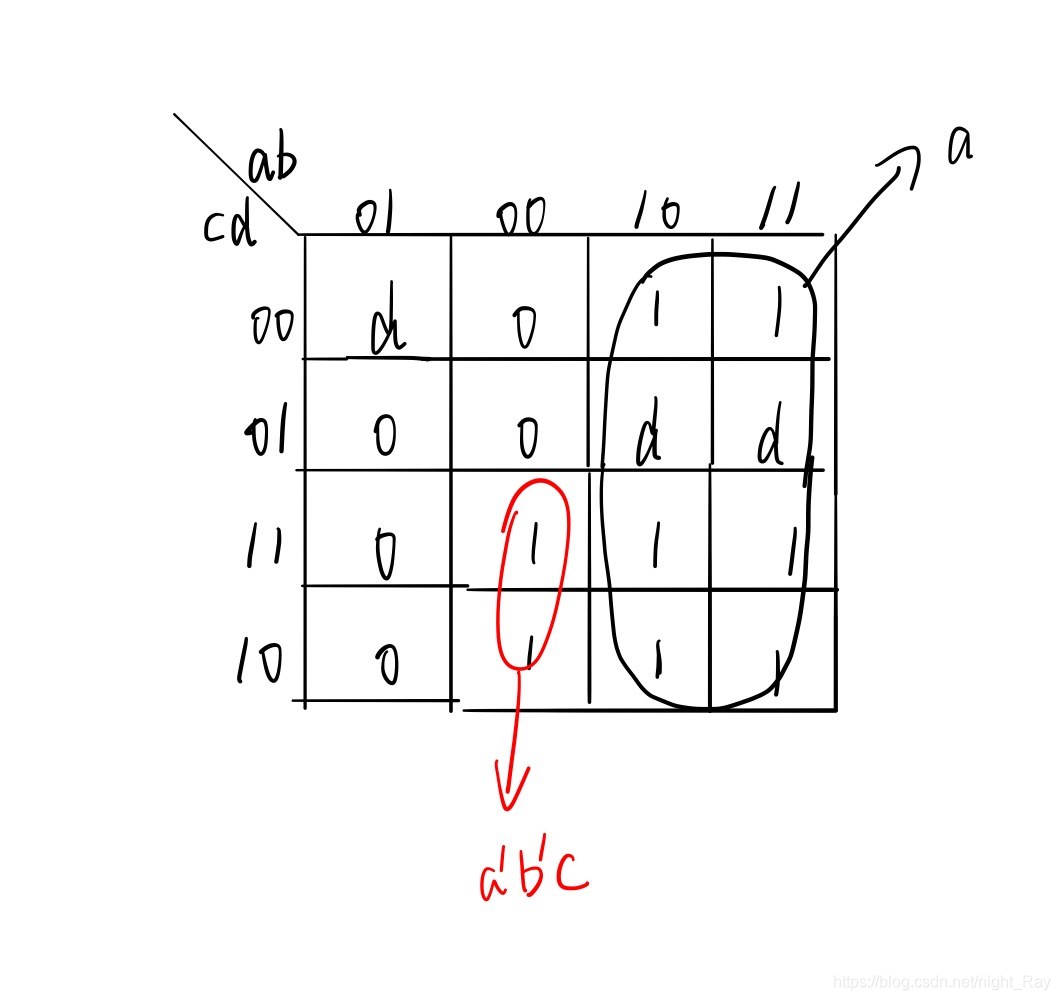

74.4-variable Karnaugh map-2

卡诺图中的d是无关项,可以为1,可以为0;

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out=a|(!b&c)|(a&c);

endmodule

75.4-variable Karnaugh map-3

这个没法化简,只能挨个写;

assign out = (~a&b&~c&~d) | (a&~b&~c&~d) | (~a&~b&~c&d) | (a&b&~c&d) | (~a&b&c&d) | (a&~b&c&d) | (~a&~b&c&~d) | (a&b&c&~d);

76.Minimum SOP and POS

SOP(SumOfProduct):将所有真值表中输出为1的项相加;

POS(ProductOfSum):将所有真值表中输出为0的项相乘;

化简方法可以利用公式,卡诺图等;

卡在这里好久,主要是最大项之积化简卡诺图的时候,0是代表正的,1代表非,和最小项之和相反,记错了导致一直报错;

关于最大项之积,可以看看这一篇:

link.

assign out_sop=(c&d)|(!a&!b&c);

assign out_pos=c&(d|!a)&(!c|d|!b);

76.Karnaugh map-1

//assign f=(!x[1]&x[3])|(x[1]&x[2]&!x[3]);

assign f=(x[1]|x[3])&(!x[1]|x[2])&(!x[3]|!x[1]); //用最小项之和比较简单;

77.Karnaugh map-2

assign f=(x[3]|!x[4])&(x[3]|!x[2])&(x[4]|!x[1]|!x[2])&(!x[4]|!x[1]|x[2]);//最大项之和

78.K-map implemented with a multiplexer

要注意顺序,卡诺图的顺序和高低位的顺序不对应;

assign mux_in={{c&d},{!d},{1'b0},{c|d}};

该博客主要介绍了使用卡诺图进行逻辑函数化简的方法,包括3变量和4变量的卡诺图实例。通过实际的VHDL代码展示了如何将逻辑表达式简化为最简形式。此外,还提到了SOP(最小项之和)和POS(最大项之积)的概念,并给出了相应的化简技巧和错误陷阱。同时,讨论了在实现卡诺图时使用多路复用器应注意的顺序问题。

该博客主要介绍了使用卡诺图进行逻辑函数化简的方法,包括3变量和4变量的卡诺图实例。通过实际的VHDL代码展示了如何将逻辑表达式简化为最简形式。此外,还提到了SOP(最小项之和)和POS(最大项之积)的概念,并给出了相应的化简技巧和错误陷阱。同时,讨论了在实现卡诺图时使用多路复用器应注意的顺序问题。

1707

1707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?