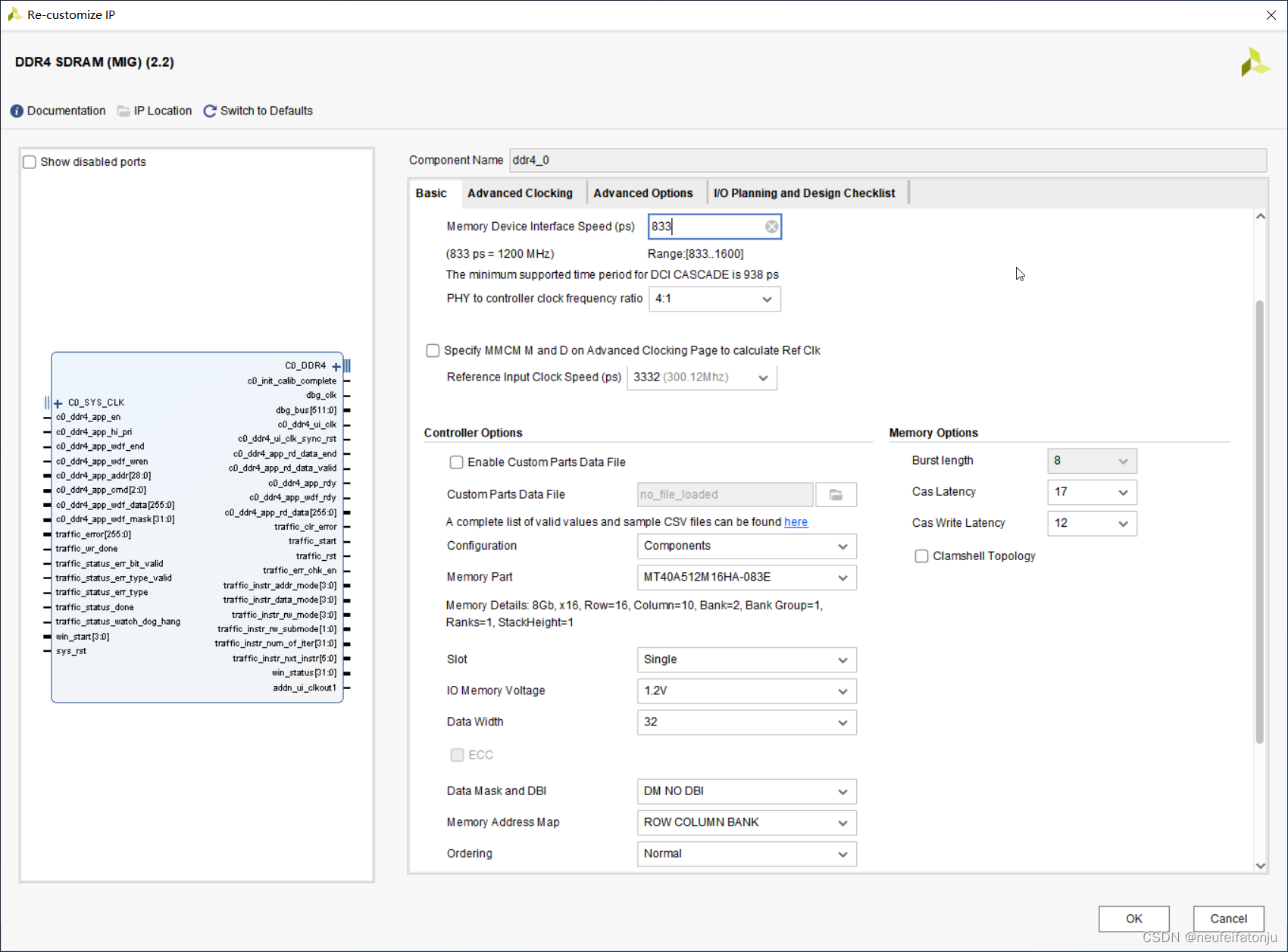

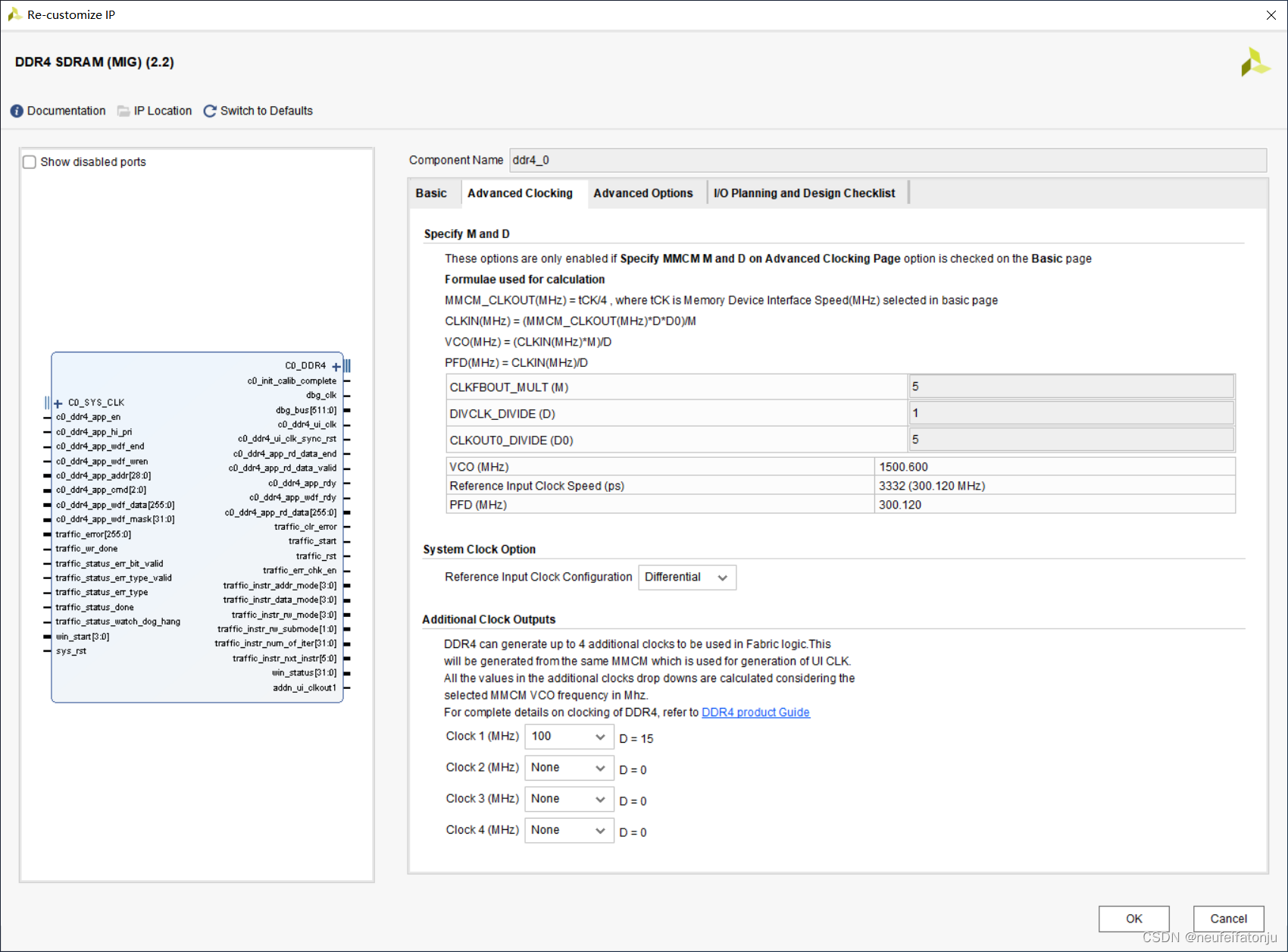

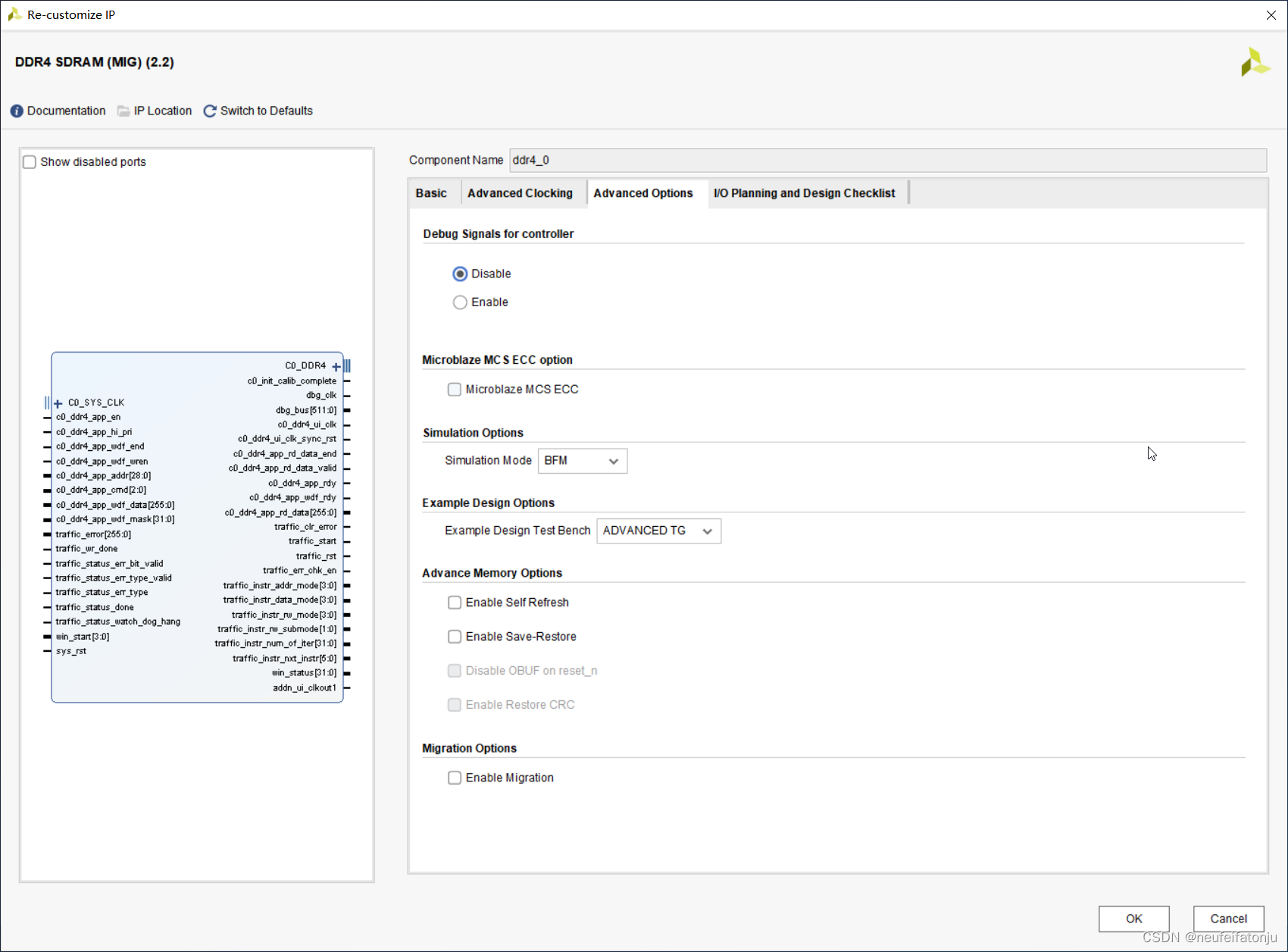

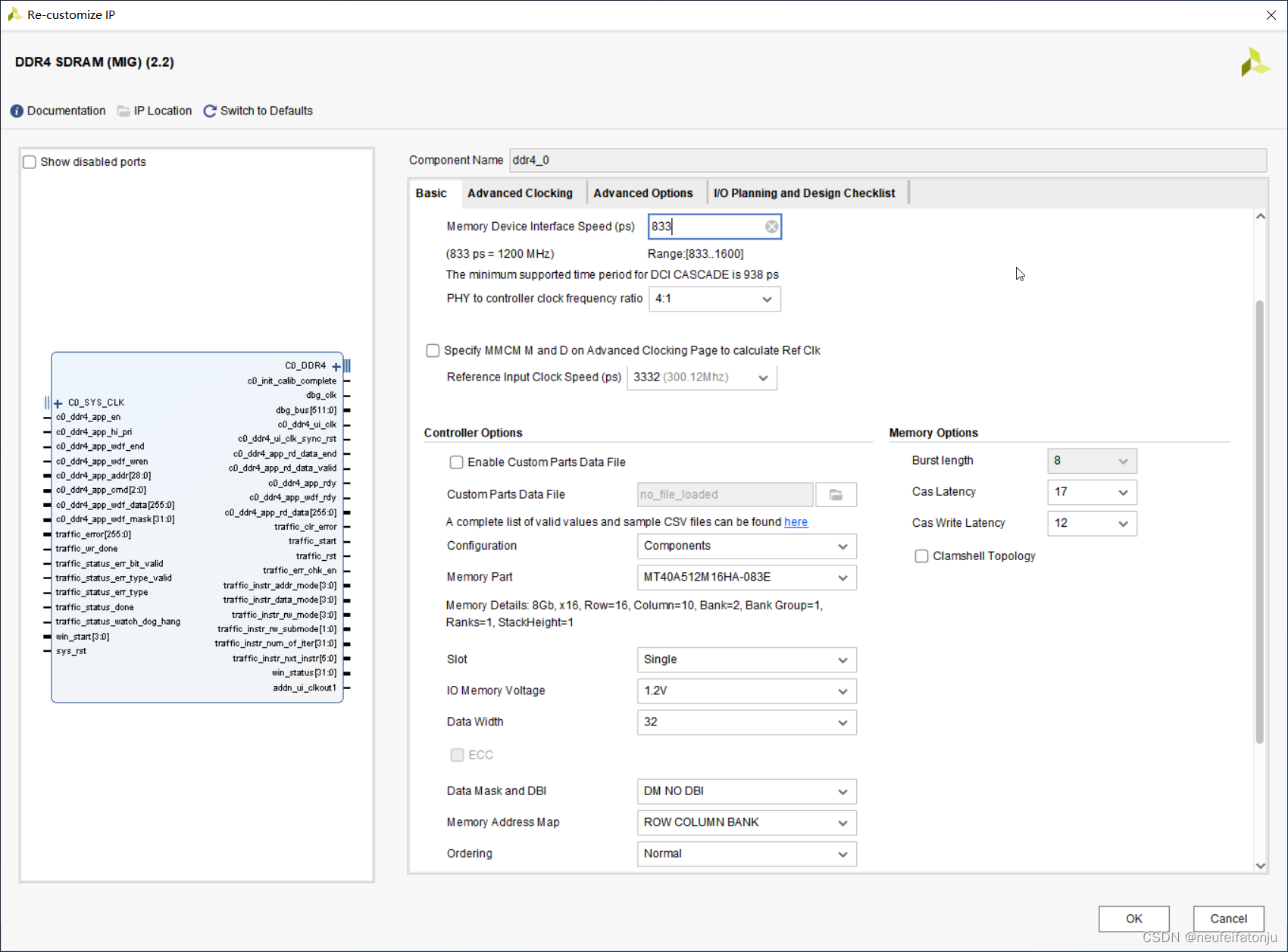

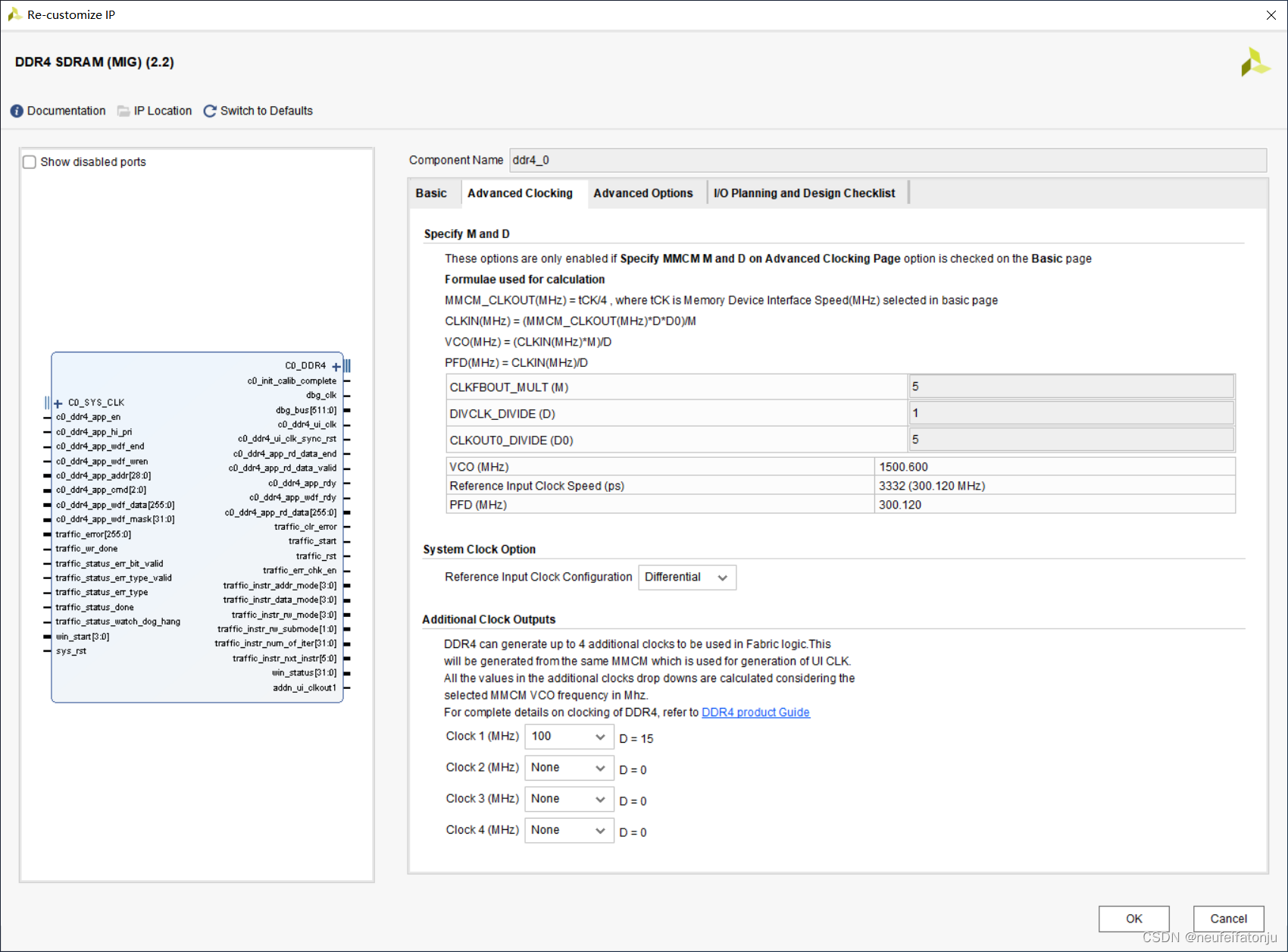

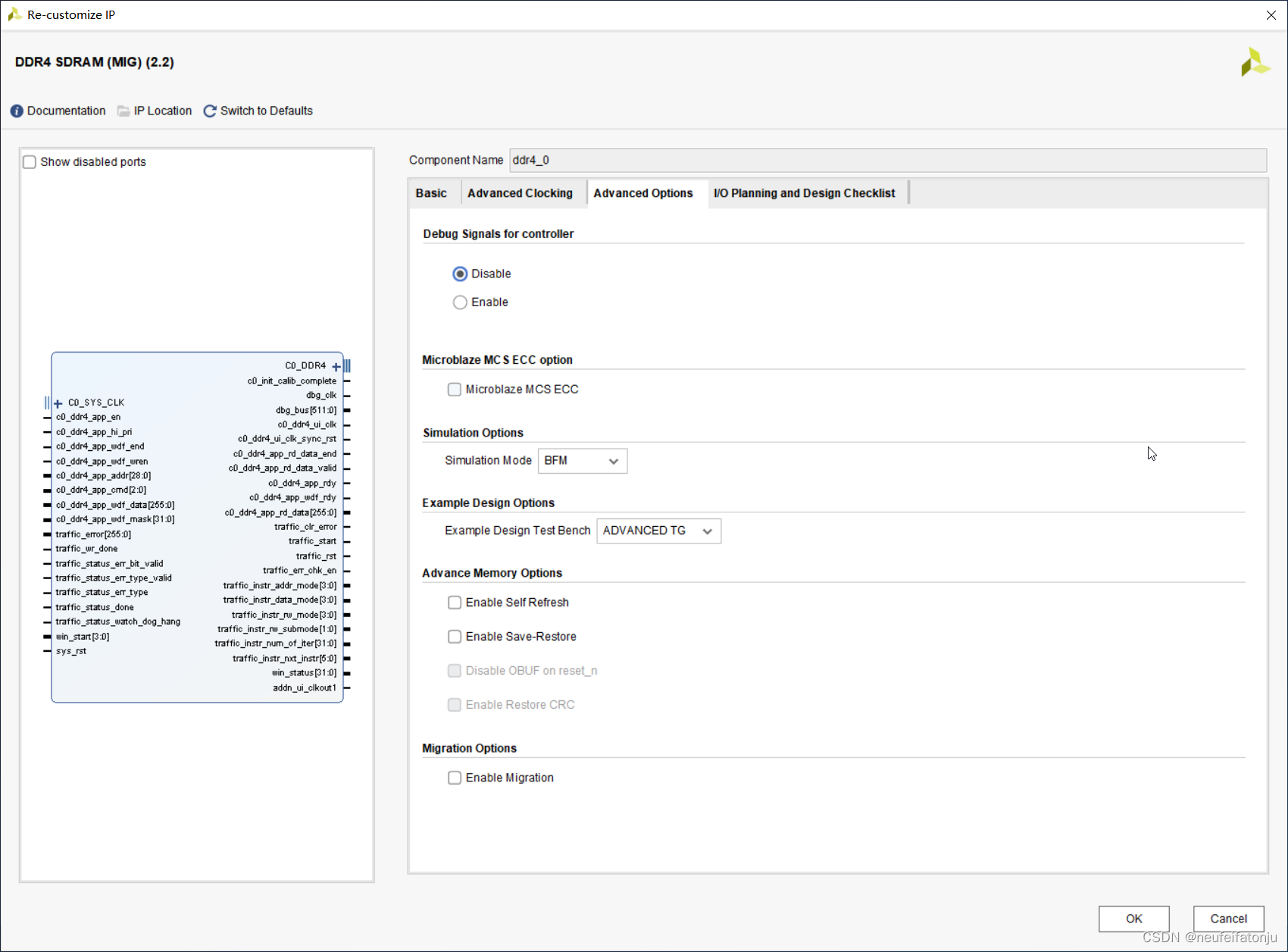

1.生成DDR4 IP核;

2.打开example工程,编译;

3.打开Implementation;

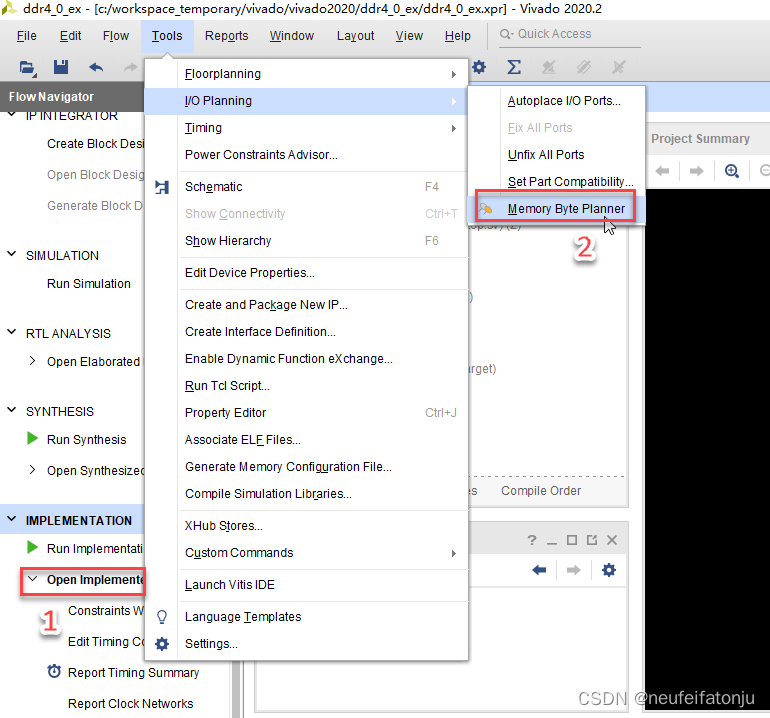

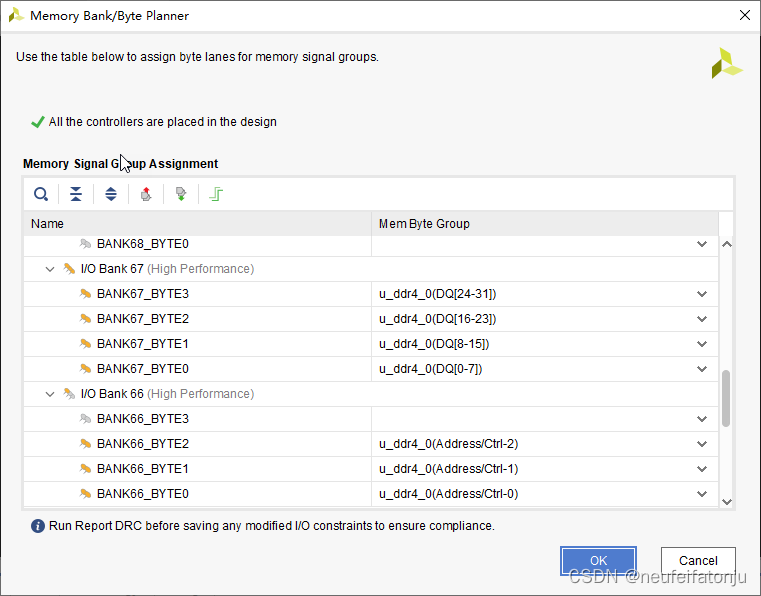

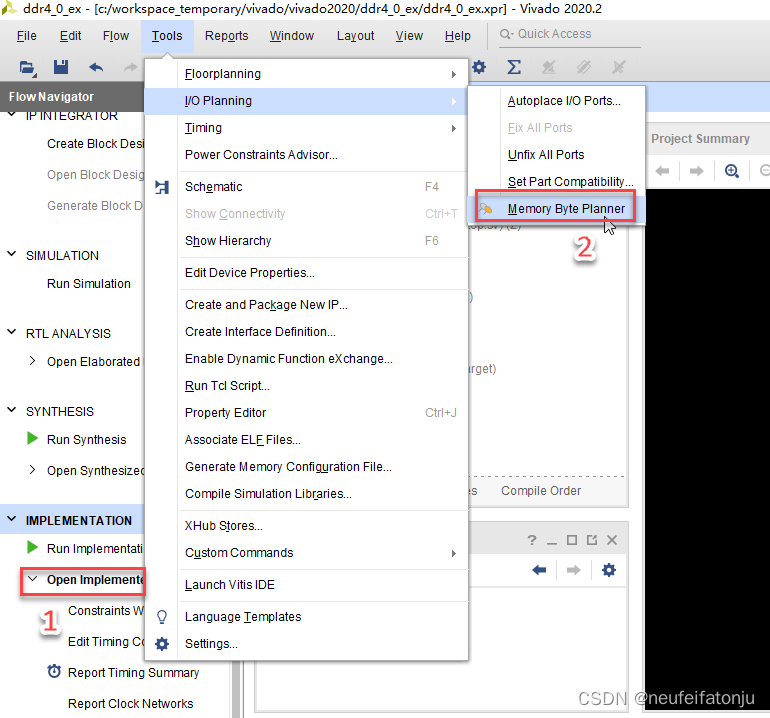

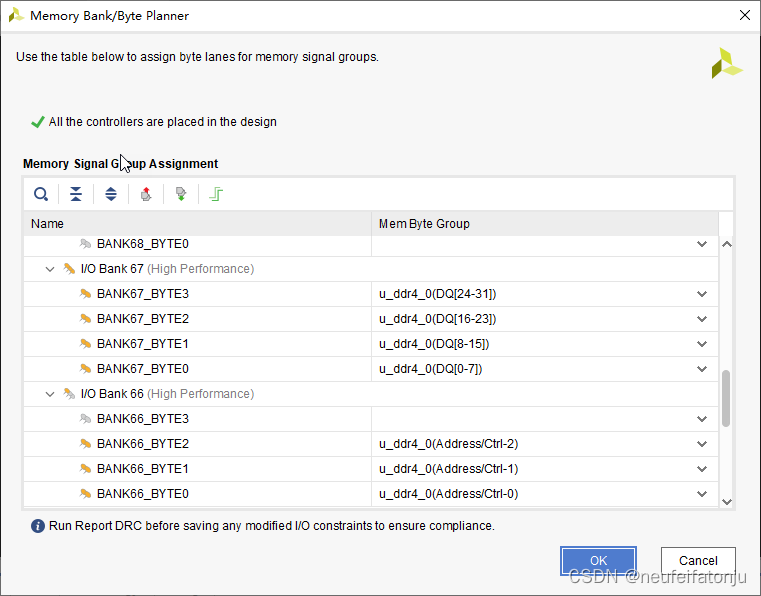

4.选择Tools --> I/O Planning --> Memory Byte Planner进行引脚约束。

附MIG核生成

1.生成DDR4 IP核;

2.打开example工程,编译;

3.打开Implementation;

4.选择Tools --> I/O Planning --> Memory Byte Planner进行引脚约束。

附MIG核生成

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?