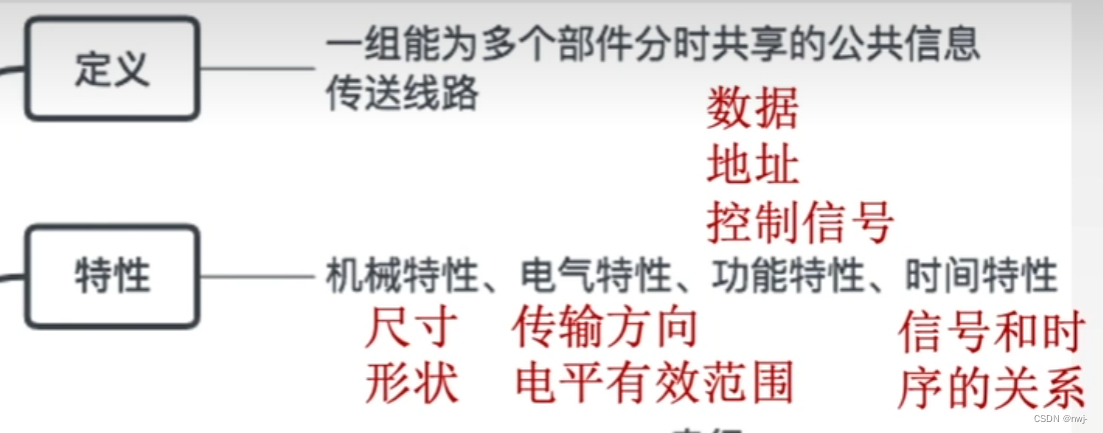

总线的特性

片内总线

芯片内部的总线,CPU内部的寄存器与寄存器、寄存器与ALU之间的公共连接线。

系统总线(机械、电气、功能、时间)

地址(AB):单向(cpu到主存/硬盘等硬件部件)

传递地址信息:告诉cpu访问的地址信息

信号线数量(位数):主存地址空间和输入输出设备的地址编号顺序有关位数要至少最大的编号相同。

数据(DB):双向

传递实际的信息:如从主存中取出指令、操作数等

信号线数量(位数):机器字长和存储字长有关

控制(CB):单根控制线是单向(cpu到主存/硬盘等硬件部件) 整体是双向的既有可能是cpu传输也有可能是反馈。

传输控制信号:告诉cpu的传输信号和I/O设备的反馈

总线结构的优缺点、带宽

总线接口是将处理器、内存和其他外设连接起来的接口

带宽计算

这条总线在单位时间内可以传输的数据总量,它等于总线位宽与工作频率的乘积。

[例如,对于64位、800MHz的前端总线,它的数据传输率就等于]

[64bitx800MHz÷8(Byte)=6.4GB/s;]

[32位、33MHz PCI总线的数据传输率就是32bit×33MHz÷8=132M]

优点

①面向存储器的双总线结构信息传送效率较高,这是它的主要优点。但CPJ与I/O接口都要访问存储器时,仍会产生冲突。

②CPU与高速的局部存储器和局部I/O接口通过高传输速率的局部总线连接,速度较慢的全局存储器和全局I/O接口与较慢的全局总线连接,从而兼顾了高速设备和慢速设备,使它们之间不互相牵扯。

③简化了硬件的设计。便于采用模块化结构设计方法,面向总线的微型计算机设计只要按照这些规定制作CPU插件、存储器插件以及I/O插件等,将它们连入总线就可工作,而不必考虑总线的详细操作。

④简化了系统结构。整个系统结构清晰。连线少,底板连线可以印制化。

⑤系统扩充性好。一是规模扩充,规模扩充仅仅需要多插一些同类型的插件。二是功能扩充,功能扩充仅仅需要按照总线标准设计新插件,插件插入机器的位置往往没有严格的限制。

⑥系统更新性能好。因为CPU、存储器、I/O接口等都是按总线规约挂到总线上的,因而只要总线设计恰当,可以随时随着处理器的芯片以及其他有关芯片的进展设计新的插件,新的插件插到底板上对系统进行更新,其他插件和底板连线一般不需要改。

⑦便于故障诊断和维修。用主板测试卡可以很方便找到出现故障的部位。以及总线类型。

缺点

①由于在CPU与主存储器之间、CPU与I/O设备之间分别设置了总线,从而提高了微机系统信息传送的速率和效率。但是由于外部设备与主存储器之间没有直接的通路,它们之间的信息交换必须通过CPU才能进行中转,从而降低了CPU的工作效率(或增加了CPU的占用率。一般来说,外设工作时要求CPU干预越少越好。CPU干预越少,这个设备的CPU占用率就越低,说明设备的智能化程度越髙),这是面向CPU的双总线结构的主要缺点。

②利用总线传送具有分时性。当有多个主设备同时申请总线的使用时必须进行总线的仲裁,分时传输。

③总线的带宽有限,如果连接到总线上的某个硬件设备没有资源调控机制容易造成信息的延时(这在某些即时性强的地方是致命的)。

④连到总线上的设备必须有信息的筛选机制,要判断该信息是否是传给自己的。

总线仲裁(总线判决)

目的是避免多个主控器同时占用总线,确保任何时候总线上最多只有一个模块发送信息:当多个主控模块同时提出总线请求时,仲裁机构以一定的优先算法裁决由哪一个模块获得总线使用权。

按裁决机构的设置

定时查询

定时査询方式中各模块的总线请求信号经一条公共的请求线向控制器发出,控制器轮流对各模块进行测试看是否有请求。

定时查询以计数方式向各模块发出一个计数值COUNT,与计数值相对应的模块如果有总线请求BR(Bus Request),则总线控制器停止计数,响应该模块的总线请求BR,使该模块获得总线使用权,然后该模块发出总线忙BB(Bus Busy)信号并开始总线操作。

各模块的BR和BB“线或”后送往总钱控制器。

总线操作结束,该模块撤除总线忙BB信号,释放总线,控制器继续进行轮询,计数值可从零开始,也可从暂停的值继续。

如果计数值每次都从零开始,各模块的优先级按其对应的序号固定不变,0号优先级最高,序号越大优先级越低。

如果每次都从暂停的计数值继续下去,则所有模块都有相同的机率占用总线,各模块的优先级相等。优先级还可以程序控制,动态改变,灵活性大。定时查询方式可靠性高,模块的故障不会影响总线控制。缺点是扩展性较差。

集中式控制

将总线控制逻辑基本上集中于一个设备,

分布式控制

将总线控制逻辑分散在总线连接的各个部件或设备中。

按裁决方式

串行链接仲裁

串行链接仲裁简称串链仲裁、串行仲裁,又叫“菊花链”仲裁(robin Daisy chaining)。

该仲裁法又有二线菊花链、三线菊花链、四线菊花链之分,其中三线菊花链使用普遍,最具代表性。

三线菊花链使用3根控制线:总线请求BR、总线允许BG(Bus Grant)和总线忙BB,各模块通过OC(集电极开路)门在请求线BR和忙线BB上分别‘线或”(负逻辑),各个模块的BR(或BB)线连在一起,当有一个为低电平时,输入到仲裁器的BR(或BB)即为低电平,这种“负或”的关系若从正逻辑来看则为“正与”,因此也有叫“线与”的。

为了克服三线菊花链仲裁的弊端又保留其优点,出现了循环菊花链(Round robin Daisy chaining)仲裁方法。

循环菊花链仲裁属分布式总线控制,系统中没有集中的总线仲裁器,而将仲裁逻辑分散在各个模块中。

总线允许线BG连到最后一个模块后又返回到第一个模块而形成循环。系统中无论哪个模块被获准接管总线,它就同时兼作当前的总线仲裁器。

可以编程选择任一模块首次访问总线,每个模块的优先权取决于它沿总线允许信号BG传输方向距当前总线控制器的远近,距离越远的优元权越低。

因此在总线传输过程中优先权动态地改变,每个主控模块占用总线的机会均等。每一时刻只有一个模块作为总线通信的实际主控模块。

文章介绍了计算机中的总线特性,包括片内总线、系统总线的地址总线、数据总线和控制总线的作用和信号线数量。总线结构的优点如信息传输效率高、系统模块化设计、易于扩展和更新,但也有缺点,如CPU占用率高、总线仲裁延迟和带宽限制。总线仲裁通过定时查询、集中式控制和分布式控制等方式解决多个主控器的总线使用权问题。

文章介绍了计算机中的总线特性,包括片内总线、系统总线的地址总线、数据总线和控制总线的作用和信号线数量。总线结构的优点如信息传输效率高、系统模块化设计、易于扩展和更新,但也有缺点,如CPU占用率高、总线仲裁延迟和带宽限制。总线仲裁通过定时查询、集中式控制和分布式控制等方式解决多个主控器的总线使用权问题。

3522

3522