一.PLL简介

PLL(phase-locked loop)锁相环,锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号来控制环路内部震荡信号的频率和相位。锁相环拥有强大的性能,可以对输入到 FPGA 的时钟信号进行任意分频、倍频、相位调整、占空比调整和优化抖动等。

MMCM(mixed-mode clock manager)混合模式时钟管理,是一个 PLL 上加入 DCM 的一部分以进行精细的相移,也就是说 MMCM 在 PLL 的基础上加上了相位动态调整功能,又因为 PLL 是模拟电路,而动态调相是数字电路,所以 MMCM 被称为混合模式,

Xilinx7 系列器件中的时钟资源包含了时钟管理单元 CMT( Clock Management Tile)即时钟管理单元),每个 CMT 由一个 MMCM和一个 PLL组成。xc7z020 芯片内部有 4 个 CMT,xc7z010 芯片内部有 2 个 CMT。

二.实验任务

三.PLL IP核配置

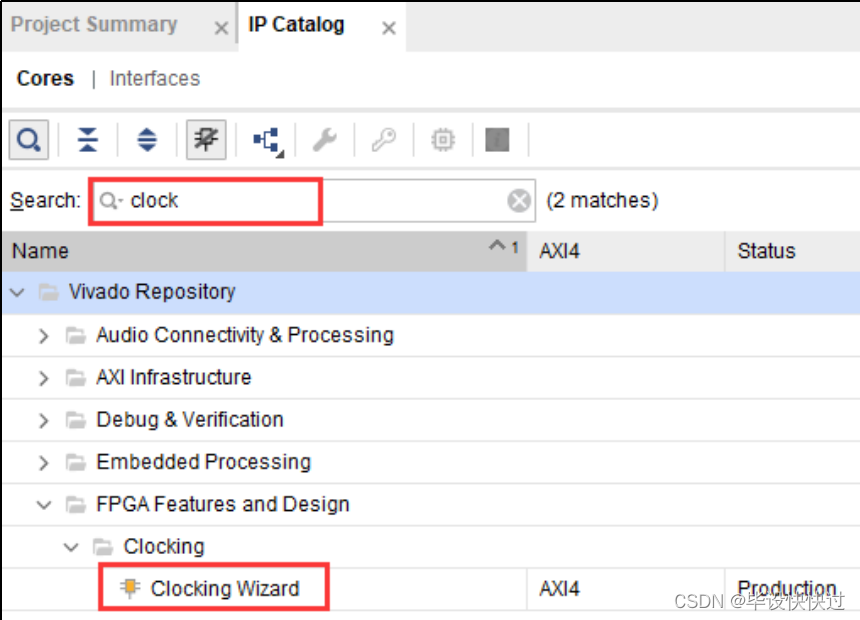

1.在IP catalog中搜索clock,若首次使用相对该IP核做深入了解,可以首先浏览器搜索“xilinx“进入官网,再在官网中搜索IP核选择对应版本文档即可。

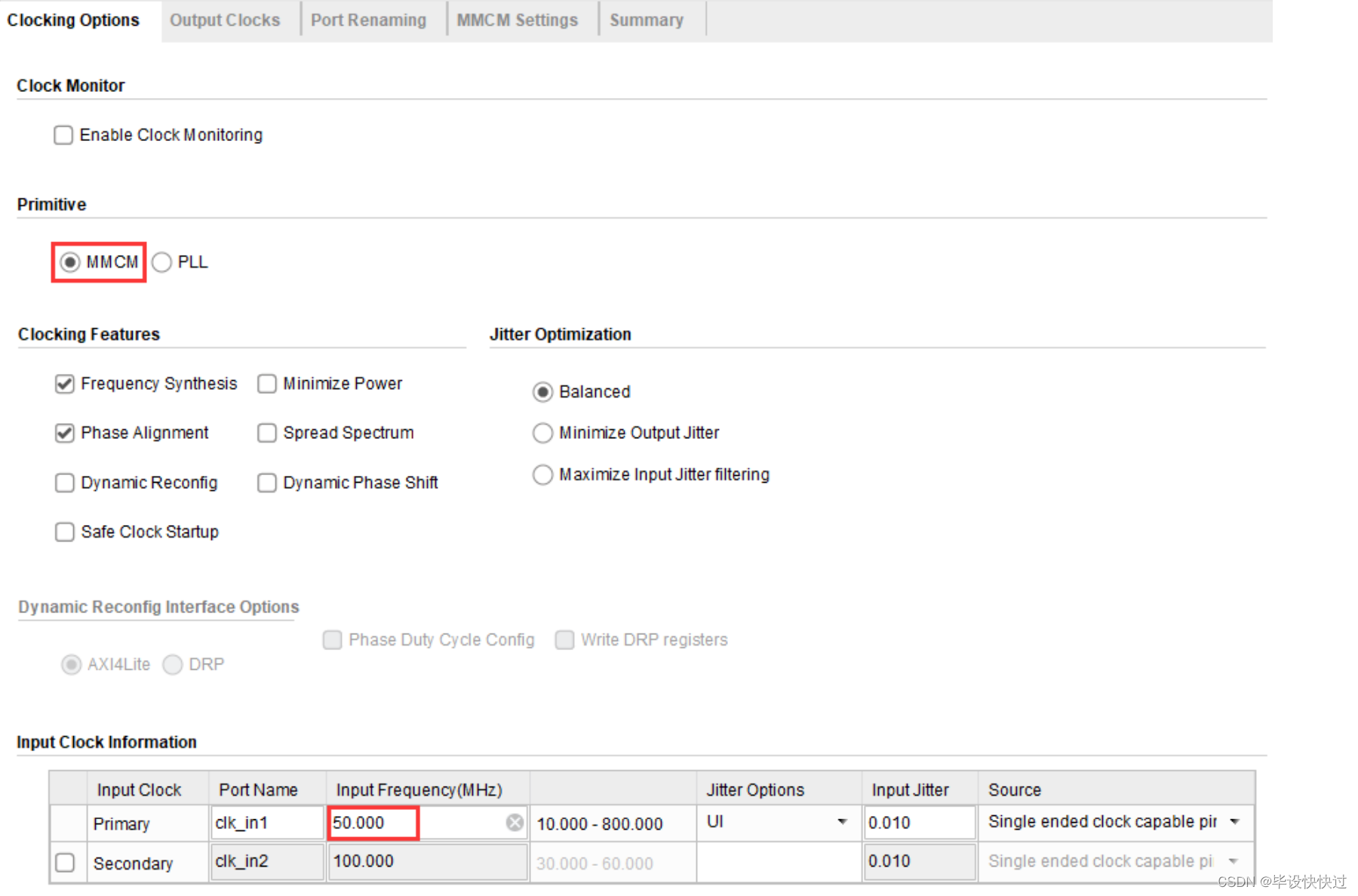

2.因为我们的我们开发板上的晶振频率为 50MHz,所以我们将主时钟的时钟频率设置为 50。

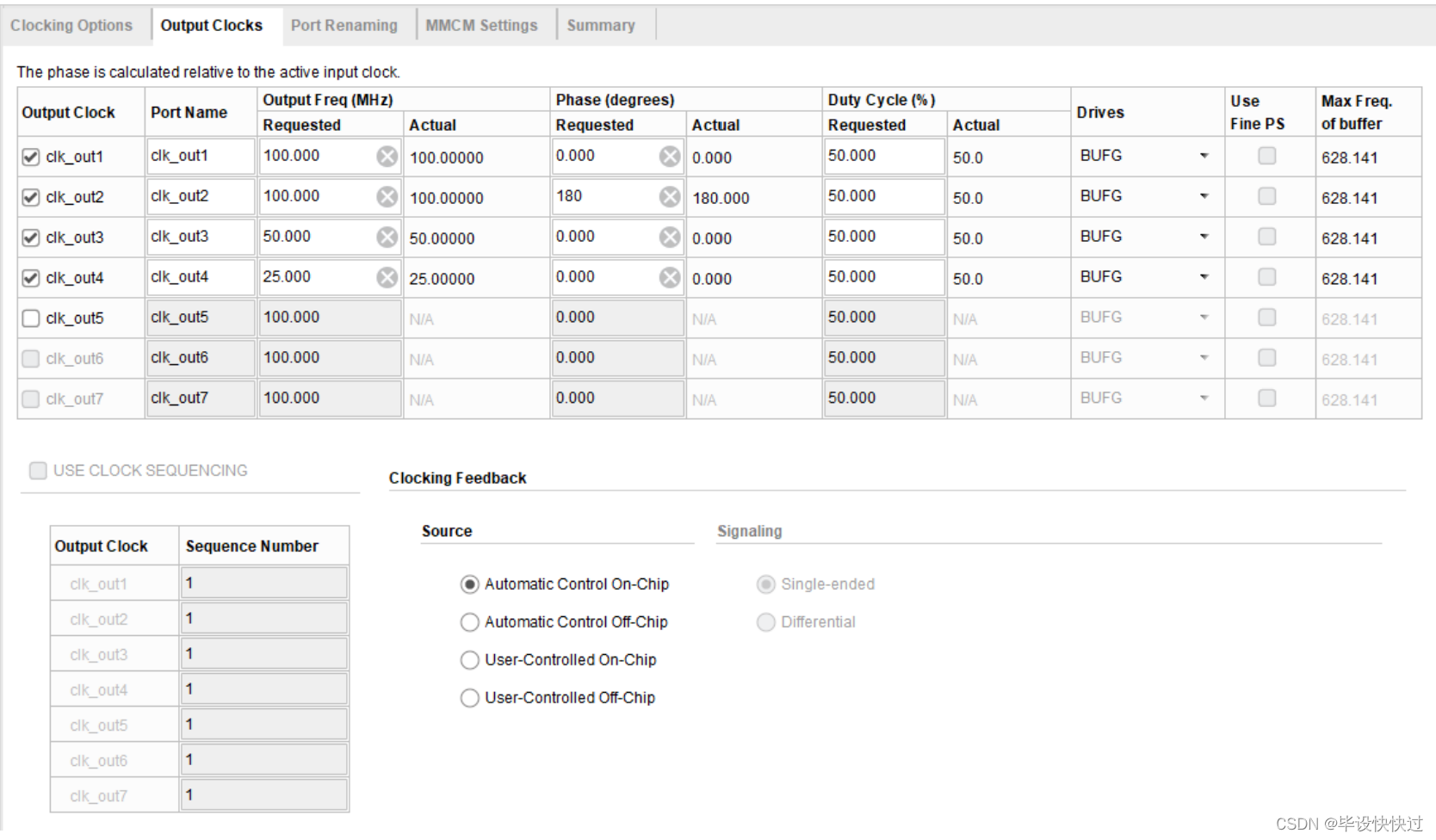

3.因为需要输出四路时钟,因此将各个时钟频率和相位按照要求更改即可。接下来一路”ok“即可。

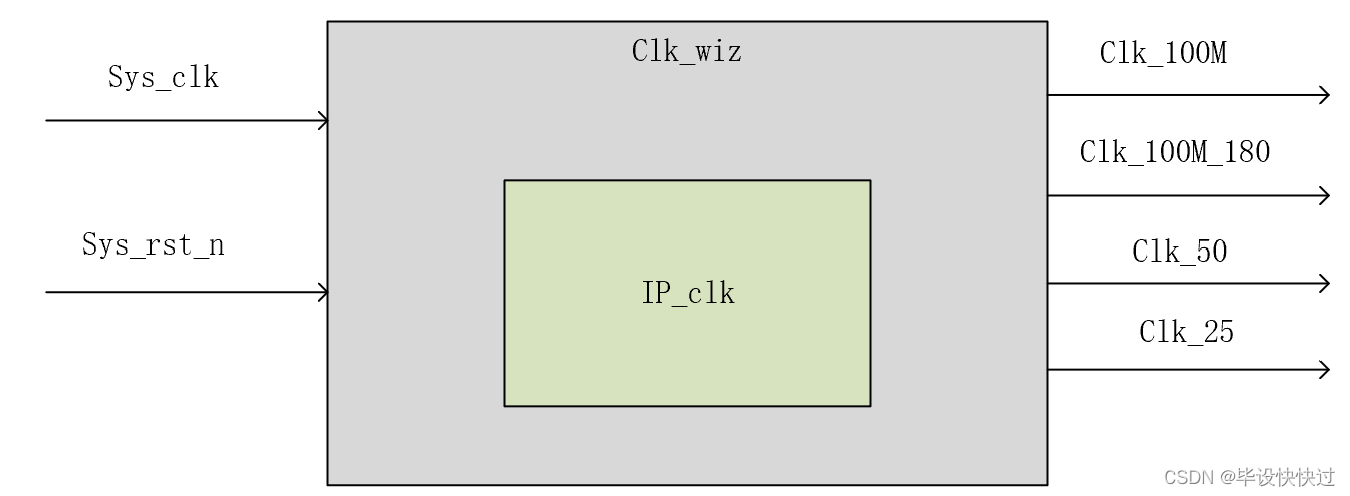

四.模块设计

输入端口里系统复位信号必不可少,其次产生四路时钟的系统时钟必不可少。

五.波形图绘制

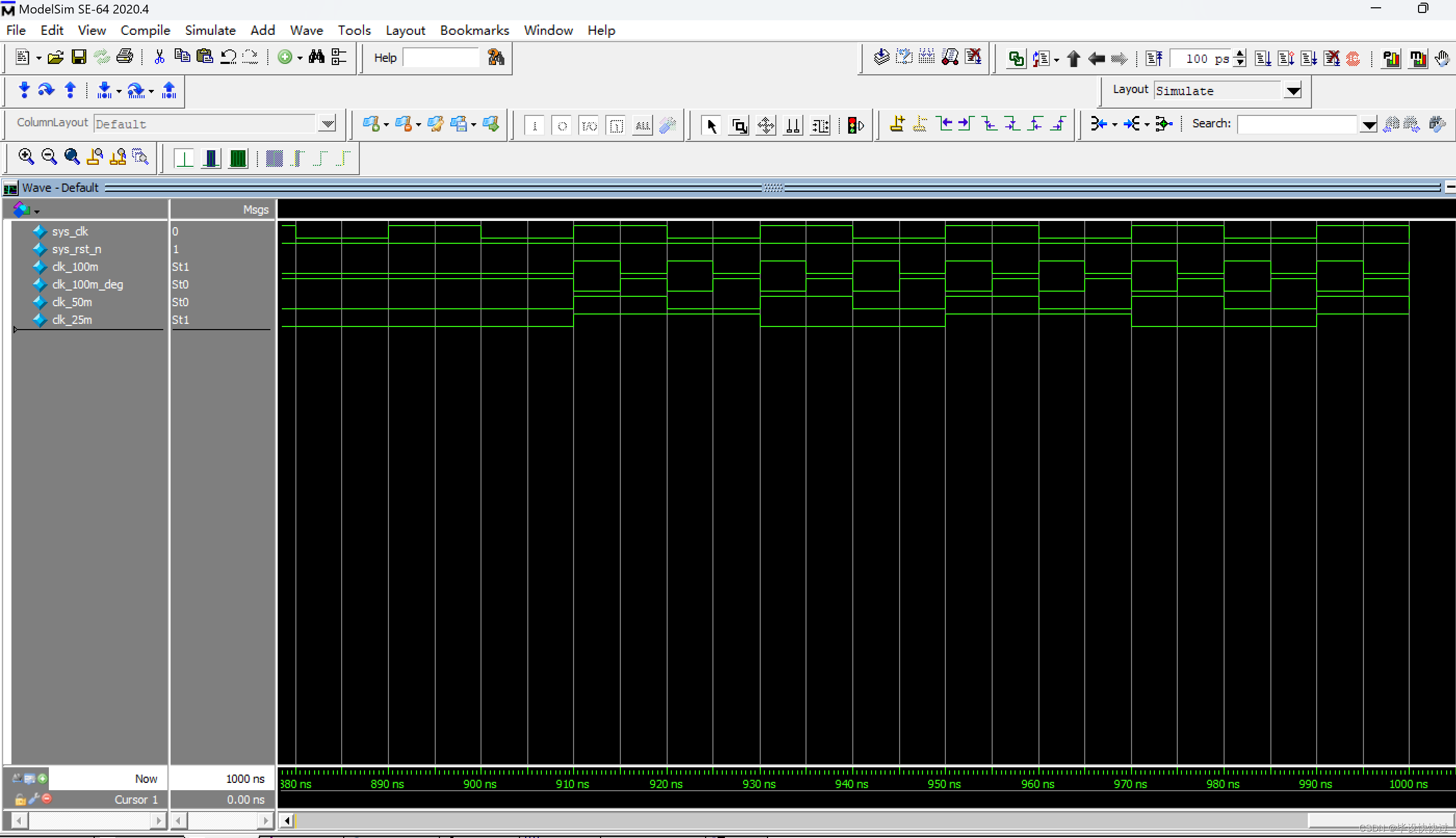

系统时钟是50M,故clk_100m是系统时钟的两倍,周期是其1/2,clk_100m_180在clk_100m的基础上偏移1/2个周期即可。clk50m与系统时钟一致,clk25m周期是clk50的两倍。

六.vivado和modelsim联合仿真验证

观察仿真波形和所设计时波形一致,符合设计要求。

仿真可以分为RTL 行为级仿真、综合后门级功能仿真和时序仿真 。

RTL行为级仿真:在大部分设计中执行的第一个仿真都是 RTL 行为级仿真,用来检查代码中的语法错误以及代码行为的正确性不包含延时信息。

综合后门级功能仿真:一般在设计流程中的第二个仿真是综合后门级功能仿真,绝大多数的综合工具除了可以输出一个标准网表文件以外,还可以输出 Verilog 或者 VHDL 网表,为综合工具给出的仿真网表已经是与生产厂家的器件的底层元件模型对应起来了。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?