话说咸鱼上收了几块性价比很高的屏幕,LVDS接口的8寸屏。加上之前收的几块EBAZ4205矿板,想试试看用矿板驱动。

-

首先研究了下ZYNQ的LVDS接口,但是不幸的是ZYNQ不支持3.3v,只能LVDS25,这样的话就要硬件上改电源。

偶然机会看到国外友人已经成功的用LVDS驱动了屏幕,他们巧妙的用TMDS差分输出,然后用50欧姆上拉到1.5V,然后实现了LVDS电平标准的输出。

这样就不需要更改VCCO电平,很满意,决定效仿。 -

Xilinx Zynq 里面没有专门的LVDS IP, 但是有强大的SelectIO,可以轻松实现串并转换等。可以参考UG471,以及xapp585这些文档和引用。

-

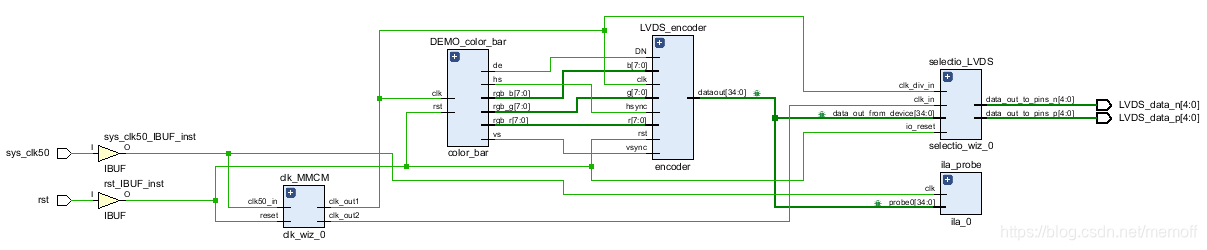

然后就是原理框图,因为我要实现的功能很简单,只是输出一个彩条就行,所以只要一个MMCM模块生成需要的时钟(X1)和Pixel 时钟(X7),然后是彩条模块,产生时序信号。

然后是串行数据编码模块,用于产生标准的LVDS时序, 最后是SelectIO用于串并转换。

本文介绍了如何利用EBAZ4205 FPGA矿板驱动LVDS接口的8寸屏幕。由于ZYNQ不支持3.3v LVDS,作者借鉴了国外的方法,通过TMDS差分输出并上拉到1.5V模拟LVDS电平。借助Xilinx Zynq的SelectIO,实现了串并转换,结合MMCM模块生成所需时钟和彩条模块,最终成功驱动屏幕显示彩条。下一步计划实现HDMI输入。

本文介绍了如何利用EBAZ4205 FPGA矿板驱动LVDS接口的8寸屏幕。由于ZYNQ不支持3.3v LVDS,作者借鉴了国外的方法,通过TMDS差分输出并上拉到1.5V模拟LVDS电平。借助Xilinx Zynq的SelectIO,实现了串并转换,结合MMCM模块生成所需时钟和彩条模块,最终成功驱动屏幕显示彩条。下一步计划实现HDMI输入。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2735

2735