数电,计算机组成原理要写verilog

由于我不需要编写一些大项目, 用vivado就是杀鸡用牛刀了, 不仅慢,还要配置很多地方. 于是我在网上搜索,可以使用iverlog+gtkwave命令行工具

写好各个模块后,开放仿真

$ iverilog -o reg *.v

$ vvp -n reg -lxt2程序正常输出了, 但是没有产生vcd仿真文件,

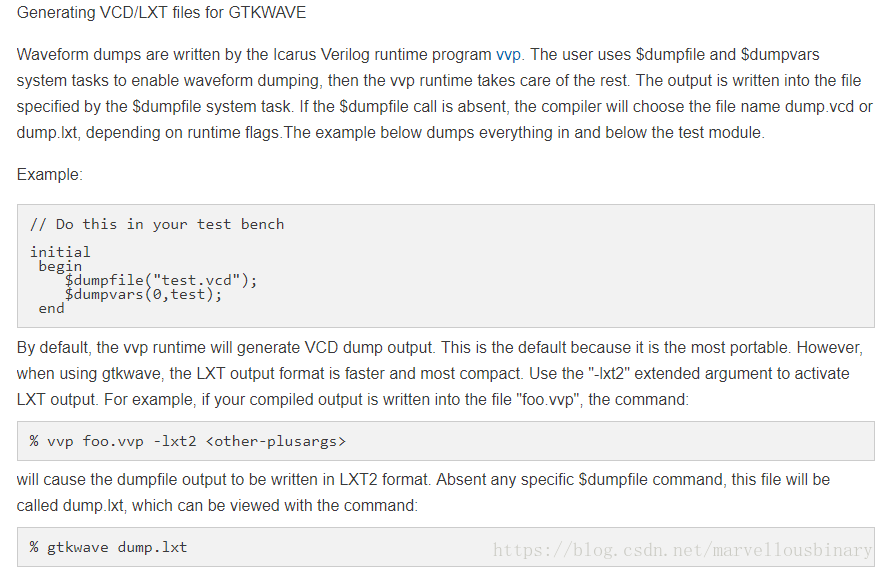

在官网上找到答案

是因为没有在testbench文件中使用命令 dumpfile, d u m p f i l e , dumpvars 所有加上

6 initial begin

7 $dumpfile("reg.vcd");

8 $dumpvars(1,sim);

9 end

10下面是dumpvars的介绍:

我们甚至可以在同一个$dumpvar的调用中,同时指定某些层次上的所有信号和某个单独的信号,假设模块top包含信号signal1,同时包含有子模块module1,如果我们不但希望记录signal1这个独立的信号,而且还希望记录子模块module1以下三层的所有信号,则语法举例如下:

initial $dumpvar (3, top.signal1, top.module1); //指定层次数和单独指定的信号无关 //所以层次数3只作用于模块top.module1, 而与信号 top.signal1无关 上面这个例子和下面的语句是等效的: initial begin $dumpvar (0, top.signal1); $dumpvar (3, top.module1); end $dumpvar的特别用法(不带任何参数): initial $dumpvar; //无参数,表示设计中的所有信号都将被记录

再使用vvp -n reg -lxt2就能产生vcd文件了

继续

$ gtkwave reg.vcd报错

Could not initialize GTK! Is DISPLAY env var/xhost set?

查了很久,

原因是linux下命令行界面要连接一个窗口才能将图形显示出来, $DISPLAY就是这个环境变量, 按网上的说法设置为本机ip:0.0还是没能解决,

而且配置了DISPLAY环境变量而不连接, 其他时候使用, 打开看vim变得很慢, 所以果断去掉

我就只好在windows上下载图形化界面的gtkwave

同上 , 只需在命令行输入(先将gtkwzve的bin目录加入path) gtkwave reg.vcd

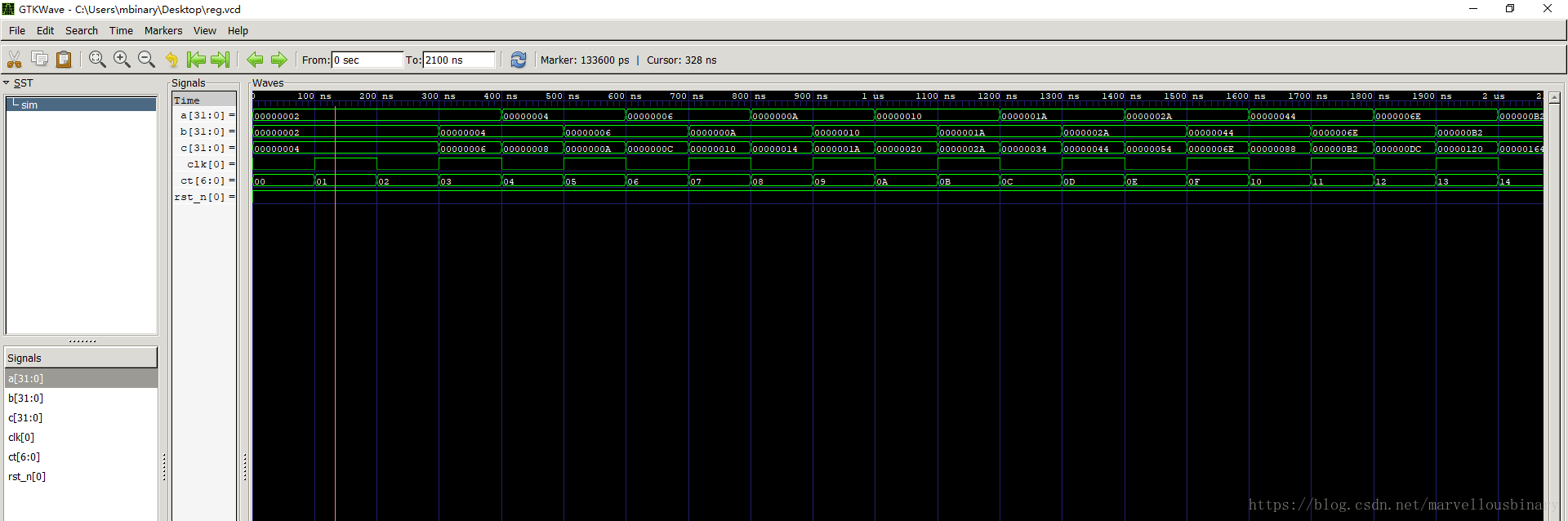

刚进入还没有波形, 需点击左侧上面窗口的sst ,然后选择tb文件, 然后再点左侧下面窗口的变量,全部显示即可

比如这是一个利用regfile, alu 求斐波那契的波形 c=a+b, a=b,b=c;

本文介绍了使用Iverilog和Gtkwave进行Verilog代码仿真的步骤。包括如何生成VCD文件并解决仿真过程中遇到的问题。

本文介绍了使用Iverilog和Gtkwave进行Verilog代码仿真的步骤。包括如何生成VCD文件并解决仿真过程中遇到的问题。

703

703

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?