一、什么是DAC

与ADC相反,DAC为数模转换器。

二、DAC904的重要参数

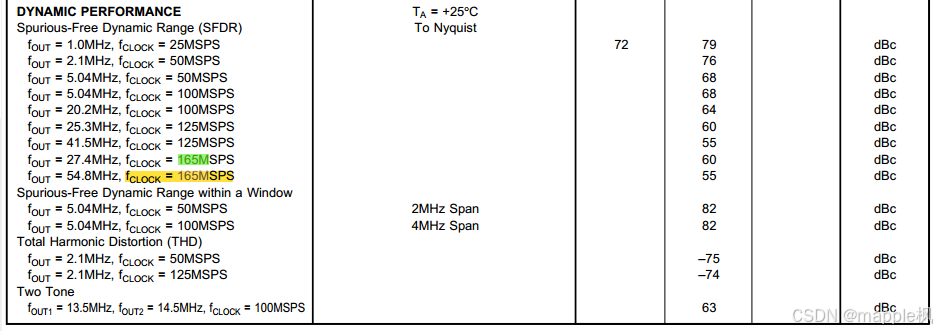

位数14-bit,165MSPS更新速率。

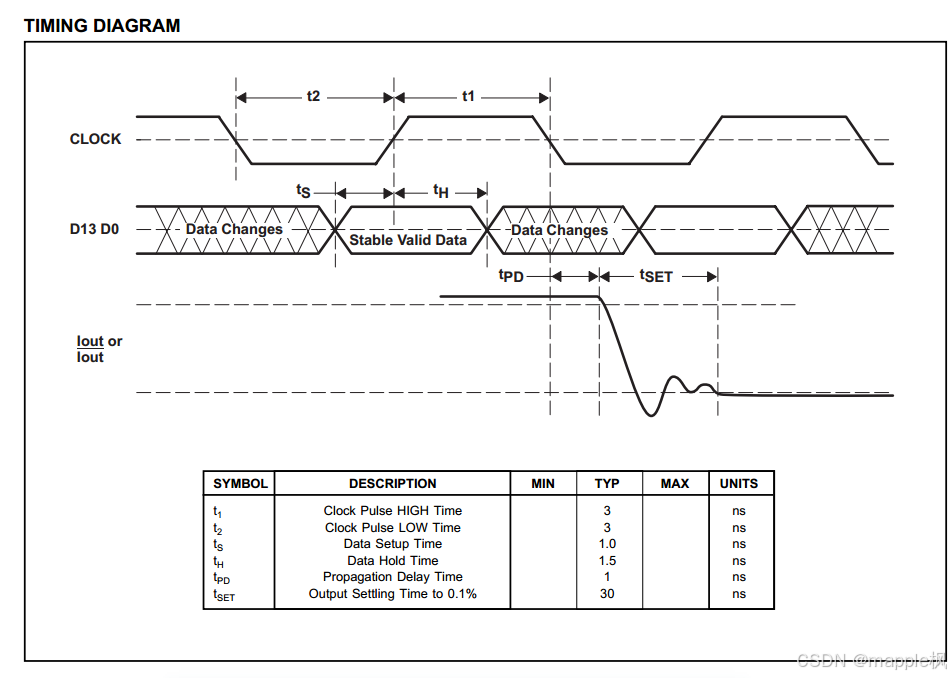

DAC采集时序:

可知一个时钟周期实现转化和保持,转化和保持各半个周期。

供电电压:2.7V~5V

三、DAC904基本原理

1.最大电流输出

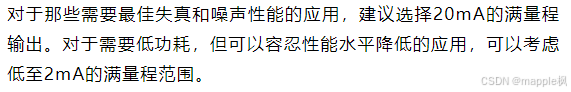

通过选择Rset设置Iref。Rset按照数据手册设置2k,获得最佳失真性能。

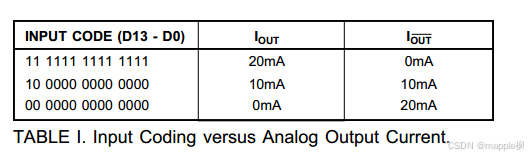

由下面的公式可得此时对应输出的电流和为19.84mA,约为20mA。Rset=20k时,则满量程为2mA。

![]()

2.DAC模拟量和数字量的映射关系。

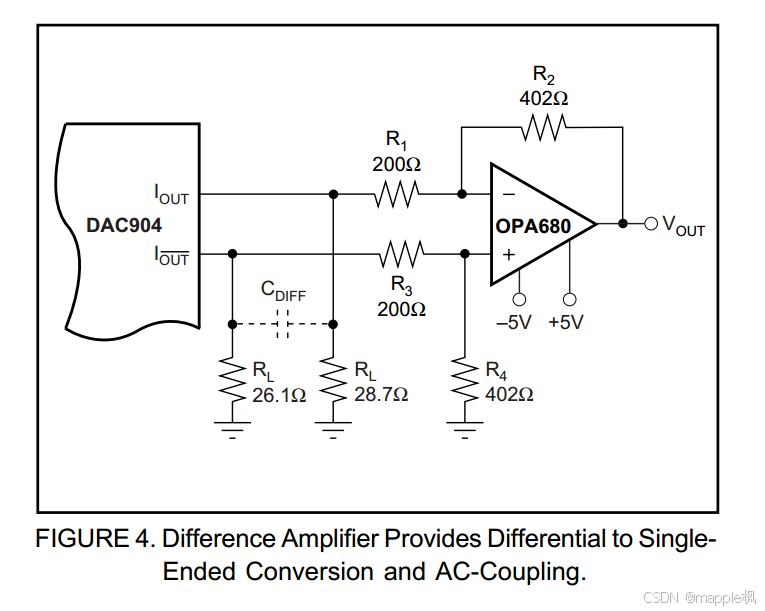

3.差分输出与单端输出。

由于输出电流很小,采用共模抑制噪声。

四、电路设计

设置后级等效负载电阻50欧姆,OPA680的增益配置为2。因此,使用20mA满量程输出操作DAC904将产生±1V(0.02A*50欧姆=1V)的电压输出。这要求放大器在双电源(±5V)下工作。电阻器的容差通常设定了可实现共模抑制的极限。通过微调电阻R4,可以得到改进。

五、布局技巧

适当的接地和旁路、短引线长度和接地面的使用对高频设计尤为重要。多层pc板的性能最好,因为它们具有明显的优势,如接地阻抗最小化,信号层与接地层之间的分离等。

DAC904使用单独的引脚进行模拟和数字电源和接地连接。去耦电容的放置应该使模拟电源(+VA)旁路到模拟地(AGND),数字电源旁路到数字地(DGND)。在大多数情况下,每个电源引脚处的0.1µF陶瓷芯片电容器足以提供低阻抗去耦路径。请记住,它们的有效性在很大程度上取决于与单个电源和接地引脚的接近程度。因此,它们应该在物理上尽可能靠近这些设备引线。只要有可能,电容器应位于PCB板背面的每对电源/接地引脚的正下方。这种布局方法将最大限度地减少组件引线和pcb运行的寄生电感。

进一步的电源去耦与表面贴装钽电容器(1µF至4.7µF)可以根据需要添加在转换器附近。

DAC904的所有电源和接地连接都要求低噪声。建议使用多层电路板,采用单独的电源和接地层。混合信号设计需要特别注意不同电源电流和信号走线的路由。一般来说,模拟电源和地平面应该只延伸到模拟信号区域,如DAC输出信号和参考信号。数字电源和地平面必须限于覆盖数字电路的区域,包括连接到转换器的数字输入线以及时钟信号。模拟和数字地平面应该在DAC下面的一点连接在一起。这可以通过大约1/8英寸(3毫米)的短轨道来实现。

DAC904的电源应该通过使用宽pcb运行或平面来提供。宽运行将呈现较低的走线阻抗,进一步优化电源去耦。转换器的模拟和数字电源只应在pc板的电源连接器上连接在一起(单点连接)。在只有一个电源电压可供DAC供电的情况下,铁氧体磁珠和旁路电容器可用于创建LC滤波器。这将产生一个低噪声模拟电源电压,然后可以连接到DAC904的+VA电源引脚。

在设计布局时,重要的是要保持模拟信号走线与任何数字线分开,以防止噪声耦合到模拟信号路径上。

六、巨人之肩

DAC904 14-Bit 165-MSPS Digital-to-Analog Converter datasheet (Rev. C) (ti.com.cn)

4835

4835

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?