(一)Logisim的下载与安装

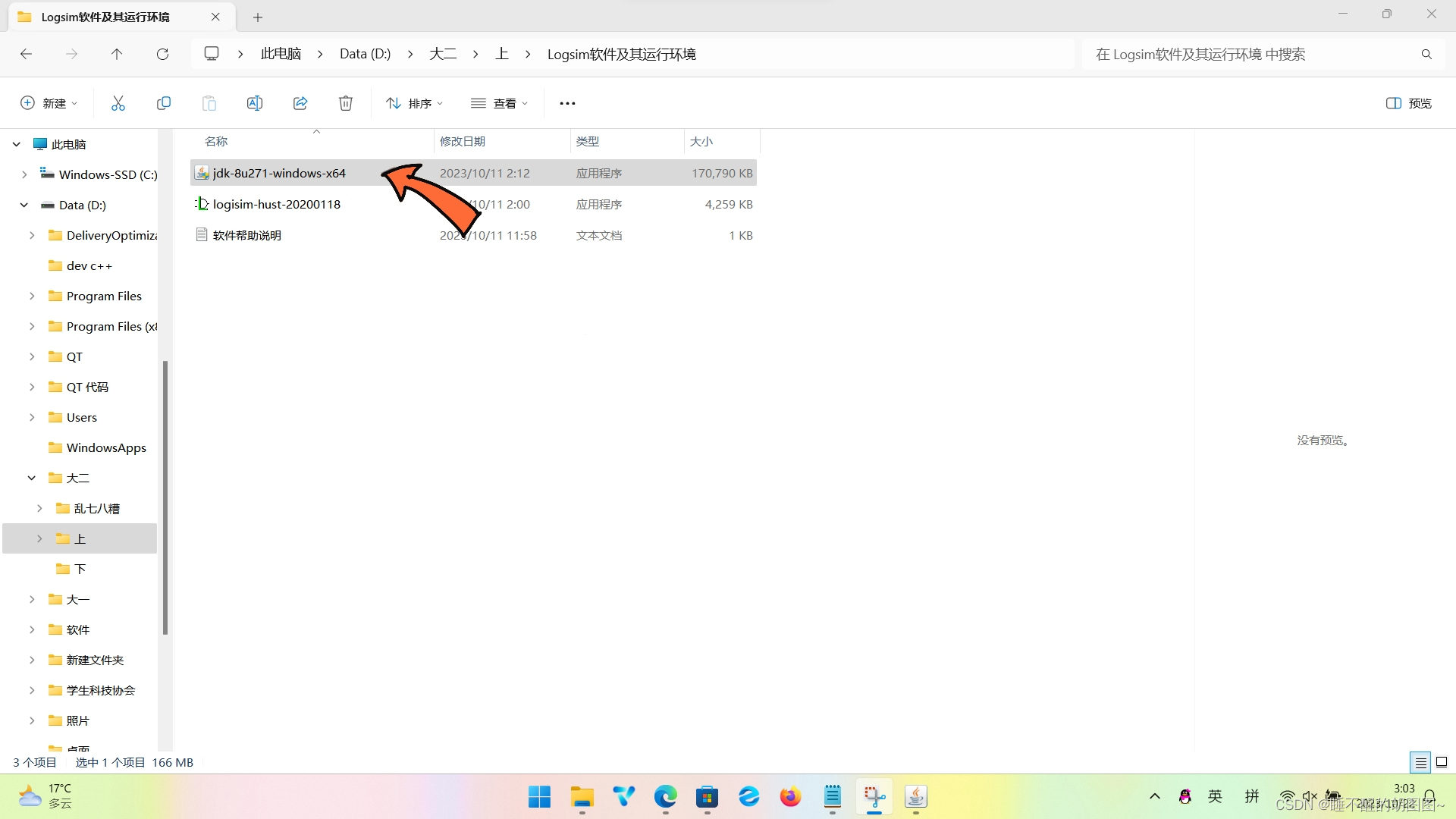

1.安装Java运行环境JDK

先安装JDK软件,默认安装即可

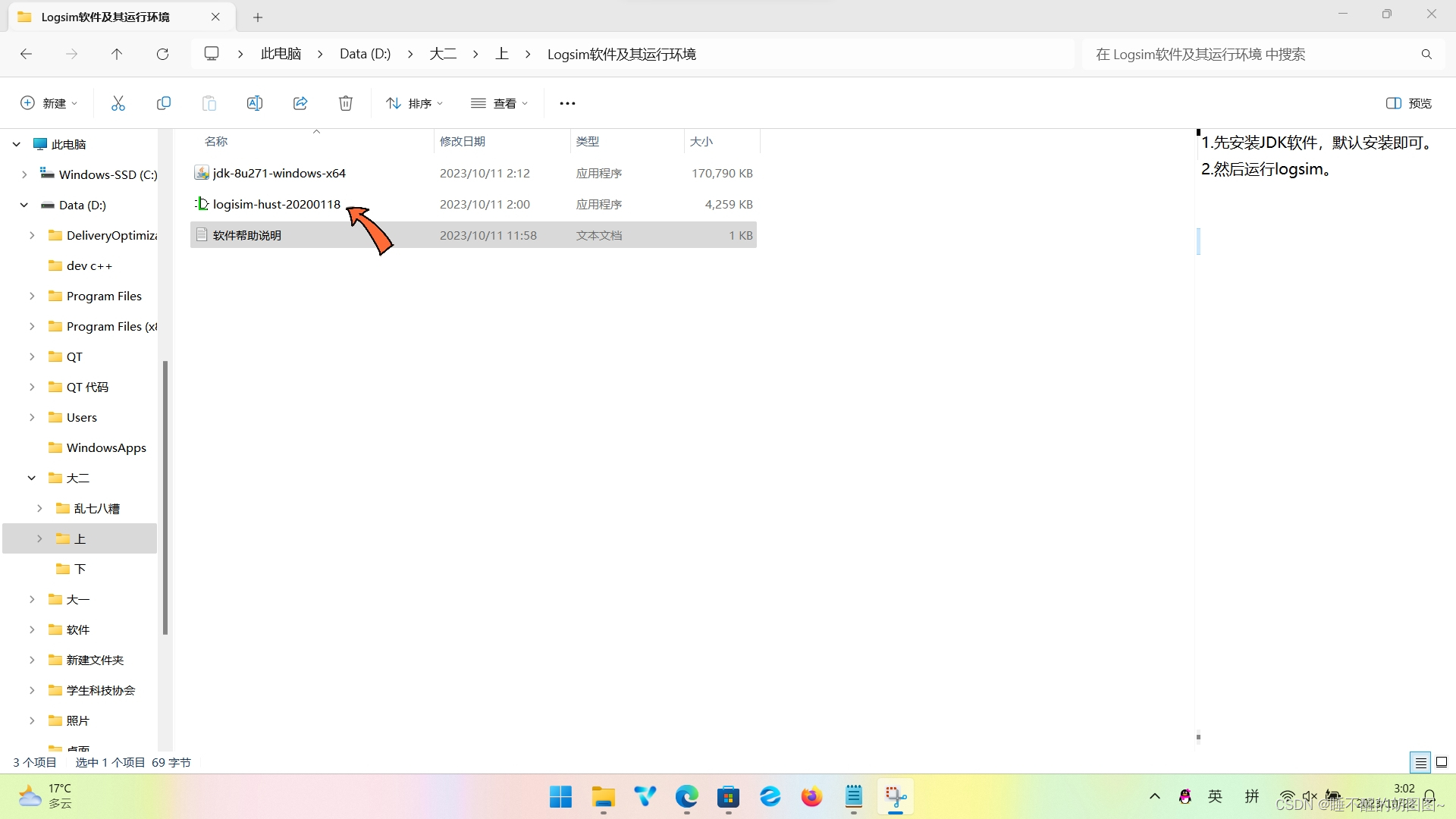

2.下载运行Logisim

2.下载运行Logisim

安装完JDK软件,下载Logisim运行即可)

(二) Logisim设计实现1bit半加器

1.半加器工作原理

半加器的功能是将两个一位二进制数相加。它有两个输入:1、和(S)与进位(C),两个一位二进制数的和用十进制表示即等于2_C+S。半加器的设计是通过一个异或门来产生S,一个与门来产生C实现的。半加器将两个输入加和,产生进位与和,是半加器的两个输出。半加器的输入变量叫做被加数或被加位,输出变量为和与进位。设计半加器后我们可以通过真值表进行验证,半加器真值表如下:

| 输入 | 输入 | 输出 | 输出 |

| A | B | C | S |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

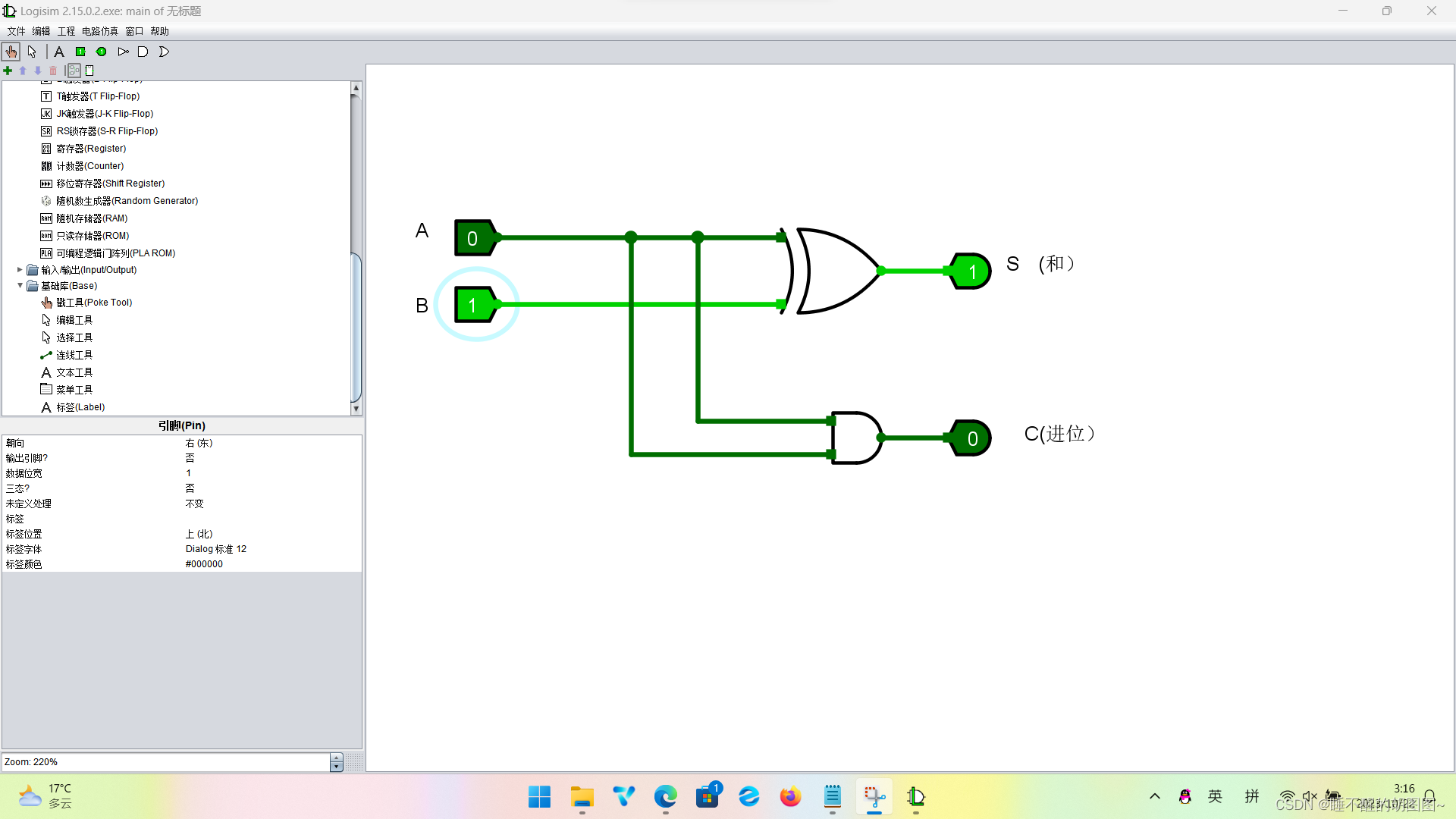

2.用Logisim设计实现半加器

如下图所示,可以通过切换输入值进行验证

(三) Logisim设计实现全加器

1.全加器工作原理

全加器与半加器的不同之处在于它还能接受一个地位进位输入信号Cin,全加器将两个一位二进制数相加,并根据接收到的进位信号,输出和、进位。全加器的三个输入信号为两个加数A、B和低位进位CIn,通常可以通过级联的方式,构成多位(如8位、16位、32位)二进制数加法器的基本部分。全加器输出和半加器类似,包括向高位的进位信号Cout和本位的和信号S,相加结果的总和用十进制表达为:Sum=2×Cout+S。同样设计完全加器后我们也可以通过真值表进行验证,全加器真值表如下:

| 输入 | 输入 | 输入 | 输出 | 输出 |

| A | B | Cin | Cout | S |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

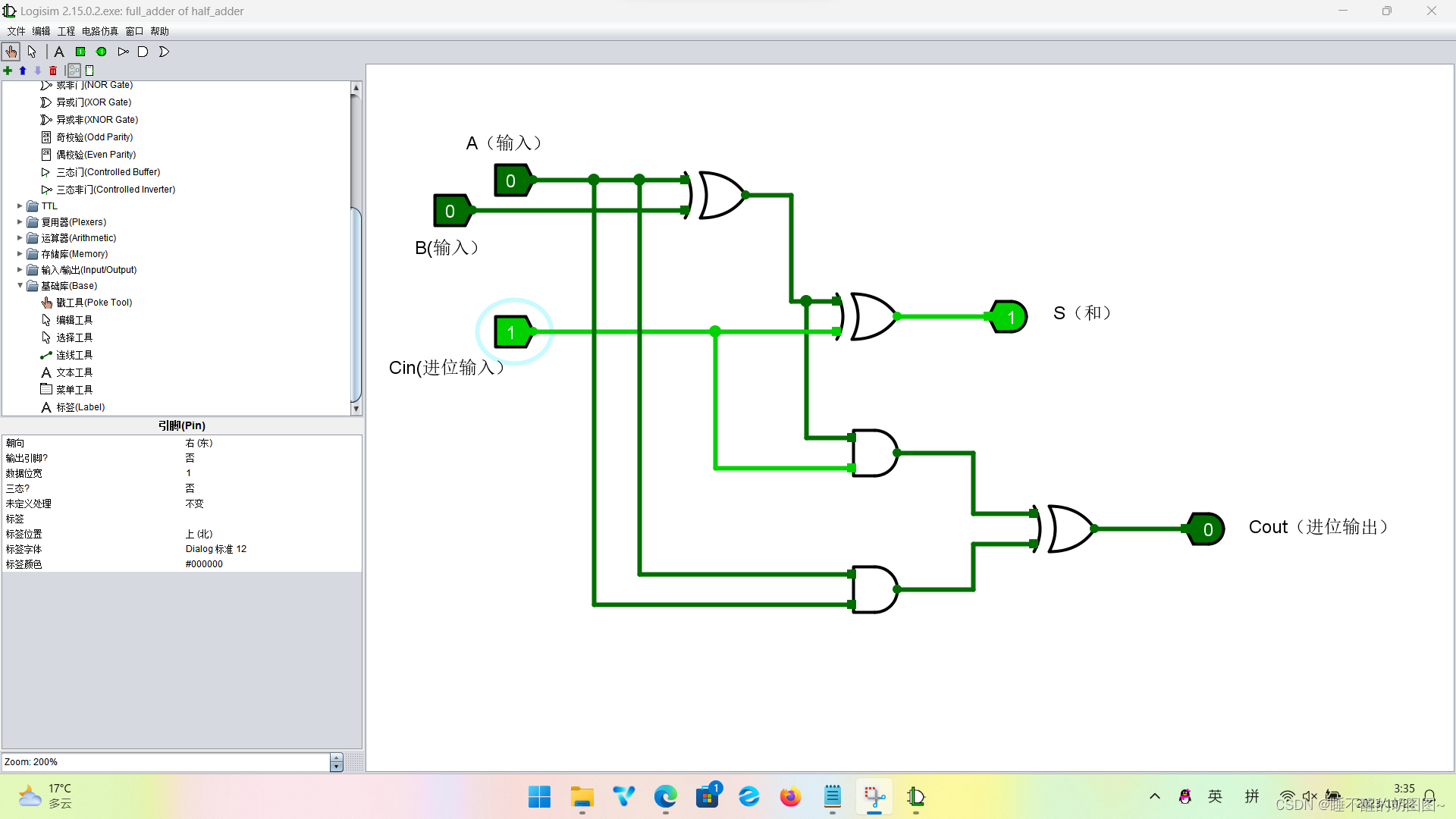

2.用Logisim设计实现全加器

如下图所示,可以通过切换输入值进行验证

(四)用Logisim设计实现一个4位二进制数的补码器电路

(四)用Logisim设计实现一个4位二进制数的补码器电路

1.补码原理

(1)、正数与原码相同

(2)、负数的补码,将其原码除符号外的所有位取反(0变1,1变0,符号位为1不变)后加1.同一个数字在不同的补码表示形式中是不同的。比如:10进制数值-15的二进制原码是10001111,其补码在8位二进制中是11110001,然而在16位二进制补码表示中,不足位数要用符号位补全,也就是1111111111110001.正数和负数的补码运算规则不一样,取决于输入二进制数的最高位(符号位)。

2.输入为负数的补码情况

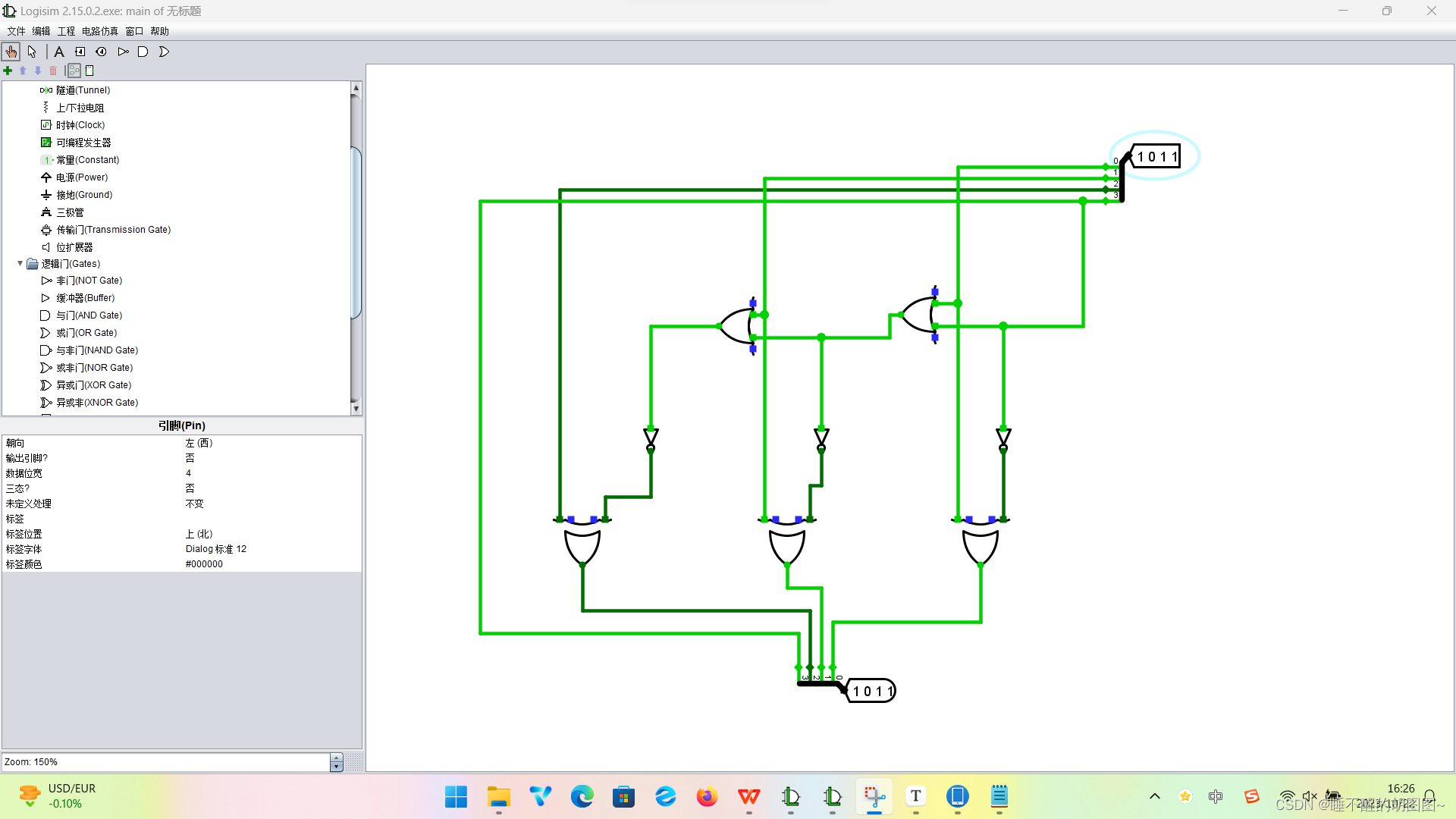

负数的符号位为1,将后三位数字分别通过一个非门取反,补码器电路如下图所示(1011的补码为1101)

3.4位二进制数的补码情况

3.4位二进制数的补码情况

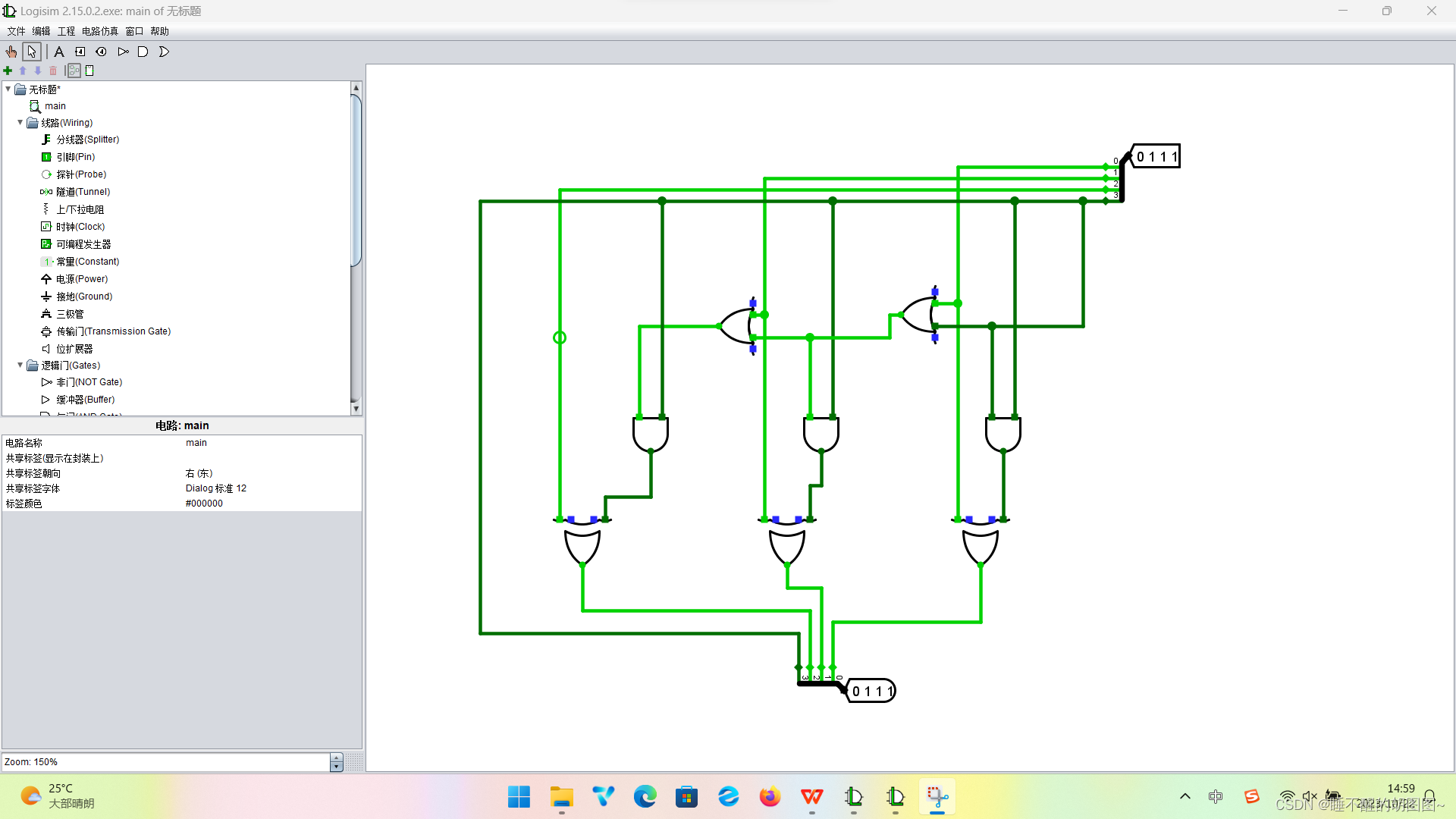

补码器电路如下图所示(0111的补码为0111)

9813

9813

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?