计算机系统概述

计算机的发展历程

-

计算机硬件的发展

电子管时代 --> 晶体管时代 --> 中小规模继承电路时代 --> 超大规模集成电路时代

-

计算机元件的更新换代

-

摩尔定律:当价格不变时,集成电路可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也提升一倍。(18个月后的CPU性能是现在的两倍)

-

半导体存储器的发展

-

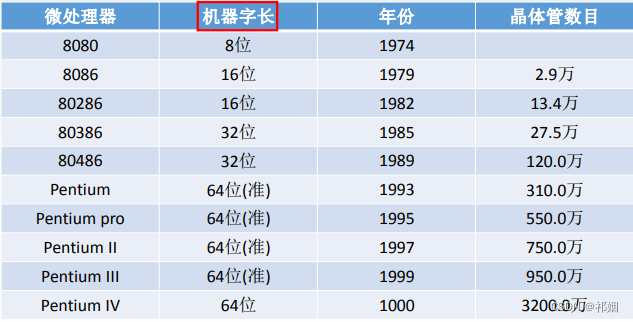

微处理器的发展:标志了微型计算机的发展

机器字长:计算机一次整数运算所能处理的二进制位数

操作系统位数:其 所依赖的指令集的位数

-

-

计算机软件的发展

-

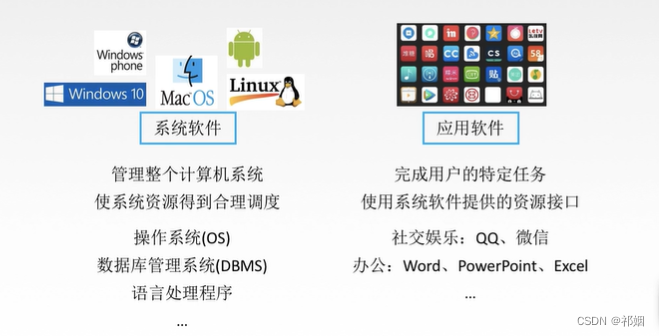

发展经历:面向机器语言(机器语言、汇编语言) --> 面向问题的高级语言

-

机器语言:二进制代码,唯一可以直接执行的语言

-

汇编语言:用助记符编写,以便记忆

-

正则语言:编译原理中符合正则文法的语言

-

-

高级语言的发展真正促进了软件的发展

科学计算和工程计算的FORTRAN --> 结构化程序设计的PASCAL --> 面向对象C++ --> 适应网络环境Java

-

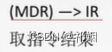

系统软件的发展(直接影响计算机性能提升),尤其是操作系统(Windows、UNIX、Linux等)

-

只有当程序执行时才将源程序翻译成机器语言,并且一次只能翻译一行语句

- 解释程序:翻译一句执行依据,边翻译边执行

- 编译程序:将高级语言的源程序全部语句一次全部翻译成机器语言程序再执行

- 编译:由高级语言转化为汇编语言

- 汇编:把汇编语言源程序翻译成机器语言程序

-

-

计算机的分类与发展方向

-

电子计算机、数字计算机、通用计算机

-

按指令和数据流:

-

单指令流和单数据流系统(SISD):冯诺依曼体系结构

-

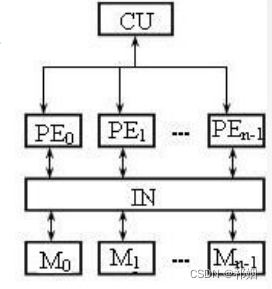

单指令流和多数据流系统(SIMD):阵列处理器、向量处理器

-

多指令流和单数据流系统(MISD):实际上不存在

-

多指令流和多数据流系统(MIMD):多处理器、多计算机

-

-

发展趋势:两极分化

-

微型计算机:更微型化、网络化、高性能、多用途

-

巨型机:巨型化、超高速、并行处理、智能化

-

-

计算机系统层次结构

计算机系统的组成

- 硬件系统和软件系统

- 计算机系统性能的好坏,很大程度上由软件的效率和作用来表征

- 软硬件在逻辑上是等效的(某一功能可以用软件实现也可以用硬件实现)

计算机硬件的基本组成

-

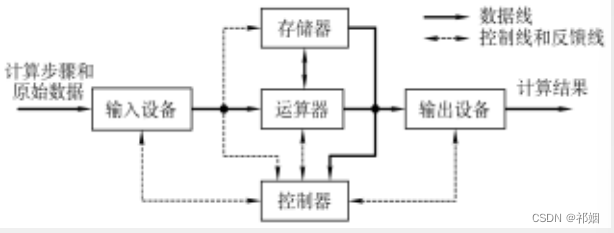

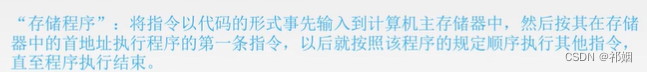

早期的冯·诺依曼机:“存储程序”的思想奠定了现代计算机的基本结构

-

计算机硬件系统由运算器、存储器、控制器、输入设备和输出设备组成

-

指令和数据以同等地位存储在存储器中,并可以按地址寻访

-

指令和数据均用二进制代码表示

-

指令由操作码和地址码组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置

-

指令在存储器内按顺序存放,通常是顺序执行的

-

早期的冯·诺依曼机以运算器为中心,输入/输出设备通过运算器与存储器传送数据

-

-

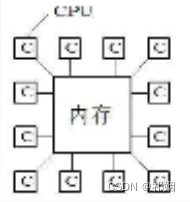

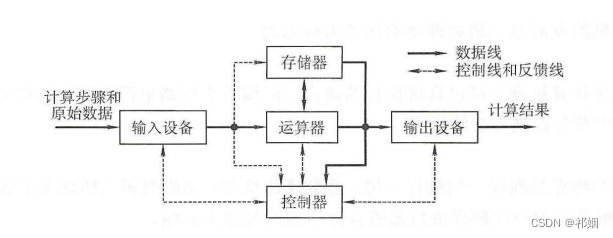

现代计算机的组织结构

以存储器为中心,使I/O操作尽可能绕过CPU,直接在I/O设备和存储器之间完成

目前大多数现代计算机仍遵循冯·诺依曼存储程序的设计思想

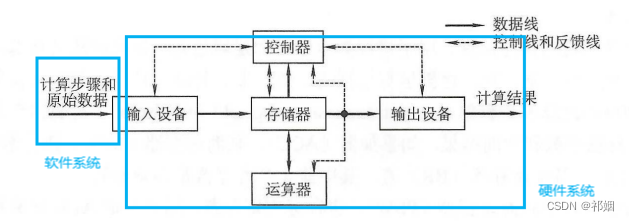

计算机的功能部件

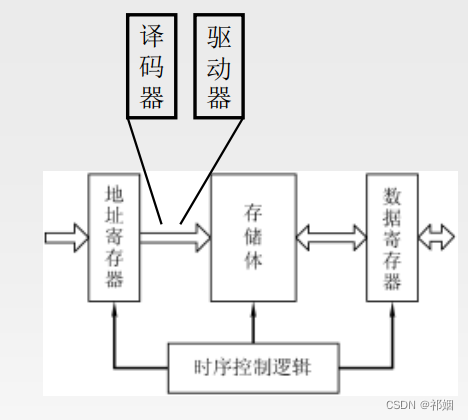

存储器

-

用来存放程序和数据

-

分为主(内)存储器和辅助(外)存储器,CPU能够直接访问的存储器是主存储器,辅助存储器中的信息必须调入主存后,才能为CPU所访问

-

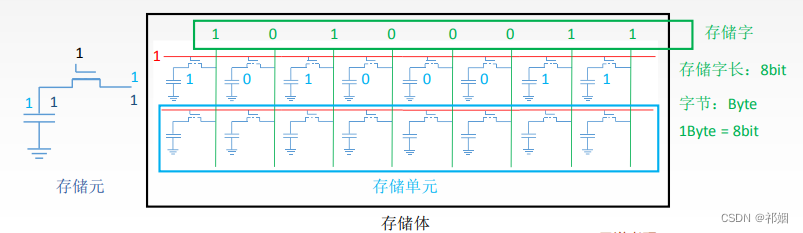

主存储器由许多存储单元组成,每个存储单元包含若干存储元(件),每个存储元(件)存储一位二进制代码

0或1。因此存储单元可存储一串二进制代码,成为这串代码为存储字,这串代码的位数为存储字长。

b:bit 一个二进制位 B:Byte字节,八个二进制位

-

主存储器是按存储单元的地址进行存取,相联存储器是按照内容访问的

-

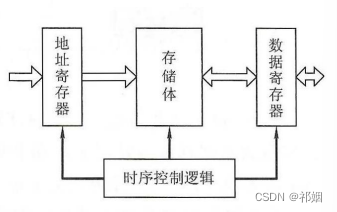

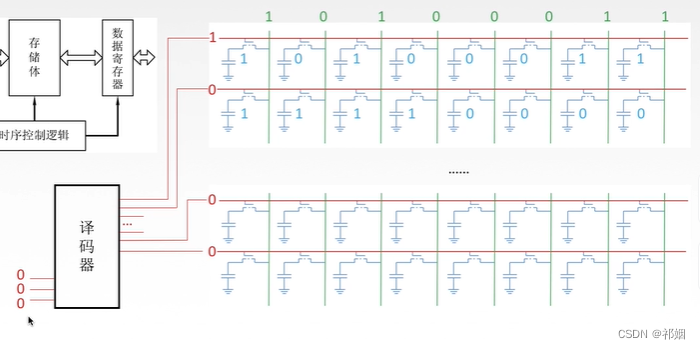

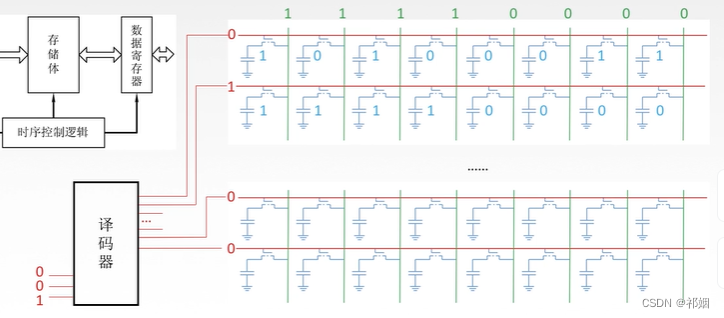

主存储器的最基本组成:

-

存储体:存放二进制信息

-

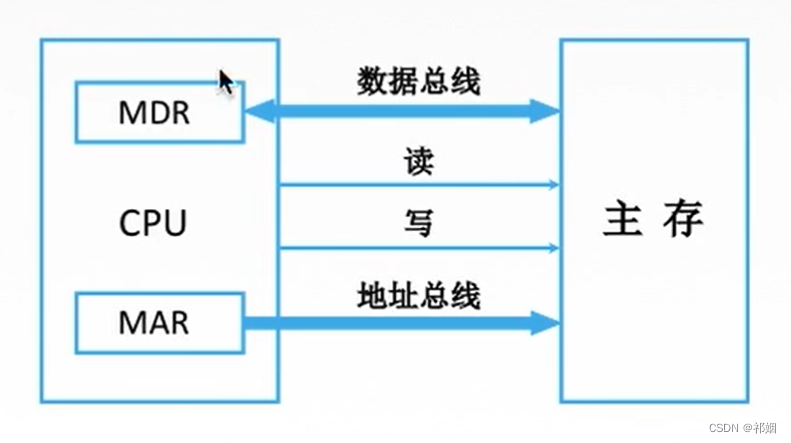

地址寄存器(MAR):存放访问地址,经过地址译码后找到所选的存储单元

MAR位数反映存储单元的个数(最多支持多少个),反应可寻址范围的最大值(而不一定是实际存储器的存储容量)

如MAR为10位(即10个二进制位),则有 2 10 = 1024 2^{10}=1024 210=1024个存储单元,记为 1 K 1K 1K

-

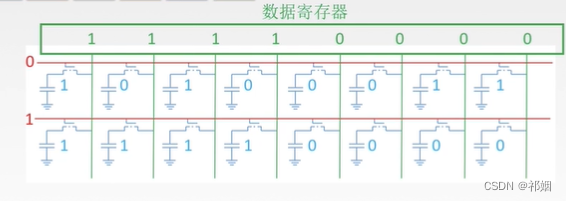

数据寄存器(MDR):暂存要从存储器中读或写的信息

MDR位数=存储字长=每个存储单元的大小

-

时序控制逻辑:产生存储器操作所需的各种时序信号

-

-

总容量=存储单元个数x存储字长 bit=存储单元个数x存储字长/8 Byte1 Byte = 8 bit例:MAR为32位,MDR为8位,总容量 = 2 32 ∗ 8 b i t = 4 G B =2^{32}*8 bit = 4GB =232∗8bit=4GB

-

补充

1 K = 1024 B = 2 10 B 1 K=1024 B=2^{10} B 1K=1024B=210B 2 20 : M 2^{20}:M 220:M 2 30 : G 2^{30}:G 230:G 2 40 : T 2^{40}:T 240:T

-

存储原理

-

某一行前数字为1,表示读取这一行,其余行均为0

-

将这一串只能有一个位为1的数字,经过译码器,转换成可以自由取0和1的数字(即地址),例如此时有8行,只需三根线即可表示出8种状态。如下图是输出第一行/第二行的情况。

n位地址 --> 2 n 2^n 2n个存储单元

问:这里存储多少二进制位?

答:总容量=存储单元个数x存储字长=8*1Byte=8B

-

-

存储器结构补充

-

MAR与MDR虽是存储器的一部分,但常存在于CPU中

-

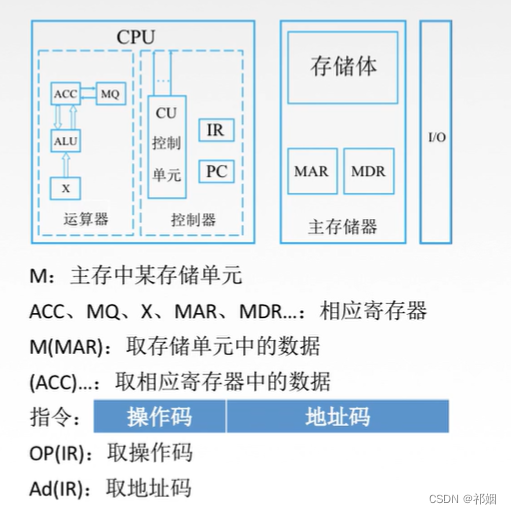

CPU及其工作过程

1.

-

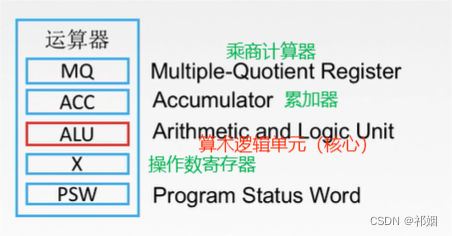

运算器(组合逻辑)

-

用于进行算术运算(加减乘除)和逻辑运算(与、或、非、异或、比较、位移等)

-

-

-

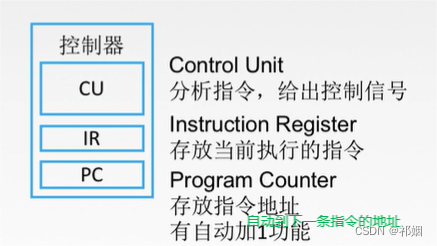

控制器(时序逻辑)

-

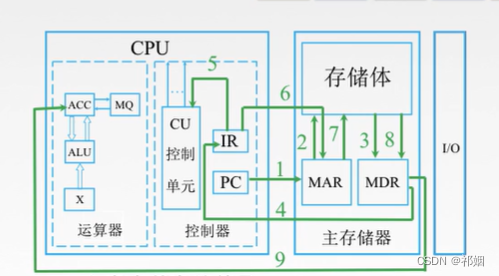

工作过程

-

取数指令

符号规定:

-

首先,主存取PC中下一条指令的内容:

(PC) —> MAR -

而后,在存储体中找到地址所对应的位置,而后写到MDR中:

M(MAR) —> MDR -

再将MDR中内容放到指令寄存器(IR)中:

(MDR) —> IR,取指令结束 -

将操作码放入控制单元以解析:

OP(IR) —> CU,分析指令结束 -

按照地址码寻找存储体中数的位置:

Ad(IR) —> MAR,M(MAR) —> MDR -

将数据放置到累加器中:

(MDR) —> ACC,执行指令结束

-

-

图示

-

CPU区分指令和数据的依据:指令周期的不同阶段

-

IO设备

软件系统 & 编程语言

- 软件:系统软件、应用软件

- 计算机编程语言

计算机的性能指标

-

机器字长:计算机进行一次整数运算所能处理的二进制数据的位数

-

数据通路带宽:数据总线(这里指连接CPU和其他)一次所能并行传送信息的位数

-

主存容量:总容量=存储单元个数x存储字长

-

运算速度

-

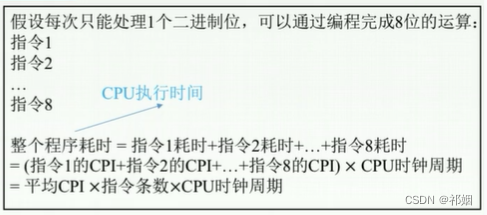

程序(指令)耗时计算:

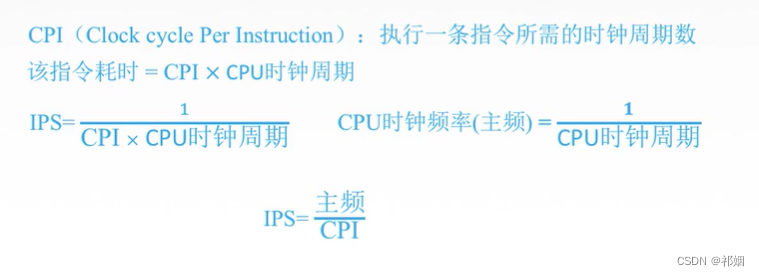

CPU始终频率(主频)=1/CPU时钟周期CPI:执行一条指令所需的时钟周期数

该指令耗时=CPI*CPU时钟周期

-

MIPS:每秒执行多少百万条指令

MIPS=指令条数/(执行时间*10^6)=主频/CPI

-

MFLOPS,每秒执行多少百万次浮点运算

MFLOPS=浮点操作次数/(执行时间*10^6) -

GFLOPS,每秒执行多少十亿次浮点运算

MFLOPS=浮点操作次数/(执行时间*10^9) -

TFLOPS,每秒执行多少百万次浮点运算

MFLOPS=浮点操作次数/(执行时间*10^12)

-

-

吞吐量:系统在单位时间内处理请求的数量,主要屈居于主存的存取周期

-

响应时间

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?