1.生成mcs文件

01.在vivado里的菜单栏选择"tools"工具栏

02.在"tools"里选择"生成内存配置文件"

03.配置参数

按照FPGA板上的flash型号进行选型,相关配置步骤可参考下图。

注意:Flash数据传输位宽如果需要选择X4位宽,则需要对FPGA工程的xdc文件添加约束重新生成bit文件后才可以选择生成X4位宽mcs文件(约束代码见05步骤),不然生成mcs会失败,X1位宽则不用考虑约束(X4位宽的mcs文件FPGA上电后Flash烧写更快,而且x4模式下生成的mcs文件比X1模式下生成的mcs文件要小很多,可以少占用Flash内存;具有占用Flash内存少,上电后烧写速度更快的特点)

04.MCS文件生成

点击"OK"按钮后就会在03步的生成文件路径下找到生成的mcs文件和prm文件。

05.X4位宽MCS文件约束

Flash数据传输位宽如果需要选择X4位宽,则需要对FPGA工程的xdc文件添加约束重新生成bit文件后才可以选择生成X4位宽mcs文件。

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.SPI_FALL_EDGE yes [current_design]添加的约束作用介绍:

set_property CFGBVS VCCO [current_design]

设置 FPGA 配置引脚的参考电压源为 VCCO,确保与外部器件的电平兼容。

set_property CONFIG_VOLTAGE 3.3 [current_design]

设置 FPGA 配置接口的工作电压为 3.3V,需与外部设备(如 SPI Flash)的工作电压匹配。

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

启用比特流压缩,减小比特流文件大小,加快配置速度。

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

设置配置时钟频率为 50 MHz,需与配置器件的时钟速率能力相匹配。

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

设置 SPI 配置模式为 Quad SPI(四线模式),以提高比特流传输速度。

set_property BITSTREAM.CONFIG.SPI_FALL_EDGE yes [current_design]

指定 SPI 时钟在下降沿采样数据。需要与外部 SPI Flash 的工作模式匹配。2.烧写mcs文件

01.连接FPGA板

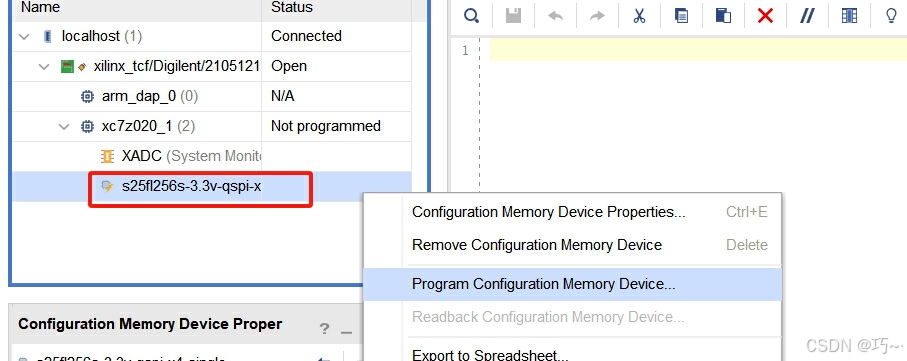

02.添加flah

连接后无flash设备

添加配置内存设备(flash)

选型(选择和生成mcs文件时选择的flash型号)

03.选择mcs文件进行烧写

若01步连接FPGA板打开后有flash设备就不用再添加flash,可直接烧写mcs文件

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?