为什么要五级流水线设计?

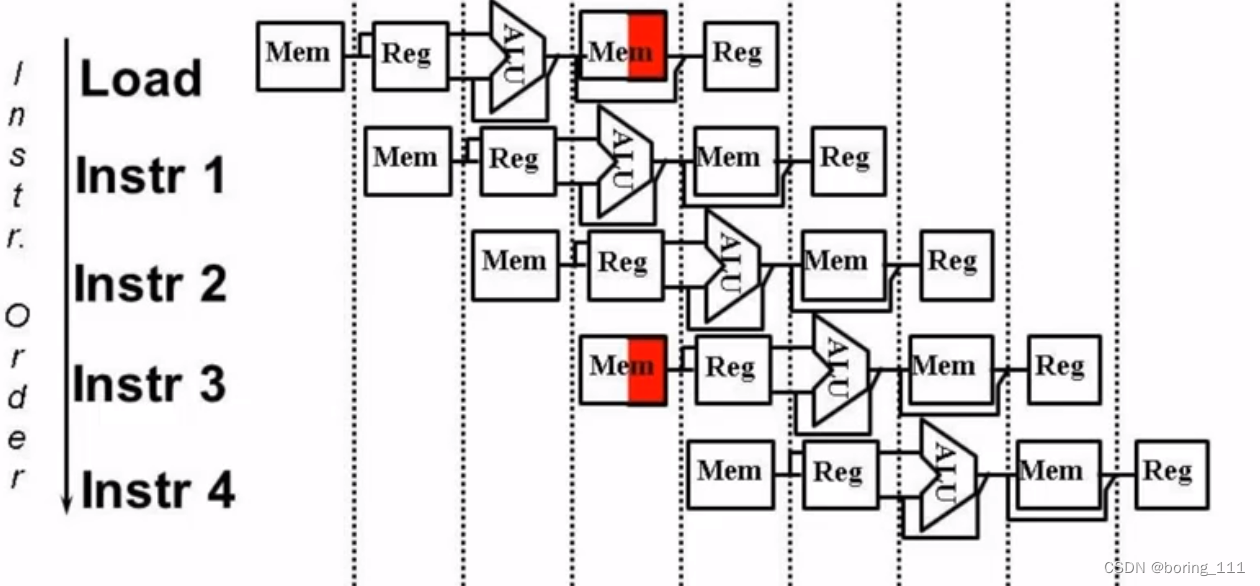

因为为了更好的利用资源,进行pipeline,提高throughput。所以切分成5个部分(memory分成instruction和data两种memory,减少了竞争)

设计上的挑战:Hazard(冒险)

结构上的structural

同一个clock上有两个instruction在使用同一的资源。解决:MIPS每个instruction都有5个stage,因为开始时间不同,使用就解决了冒险。memory分成instruction和data两种memory,减少了竞争

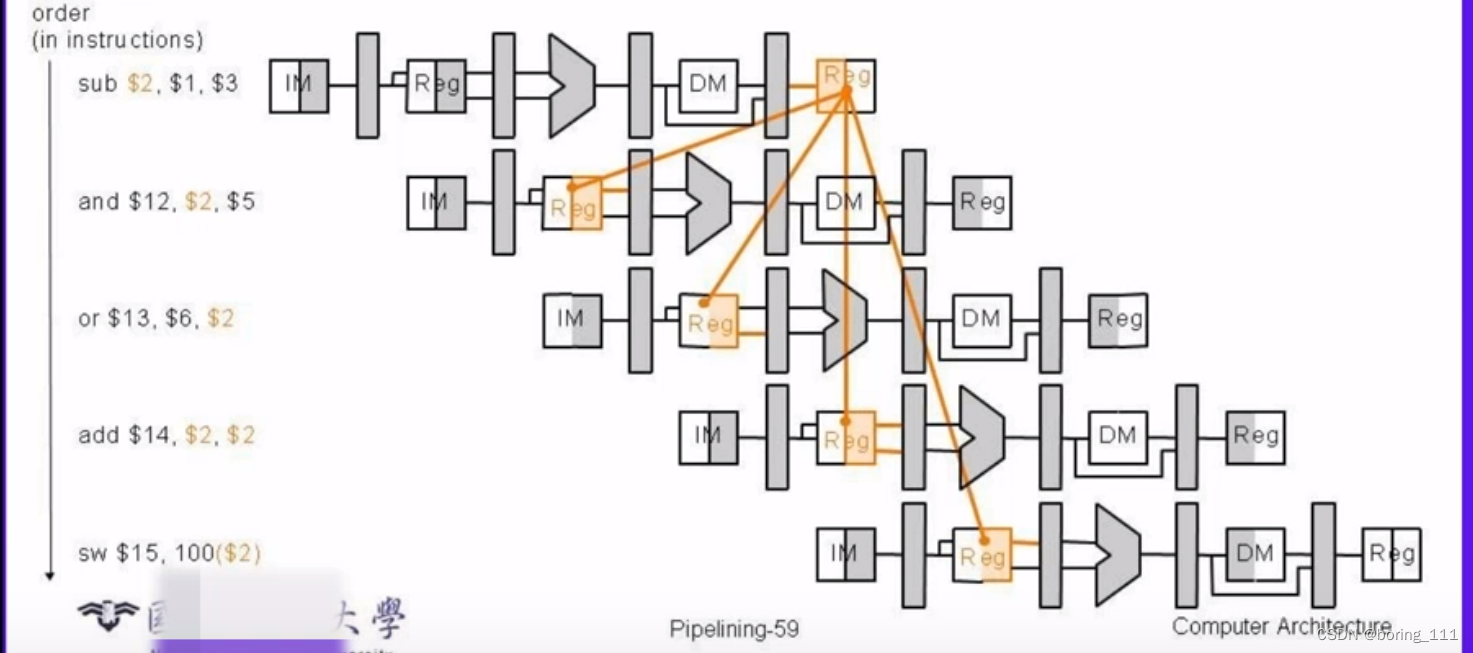

数据上data hazard

使用者为了方便编写代码,使用一个instruction的结果要对下一个instruction使用。所以我们在设计硬件的时候要有这个要求。sub要在第5个stage才写回register,而下一个instruction在第2个stage就使用了,这就不符合我们的预期,我们应该要解决。

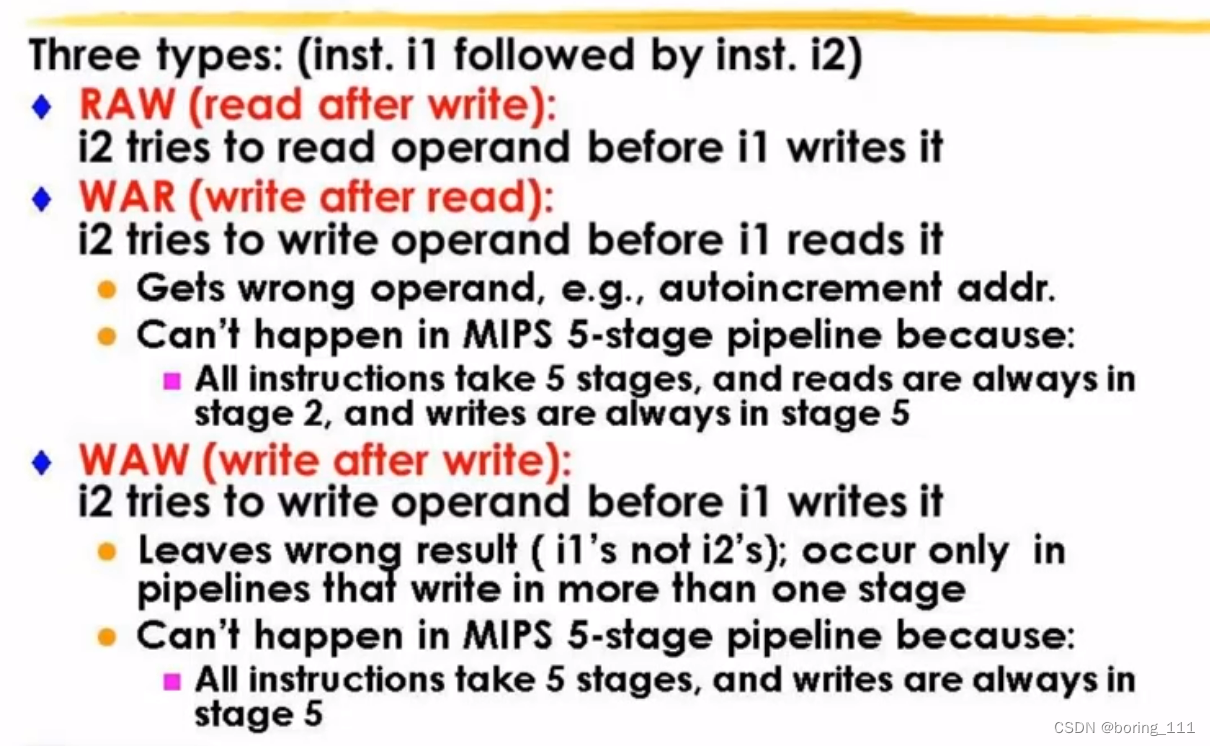

实际上因为read使用的是第二个stage读,而write使用的是第5个stage写,同时我们每个instruction都是5个stage,clock的,所以只有RAW这种结构有可能发生data hazerd

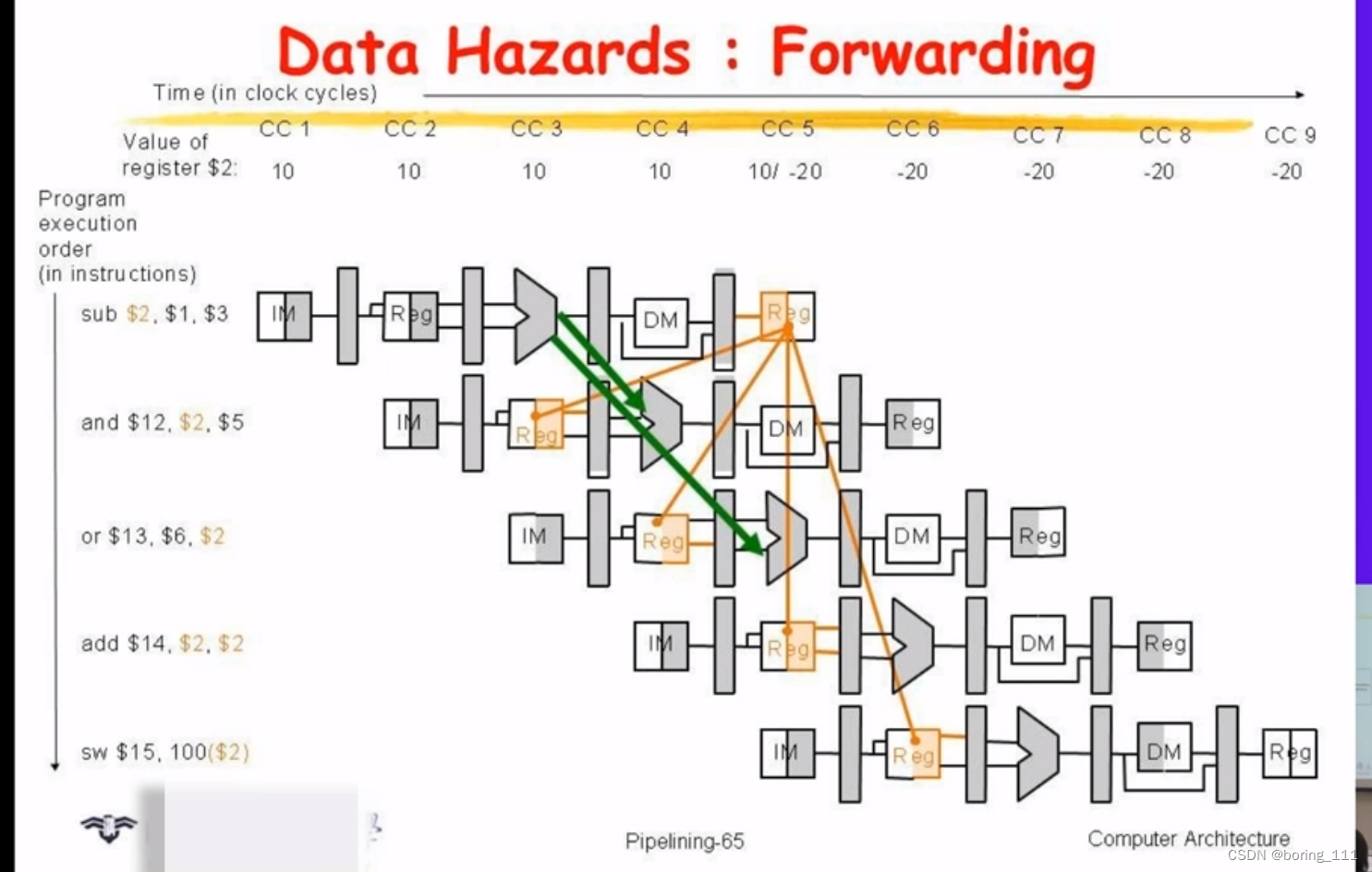

解决方法就是forwarding,因为在第三个ALU阶段就有了,可以推到读的ALU,因为两个都是第三个stage,并且write before read。所以这样就可以完美解决data harzard。

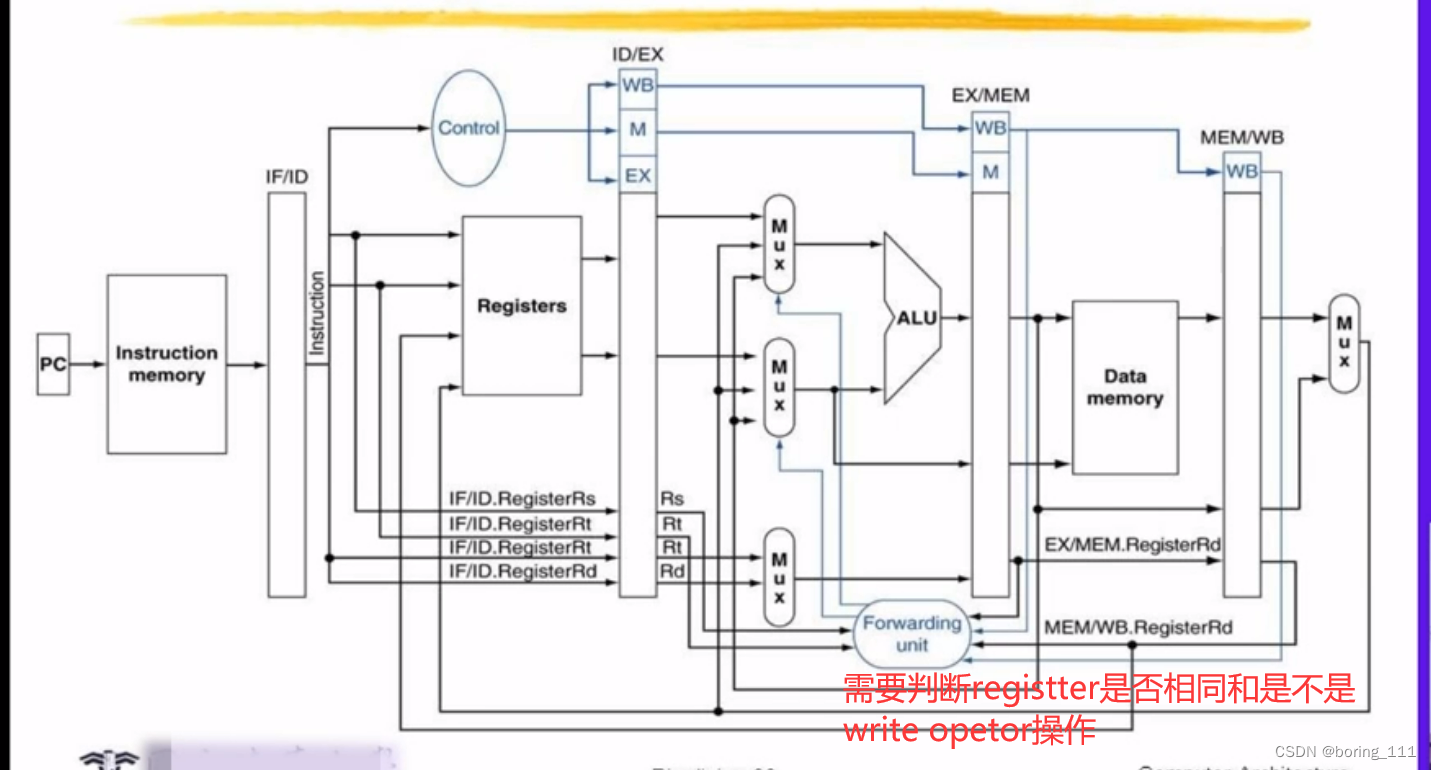

forwaring在hardware上的设计上需要追加一个forwaring unit

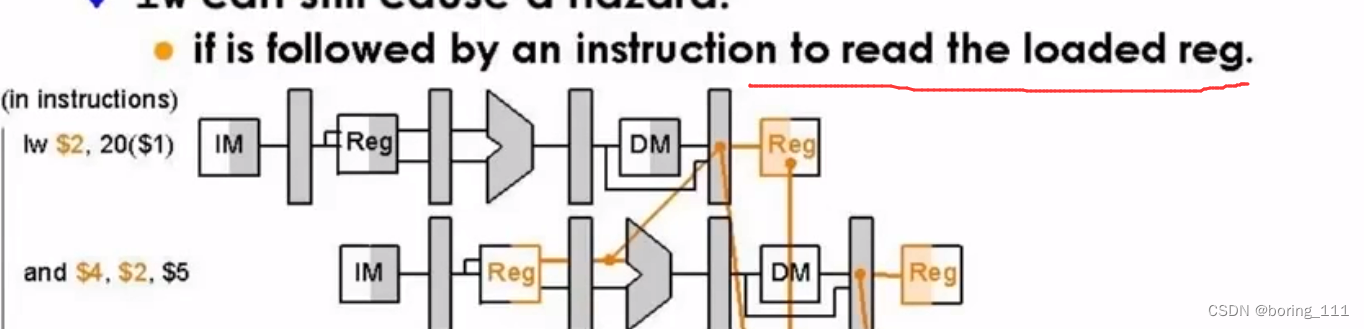

但是forwaring也不是万能的。。。

load和read就不符合上面的分析。

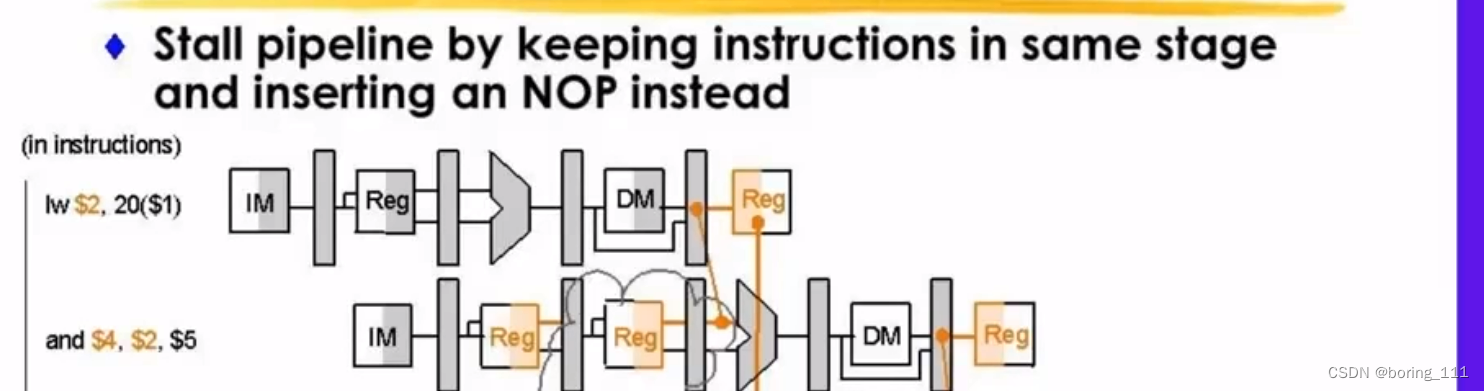

没办法了,我们就stall一个clock吧,这样pipeline file中的register2就可以传递给read的ALU用了。

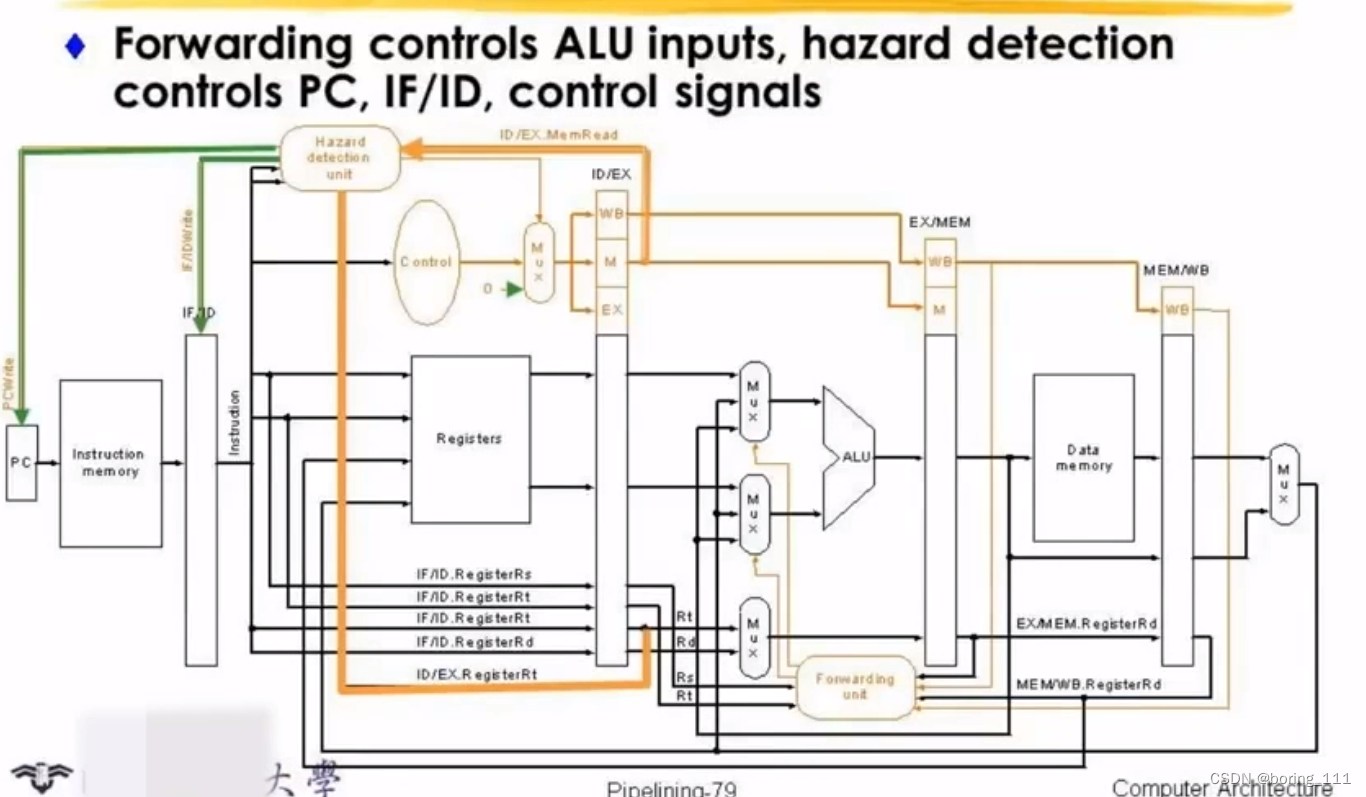

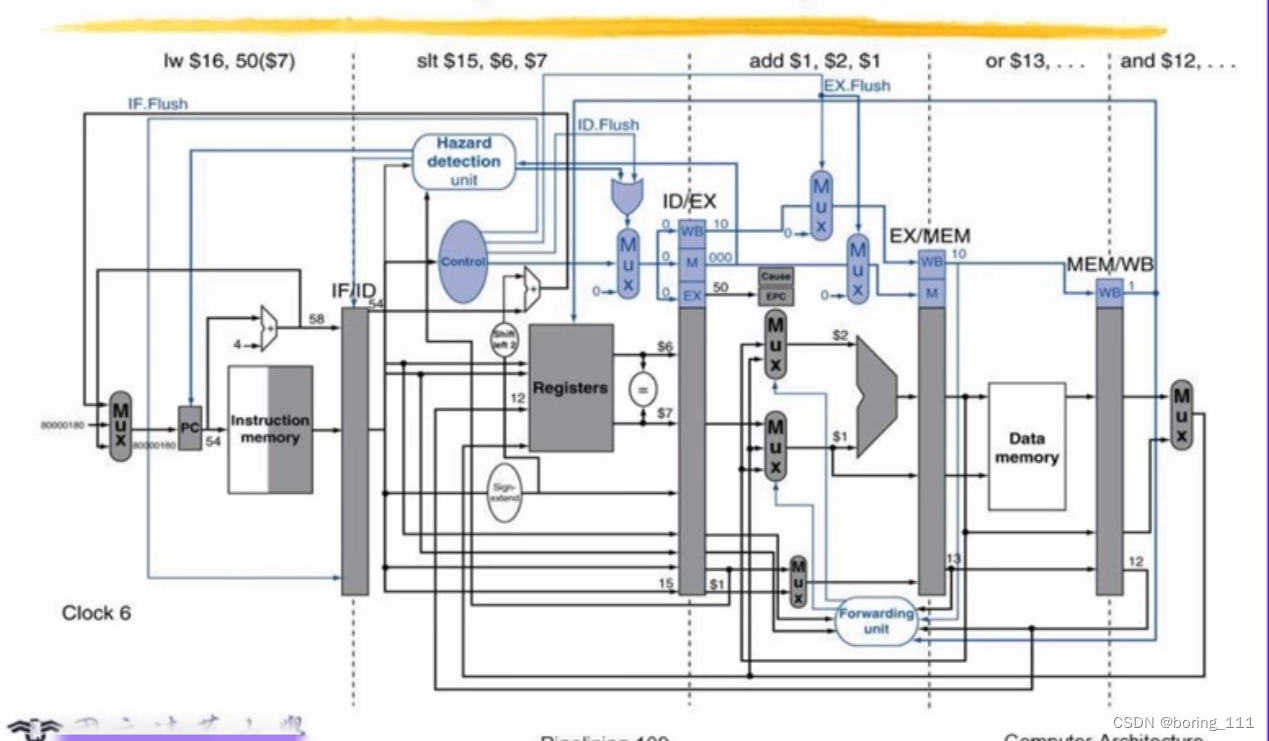

硬件上我们加了个hazard detection unit

controll(branch)冲突

pc的位置,pc + 4,还是跳到指定的位置。这是一个矛盾,当我们用branch时。为了解决这个问题我们主要提出了两种可行的优化

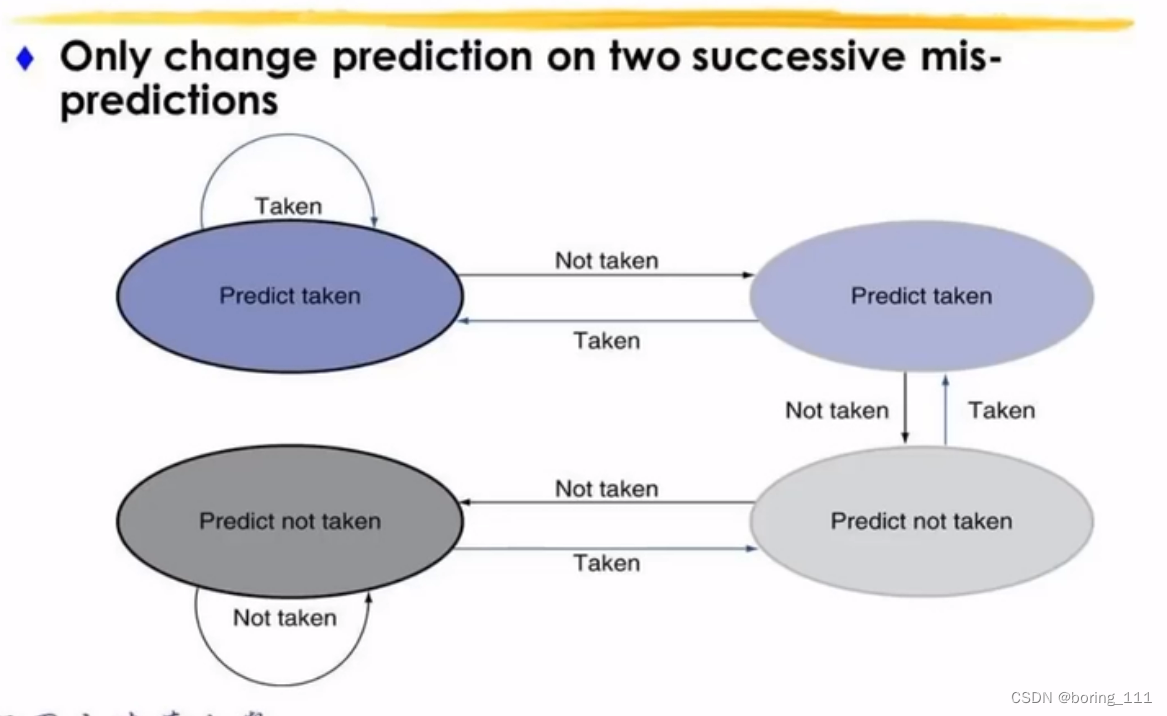

1.用2bit的preditor:因为一个bit的话,可能因为循环的最后一个跳出,而改变了原来的预测,这是不合理的,用因为循环基本上都有一个跳出点。使用失败两次,我们才要跟换预测。

2.Delay branch

把跳不跳都一样执行的指令拿到branch后面来执行,1 instrucion的距离, 刚好这样就刚好解决了预测错误的问题。

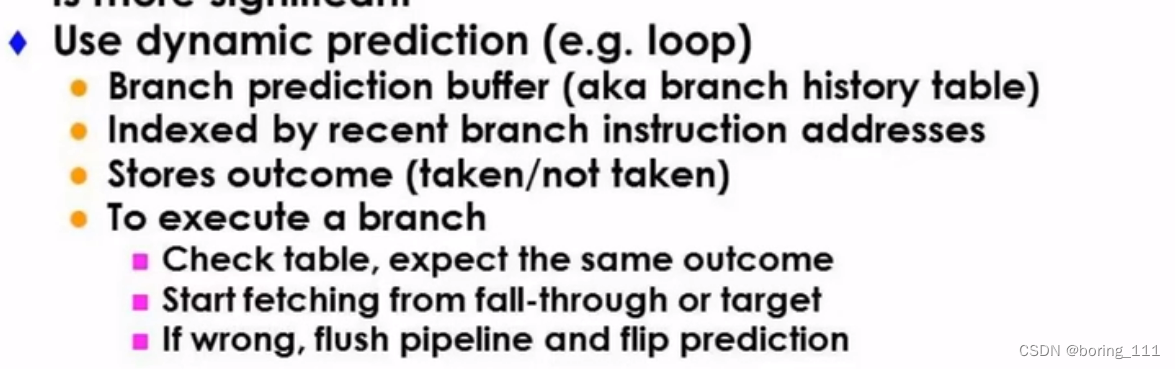

3.使用历史记录表

异常问题

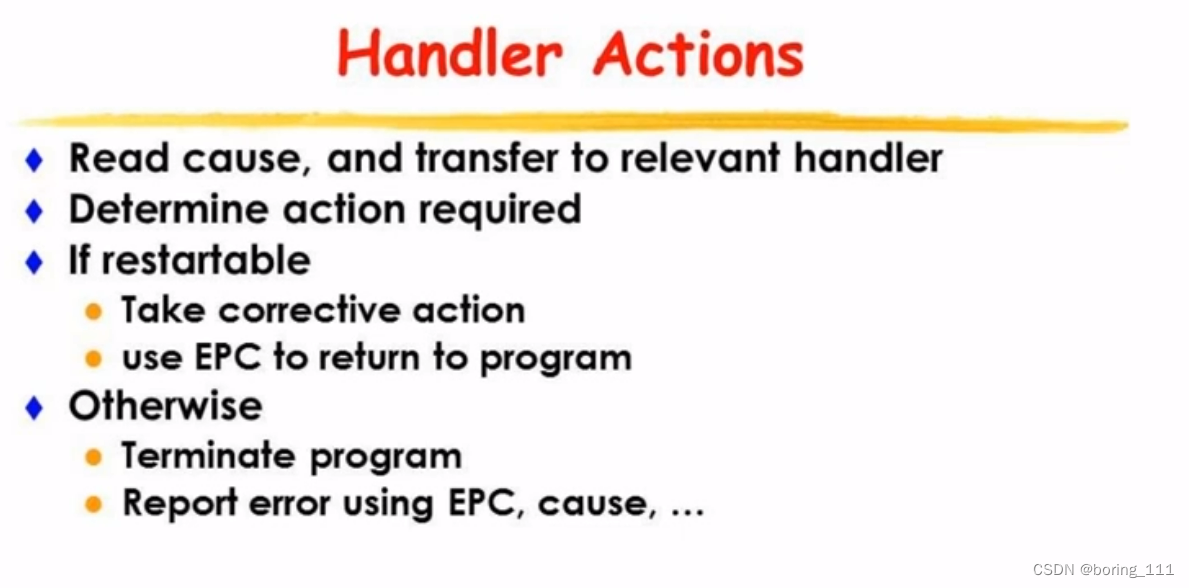

有两种一种是真异常,一种是因为I/O controller的interrput,如果是第二个,我们还要继续程序,下面存下当前位置,跳转到异常处理函数

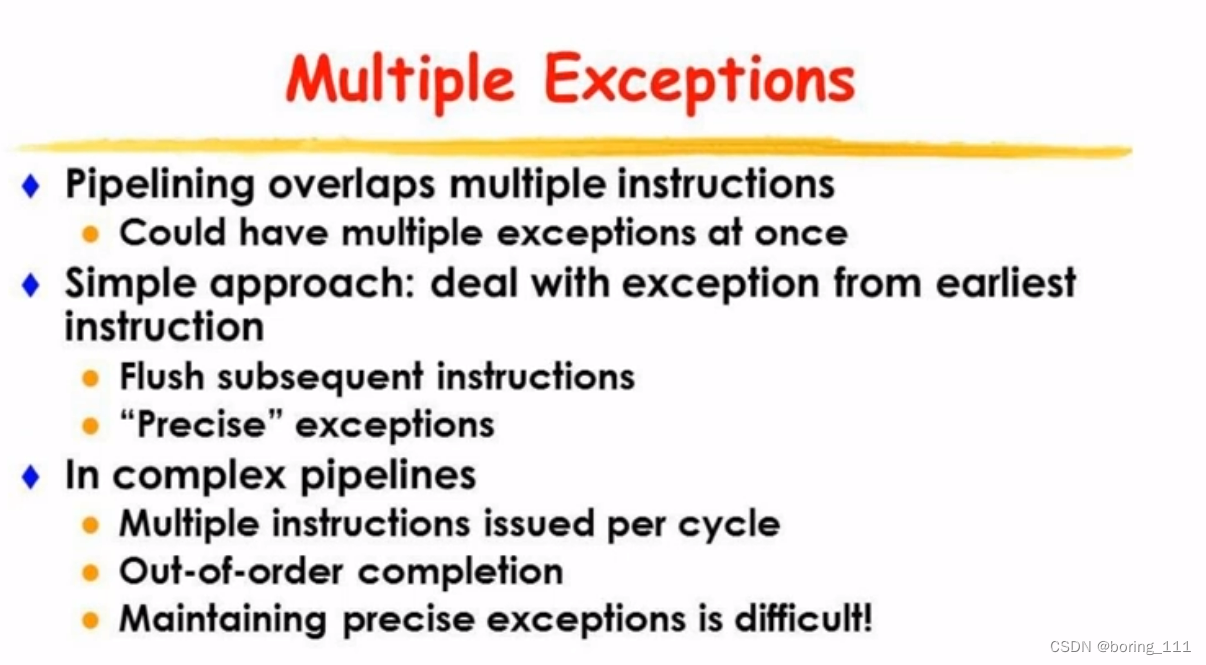

如果在pipeline时发生的话,就有点复杂了

硬件如下

文章探讨了五级流水线设计的原因,包括提高吞吐量和资源利用率。它详细阐述了结构冒险、数据冒险(特别是RAWhazard)以及如何通过转发解决这些问题。此外,还讨论了分支预测(如2位预测器和延迟分支)以及异常处理策略。

文章探讨了五级流水线设计的原因,包括提高吞吐量和资源利用率。它详细阐述了结构冒险、数据冒险(特别是RAWhazard)以及如何通过转发解决这些问题。此外,还讨论了分支预测(如2位预测器和延迟分支)以及异常处理策略。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?