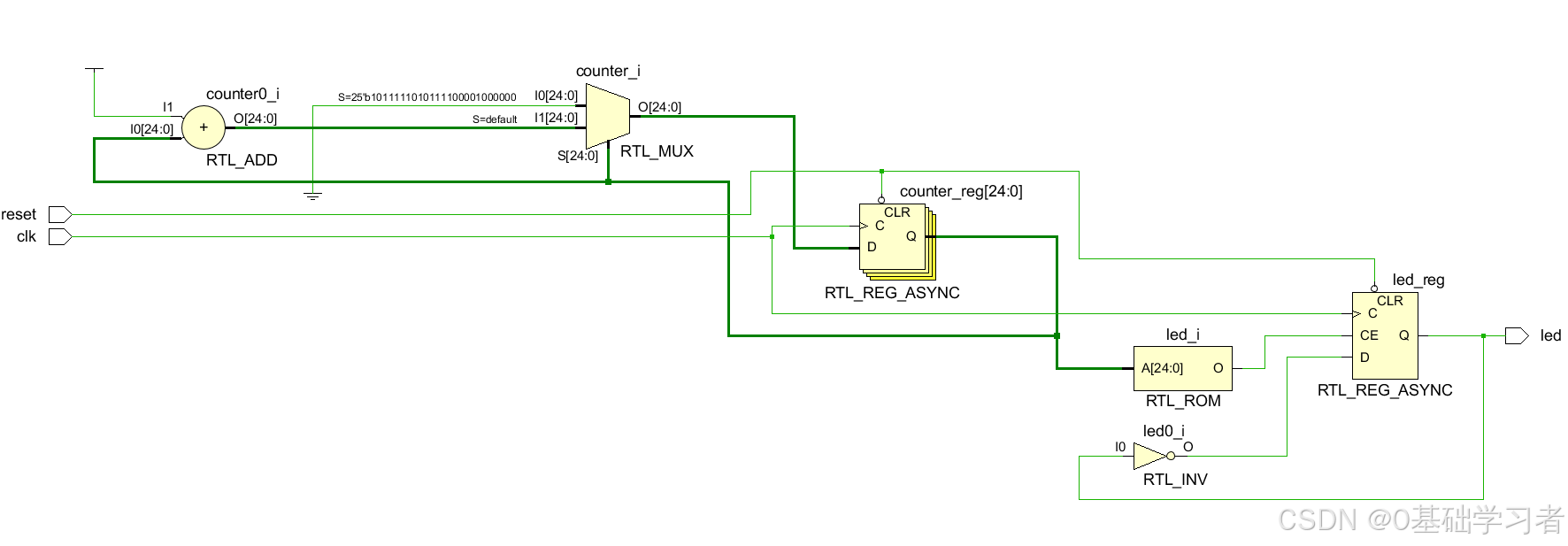

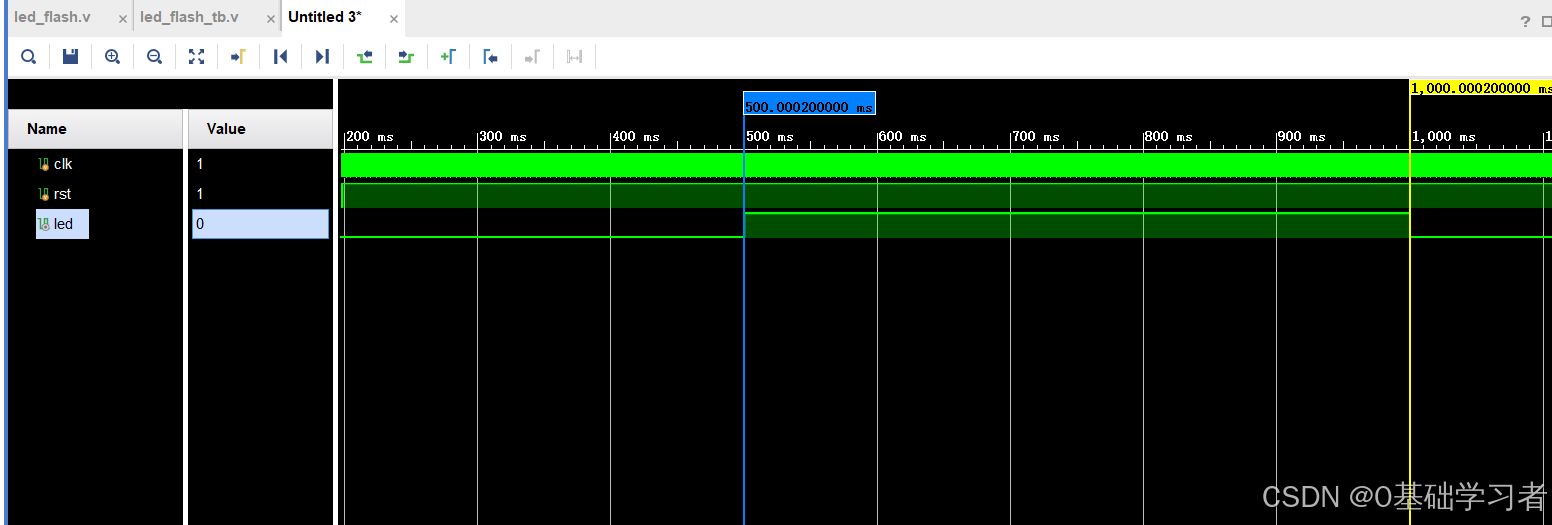

设计一个以疫苗频率闪烁的LED灯(亮灭各500ms),clk频率50MHz(20ns)

计数器:500ms\20ns=25M 换算成二进制是25位(即[24:0])

module led_flash(clk,reset,led);

input clk;

input reset;

output reg led;

reg [24:0]counter;

always@(posedge clk,negedge reset)

if(!reset)

counter<=0; //非阻塞赋值

else if(counter==24999999)

counter<=0;

else

counter<=counter+1'd1;

always@(posedge clk,negedge reset)

if(!reset)

led<=0;

else if(counter==24999999)

led<=!led;

//等同于下述代码

// always@(posedge clk,negedge reset)

// if(!reset) begin

// counter=0;

// led<=0;

// end

// else if(counter==24999999) begin

// led<=!led;

// counter=0;

// end

// else

// counter=counter+1'd1;

endmodule

仿真验证代码

`timescale 1ns/1ns

module led_flash_tb;

reg clk;

reg reset;

wire led;

led_flash led_flash(

.clk(clk),

.reset(reset),

.led(led)

);

initial clk=1;

always #10 clk=!clk;

initial begin

reset=0;

#205;

reset=1;

#2000000000;

$stop;

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?