相位检测器(PD)是将【输入信号的相位】与【压控振荡器(VCO)的相位】进行比较并生成其平均值与相位差成比例的误差电压的电路。

- 在频率合成器中,输入信号来自稳定的源,通常是低频晶体振荡器

- 在时钟和数据恢复(CDR)电路中,输入信号是其中不包含时钟信息的高速率不归零(NRZ)数据

- 【CDR电路】的PD设计方面与【频率生成电路】和【时钟生成电路】的PD设计方面有很大不同。

如今,PFD与电荷泵组合是频率合成器和时钟发生器设计中相位检测的最流行选择。

其他PD具有一些特性,例如高速操作或低杂散生成,这些PD不具有先前状态的记忆,并且在每个参考周期内提供瞬时相位误差信息,因此它们可以被归类为无记忆PD。

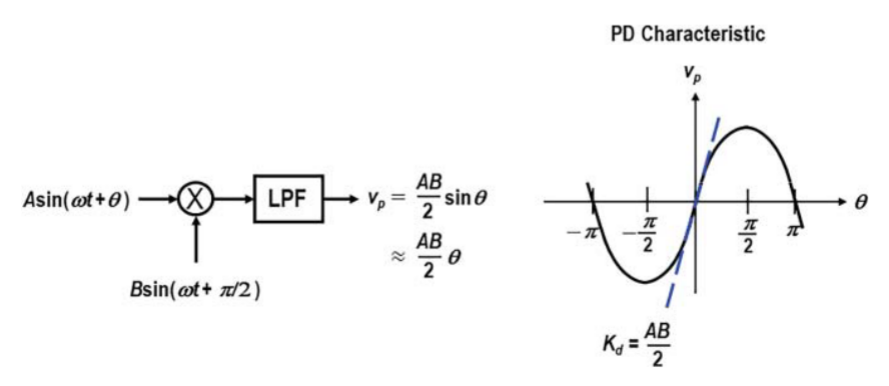

1. 乘法器 Multiplier PD

平衡混频器或乘法器是早期传统的相位检测器之一。

当两个正弦信号相乘时,输出端的DC项包含相位误差信息

两个输入:、

是两个正弦波的相位偏移

输出电压:

通过低通滤波器,高频项被抑制,小的的乘法器DC电压:

- Kd:从输入相位误差到输出电压的有效转换增益

- 乘法器可以作为增益为

的PD工作

如果使用乘法器PD,则两个正弦输入之间的静态偏移为90°时发生锁相。请注意,它是系统偏移,不应视为相位误差。

- 由上图可知,

- 相位检测器的线性范围小于

- 负斜率区域不陡到足以防止锁相环(PLL)立即脱离不稳定区域

- 当初始相位误差接近 【

】且时钟抖动很大时

- PLL会暂时处于不稳定的平衡状态,

- 并表现出较长的建立时间

- 从而导致挂起效应

- 当初始相位误差接近 【

PD增益还取决于输入信号的幅度

这种模拟PD的PLL会遇到环路增益剧烈变化

乘法器PD的另一个问题是谐波锁定

- 如果第二个输入信号是方波,

- 其频率是第一个输入信号频率的三分之一,

- 则存在与第二输入信号的三次谐波锁相的机会

因为乘法器采用模拟信号,所用乘法器PD具有最快的操作。

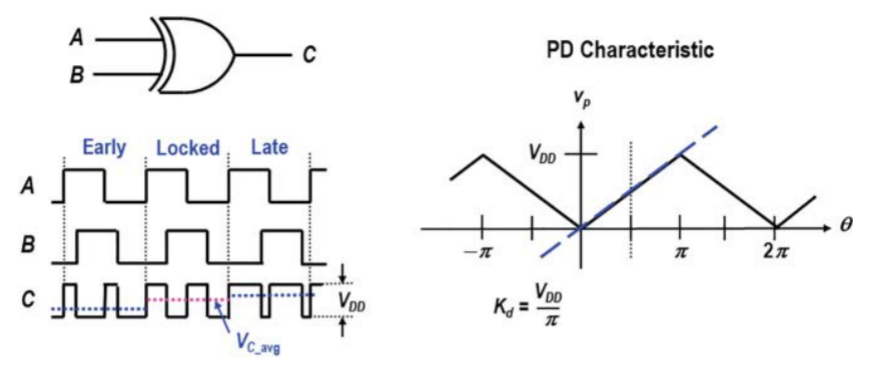

2. 异或门 exclusive-OR PD(XOR PD)

异或门,被认为是数字域的乘法器:XOR的输出波形 等于 两个输入数字信号的乘积

锁定状态:

- 当两个输入之间存在90 °相位偏移时,

- XOR门的输出具有占空比为50%的平衡输出

- PLL的锁相状态

反馈时钟早到:

- 如果反馈时钟B比参考时钟A早到来,即,相位偏移小于90 °

- XOR PD输出的占空比变得低于50%

- 有效DC电平小于0.5VDD

反馈时钟晚到:

- 如果反馈时钟B比参考时钟A晚到来,即,相位偏移大于90 °

- XOR PD输出的占空比变得低于50%

- 有效DC电平大于0.5VDD

XOR PD在±90°范围内,由单调DC控制,因此XOR PD的线性范围是

与模拟乘法器PD不同,XOR PD的增益不依赖于输入信号的幅度,因为数字操作具有轨到轨摆动

XOR PD增益

XOR PD被认为是最简单的PD,但XOR PD的使用在实践中受到限制,

- 因为它具有比其他基于逻辑的PD更差的PD特性

- 不像PFD那样提供频率捕获

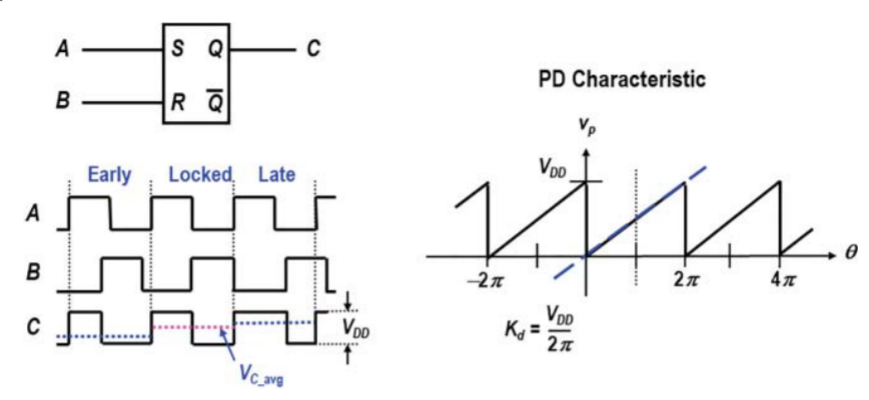

3. 触发器 Flip-Flop PD

当两个输入之间存在180°相位偏移,RS触发器作为PD工作

反馈时钟早到:

- 反馈时钟B早于参考时钟A,相位偏移小于180 °

- 反之亦然

- 如果在这两个输入之前插入反相器,则触发器PD变成具有零相位偏移的锁相

- 与PFD相比,触发器PD不储存先前的状态,

- 并且基于每个参考周期的两个输入 ,产生瞬态相位误差

以0.5VDD为中心的有效DC电平由类似XOR PD的输出波形的占空比控制,但是触发器PD的线性范围扩展到,这是XOR PD的线性范围的两倍

对于相同的电源电压,由于图所示的范围,PD增益减半:

除了加宽的线性范围外,触发器PD在【】处具有陡峭的负斜率

因此,在存在噪声的情况下,触发器PD不太可能在【】附近具有不稳定的平衡状态,从而使挂起效应最小化

作为具有宽线性范围的无记忆PD,触发器PD很好地用于延迟锁定环,

其不需要频率捕获,

还可以处理某些数字系统中的【时钟拉伸】或【丢失边缘时钟】

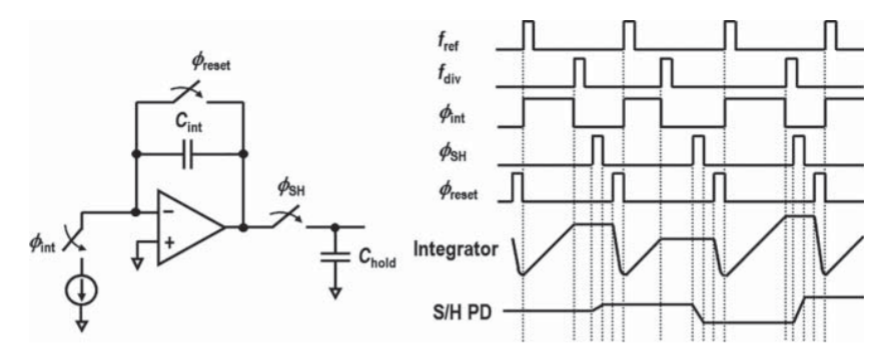

4. 采样保持PD

如果积分时间与相位误差成比例,则具有积分器的采样保持(S/H)电路可以作为PD工作。

- 上升沿检测器在参考时钟【

】和分频器反馈时钟【

】的上升沿产生短脉冲

- 一旦【

】被触发,电容【

】被充电,产生积分电压,直到【

】到达

- 积分器输出经过采样并传输到保持电容【

】,被S/H时钟

控制

- 然后,积分器输出被 复位时钟【

】重置

- 【

】处的输出电压,与每个参考周期的【

】、【

】的相位差成正比

- 当发生锁相时,【

】位于【

】脉冲的中间

- 这意味着像触发器PD一样形成180°的相位偏移

PD增益为:

是在

出的最大的电压值

- 注意,具有积分器的S/H PD不会在PLL的开环增益中产生1/s

- 这是因为Cint处的积分电压在每个参考周期都被重置,

- 因此不会在下一个时钟周期中传播

- S/H PD也被分类为非存储器PD

如果复位时间可以忽略,S/HPD的输出几乎是恒定的

S/H PD能够实现低参考杂散,早期用于高性能信号源发生器

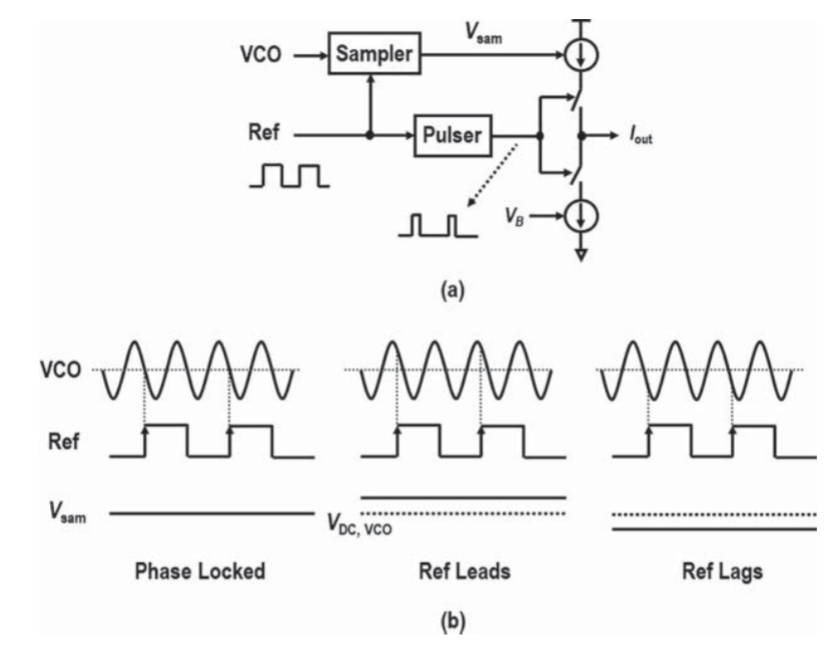

5. 亚采样PD(Sub-Sampling PD, SSPD)

(SSPD)利用参考时钟直接对VCO的波形进行采样

- 该PD用于倍频,而不使用分频器。

- 与乘法器PD类似,SSPD的增益取决于输入波形的幅度或斜率。

- SSPD的主要优势

- 是PLL输出端的低噪声贡献,因为它直接对VCO相位进行采样。

如图(b)所示

- VCO的下降沿,被参考时钟亚采样

- 根据VCO波形采样点产生不同的输出电压

- VCO波形斜率非常陡

- 可以获得高PD增益

- 当参考时钟的上升沿与VCO波形的过零点对齐时,可获得最大PD增益

- 当SSPD与电荷泵组合时,

- 工作在参考频率的电荷泵的噪声贡献被高PD增益抑制。

- 因此,可以利用SSPD设计低抖动PLL

- 然而,亚采样PLL的PD特性线性范围窄,需要用附加电路进行良好的频率采集。

- 如果VCO输出由参考时钟进行亚采样时存在耦合或非理想采样效应,则参考杂散性能可能会出现问题。

- 更重要的是,SSPD表现出高增益变化以及非线性,因为PD增益取决于VCO波形的斜率。

- SSPD的不良线性度可能会对小数N分频PLL中的带内相位噪声和杂散性能造成问题,需要额外的补偿电路。

总结对比

| 线性范围 | 增益 | 缺点 | 特点 | |

| 乘法器 Multiplier PD | 线性范围小于 | 取决于输入信号的幅度 |

| 具有最快的操作 |

| 异或门 XOR PD | 线性范围小于 |

| 最简单的PD | |

| 触发器 Flip-Flop PD | 挂起效应最小化 很好地用于延迟锁定环 | |||

| 采样保持 S / H PD | 低参考杂散 | |||

| 亚采样 SSPD |

| P低噪声贡献 |

9208

9208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?