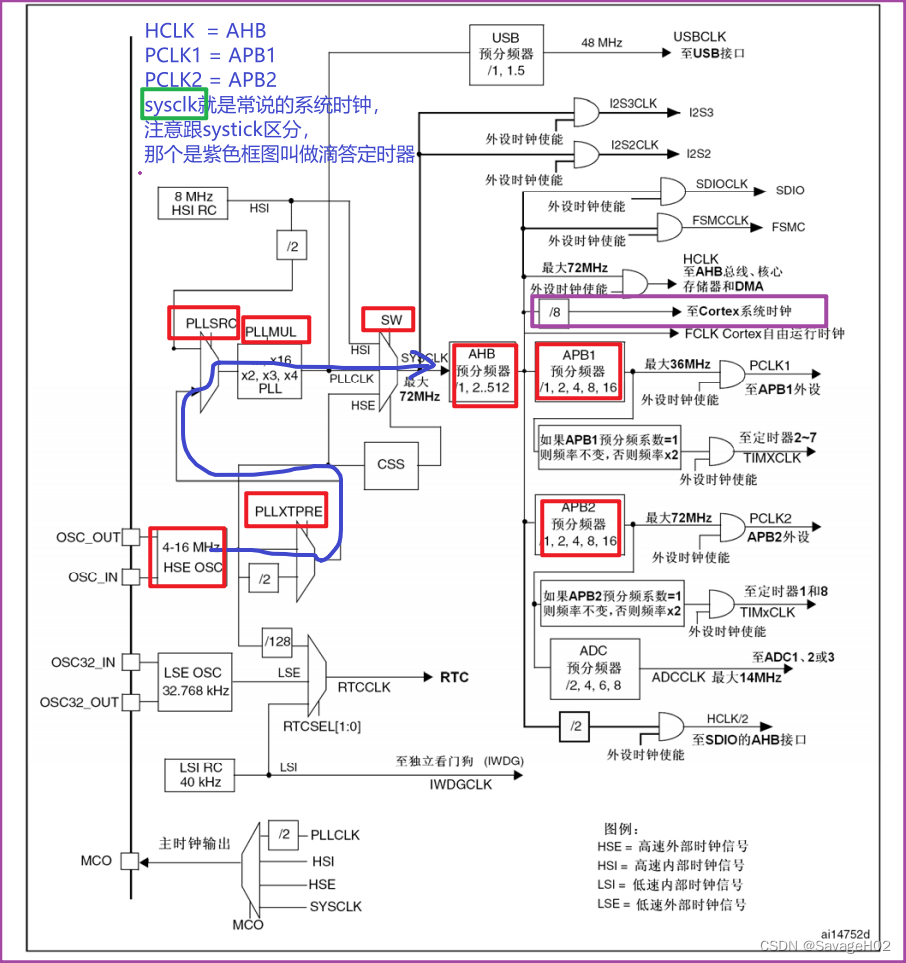

很惭愧,学了一年的stm32,一直看着那幅时钟图的密密麻麻感到害怕。现在主动去思考如何配置时钟,我结合了寄存器和库函数两种方法。大家一定得把数据手册用起来!

//系统时钟配置函数 from:Savage

void RCC_SysClock_Configuration(void)

{

RCC_TypeDef *myRCC = RCC;//因为在source Insight无法直接操作RCC所以创建一个相同指针

RCC_DeInit();//RCC设置默认

RCC_HSEConfig(RCC_HSE_ON);//使能高速外部时钟

while(RCC_GetFlagStatus(RCC_FLAG_HSERDY) == RESET);//等待高速外部时钟正常

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);//设置倍频器参数 8*9 = 72M

//PLLSRC:config CFGR->bit16 0:hsi/2 1:hse 图片中对应的那个寄存器

myRCC->CFGR |= (0x01<<16);

//PLLXTPRE:HSE yes or not dir(fenpin) 1:yes 0:no

myRCC->CFGR &= ~(0x01<<17);

//set 'SW',SW from CFGR bit 0-1

myRCC->CFGR &= ~0x03; //clear SW

myRCC->CFGR |= 0x02; //write SW to start PLL 设置1:0位为10

while( (myRCC->CFGR & (0x01<<3)) != 1 && (myRCC->CFGR & (1<<2) != 0));//等待SW位成功设置为PLL路线

RCC_HCLKConfig(RCC_SYSCLK_Div1);//配置AHB时钟 不被sysclk分频(一分频就是不分频)

RCC_PCLK1Config(RCC_HCLK_Div2);//配置APB1,手册说最大支持36M,所以必须配置2分频或以上

RCC_PCLK2Config(RCC_HCLK_Div1);//配置APB2

RCC_ADCCLKConfig(RCC_PCLK2_Div6);//配置ADC时钟,因为手册说不能超过14M,所以最高只能6分频 72/6

RCC_PLLCmd(ENABLE);//使能倍频器

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);//等待倍频器正常

//其他外设先不用配置,挂载在APB2高速上的、APB1低速上和AHB总线的外设到时候使用下列函数

/*void RCC_AHBPeriphClockCmd(uint32_t RCC_AHBPeriph, FunctionalState NewState);

void RCC_APB2PeriphClockCmd(uint32_t RCC_APB2Periph, FunctionalState NewState);

void RCC_APB1PeriphClockCmd(uint32_t RCC_APB1Periph, FunctionalState NewState);*/

}最后,我还有个疑问希望大家解答,就是sysclk是不是就是我们在主函数跑代码的速度。我觉得应该是!嘿嘿,那有问题欢迎大家指正!from:Savage

文章介绍了如何克服对STM32时钟配置的恐惧,结合寄存器和库函数进行系统时钟配置,包括启用HSE,设置PLL,配置AHB、APB1和APB2时钟分频,以及使能倍频器。作者强调了使用数据手册的重要性,并提出了关于系统时钟(sysclk)与代码执行速度关系的疑问。

文章介绍了如何克服对STM32时钟配置的恐惧,结合寄存器和库函数进行系统时钟配置,包括启用HSE,设置PLL,配置AHB、APB1和APB2时钟分频,以及使能倍频器。作者强调了使用数据手册的重要性,并提出了关于系统时钟(sysclk)与代码执行速度关系的疑问。

3706

3706

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?