1.伪路径约束

伪路径是设计中非功能路径或没有任何时序要求的路径。伪路径指的是该路径存在,但该路径的电路功能不会发生或者无须时序约束。

常见的伪路径包括:

1.代码编辑人员已经在设计上已经做了时序保证的路径,则不需要软件再进行时序约束路径。

2.已经做过同步化处理的 (FIFO,RAM,打拍等等)

3.

总结下就是 :从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑;从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径。

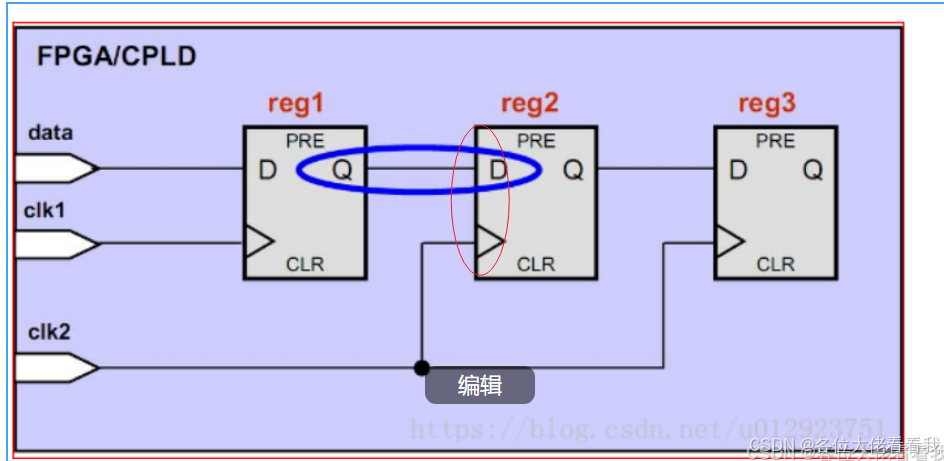

reg1的输出和reg2的输入跨越了不同的时钟域clk1和clk2,我们不希望综合工具对这这些路径进行分析,就是说这些路径就是我们所说的FALSE PATH:

set_false_path –from [get_pins reg1|clk]–to [get_pins reg2|datain] (这个约束是不分析蓝色圈圈中的传输眼熟)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?