Jetson Nano 中的 GIC-400(Generic Interrupt Controller)是一个高效的中断控制器

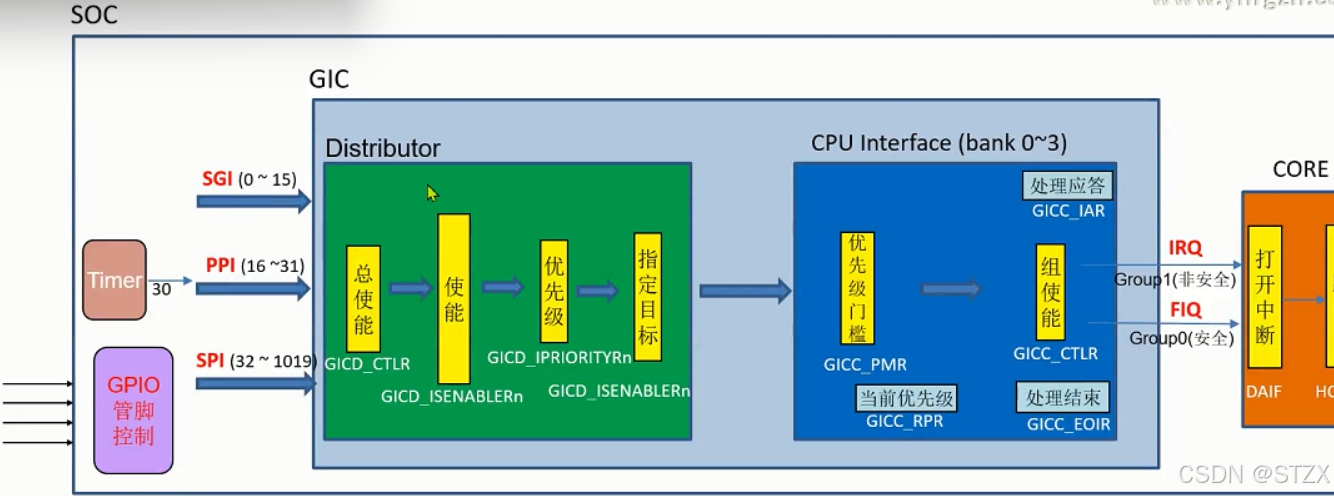

GIC-400 本身作为一个中断控制器,其物理结构包括 Distributor 和 CPU Interface:

Distributor:负责接收所有的中断请求,并根据中断的优先级、类型等信息进行处理和分配。它位于系统的中央,接收外部和内部中断信号,并控制中断的激活。

CPU Interface:每个 CPU 核心都有一个 CPU 接口,用来接收分配到该核心的中断信号。它通过该接口与 Distributor 交互,向 CPU 发送中断请求。

- 外部输入中断信号

根据芯片手册,不同寄存器配合可将中断指令传入GIC中,大致可分为三类指令

SGI(Software Generated Interrupt):

来源:由软件产生。

用途:进程间通信、内核调度、多核同步等。

特点:灵活、软件控制。

PPI(Private Peripheral Interrupt):

来源:由处理器的私有外设产生。

用途:单核心外设(如定时器、GPIO)的中断。

特点:每个核心的私有中断,不会传递到其他核心。

SPI(Shared Peripheral Interrupt):

来源:由系统的共享外设产生,多个核心可以共享这些中断。

用途:外部设备中断(如网络适配器、DMA 控制器等)。

特点:可以被多个核心共享,通常用于外设与多个处理核心之间的中断通信。

2.Distributor (分配器)

distributor 主要负责 中断分发 和 管理,它的作用是将外部和内部的中断请求分发给相应的处理器核心,根据中断请求的优先级顺序来决定处理顺序。

具体来说,一个请求的优先级别体现在该请求的某些字段上,若范围是 0 到 255(取决于芯片手册)。则0 代表最高的优先级,255 代表最低的优先级。

3.CPU Interface (接口)

CPU Interface 接收来自 GIC distributor 的中断信号,并将其传递给 CPU 核心。它负责将中断从 GIC 的分配器部分传递到具体的处理器核心

CPU Interface 确保中断可以被 CPU 正确识别并处理。它为 CPU 提供必要的信息(如中断源、优先级等),并控制 CPU 是否需要进入中断处理程序。同时管理中断的状态,包括处理中断时的优先级控制、屏蔽和清除等操作。它可以根据 GIC 的配置来选择是否触发中断,根据系统需要屏蔽低优先级的中断,或只允许高优先级的中断通过,从而保证系统的稳定性和高效响应。

4.CPU 核

在中断由CPU interface传入CPU CORE时, GICD_IGROUPRn 负责 控制每个中断属于 Group 0 还是 Group 1,GICD_IGROUPRn 是一个 32 位的寄存器,每一位对应一个中断源。

· Group 0:安全模式(Secure Mode)专用,优先级更高,可触发 FIQ。

· Group 1:普通模式(Non-Secure Mode)使用,可触发 IRQ,由 OS 处理。

在传到CPU核时,常用两个寄存器:DAIF(Interrupt Mask Bits)、HCR_EL2(Hypervisor Control Register)

一、DAIF 是一个 状态寄存器,它用于控制中断的屏蔽和优先级。这个寄存器在 ARM 架构中用于管理中断的禁用和使能。它是一个 4 位的标志位,位于 CPSR(Current Program Status Register) 中,或在一些高权限级别中为 DAIF寄存器。它的作用是控制 CPU 的中断处理行为。

DAIF 主要控制以下 4 个中断的屏蔽:

D(Debug Mask):控制调试相关中断(Debug interrupts)。

A(Abort Mask):控制同步异常(例如地址错误)相关中断的屏蔽。

I(IRQ Mask):控制普通中断(IRQ)的屏蔽。

F(FIQ Mask):控制快速中断(FIQ)的屏蔽。

通过设置和清除 DAIF 寄存器中的相应位,操作系统或固件可以在不同的上下文中(如系统模式、异常模式等)控制是否允许某种类型的中断:

DAIF = 0:允许中断。

DAIF = 1:禁用中断。

二、 HCR_EL2(Hypervisor Control Register)专门用于在 ARM 架构的 虚拟化模式 中进行中断控制。它是 EL2(Exception Level 2) 权限级别下的寄存器,通常与虚拟化相关的操作系统和 Hypervisor 交互时使用。

328

328

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?