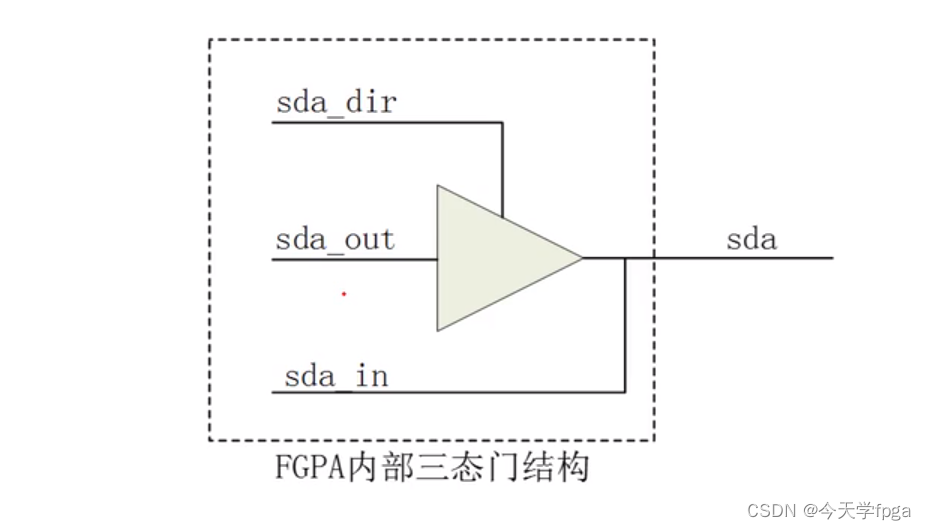

FPGA中经常使用到inout类型的双向数据线,比如IIC协议中的SDA数据线。那么在FPGA中是如何实现这种形式的端口呢?使用三态门逻辑进行控制。如下图:

当控制信号有效时,数据输出,相当于output端口。当控制信号无效时,三态门处于高阻状态,此时信号线与内部输入线连接,相当于实现input端口。verilog实现如下:

inout sda, //双向信号线

assign sda = sda_dir ? sda_out : 'bz;

assign sda_in = sda;'

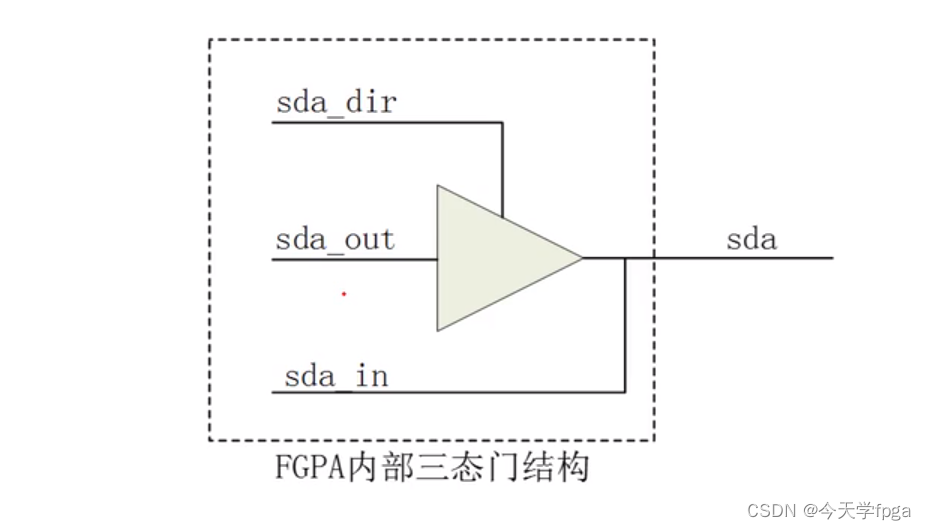

FPGA中经常使用到inout类型的双向数据线,比如IIC协议中的SDA数据线。那么在FPGA中是如何实现这种形式的端口呢?使用三态门逻辑进行控制。如下图:

当控制信号有效时,数据输出,相当于output端口。当控制信号无效时,三态门处于高阻状态,此时信号线与内部输入线连接,相当于实现input端口。verilog实现如下:

inout sda, //双向信号线

assign sda = sda_dir ? sda_out : 'bz;

assign sda_in = sda;'

4631

4631

3782

3782

1481

1481

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?