⼀ 实验⽬的

1. 掌握组合逻辑电路的设计⽅法

2. 掌握Quartus II软件⽂本输⼊设计的流程

⼆ 实验内容

2.1 设计输⼊

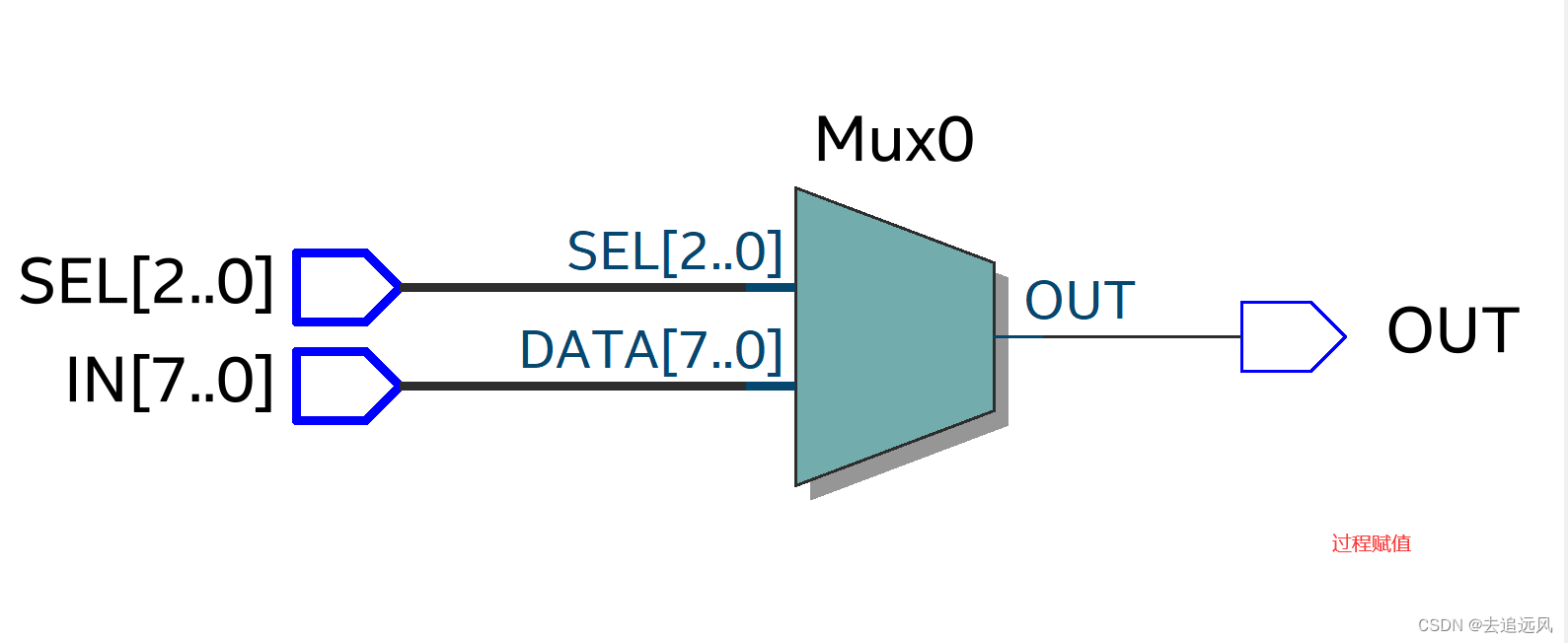

1. 模块名称:MUX81

2. 输⼊输出:IN[7:0],SEL[2:0],OUT

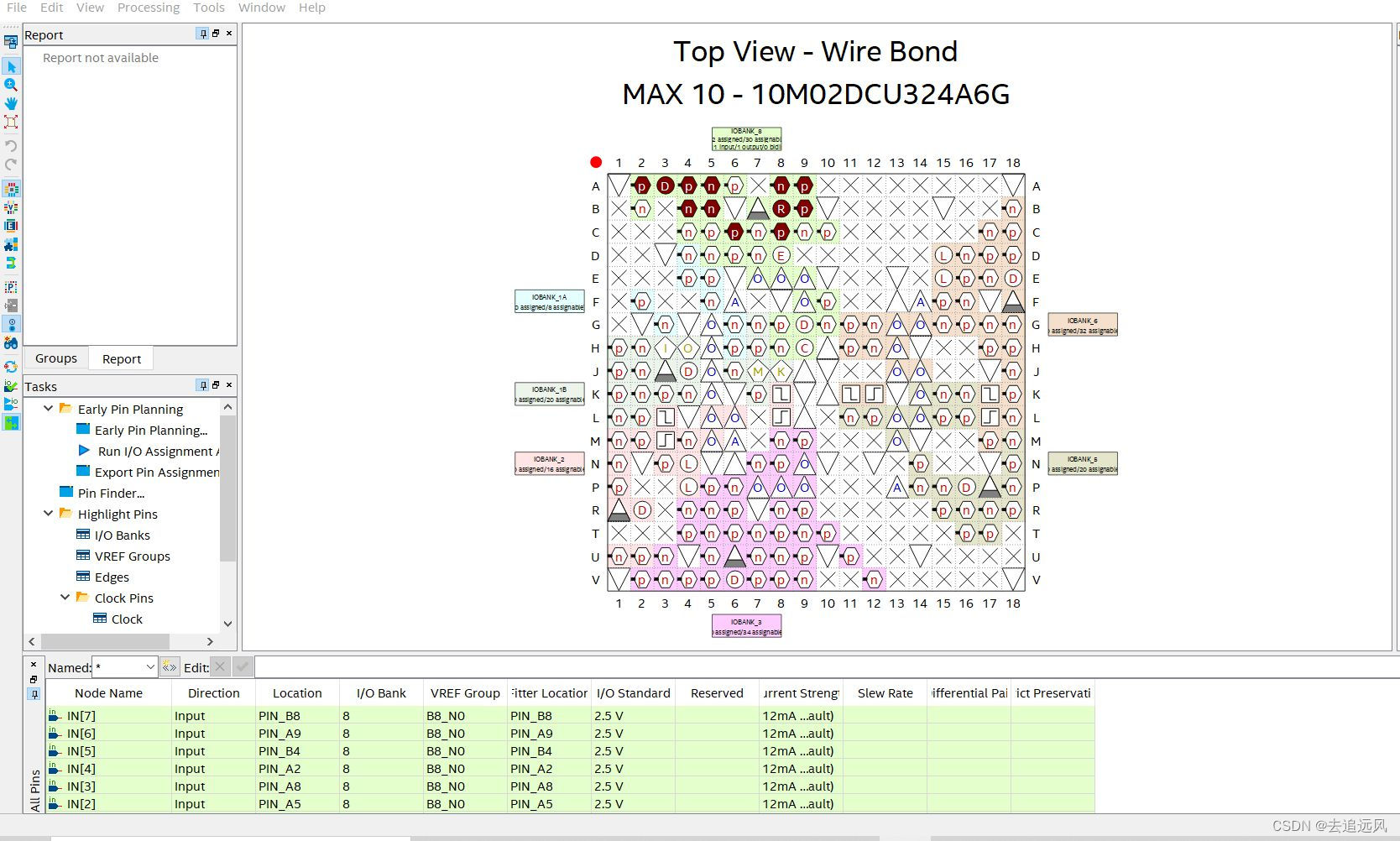

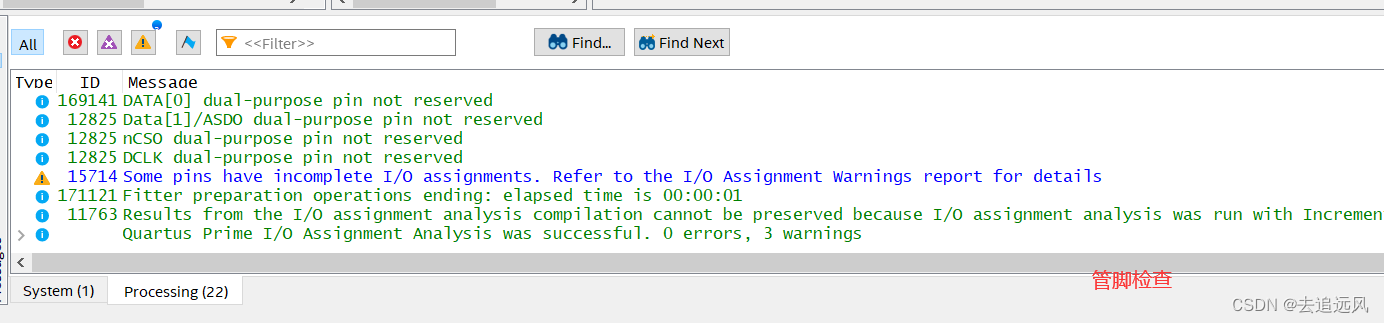

2.2 引脚约束

1. 输⼊端 ⾃定义

2. 输出端 ⾃定义

2.3 设计要求

1. 使⽤“连续赋值”和“过程赋值”两种⽅案分别实现

2. “过程赋值”需要使⽤ case 语句

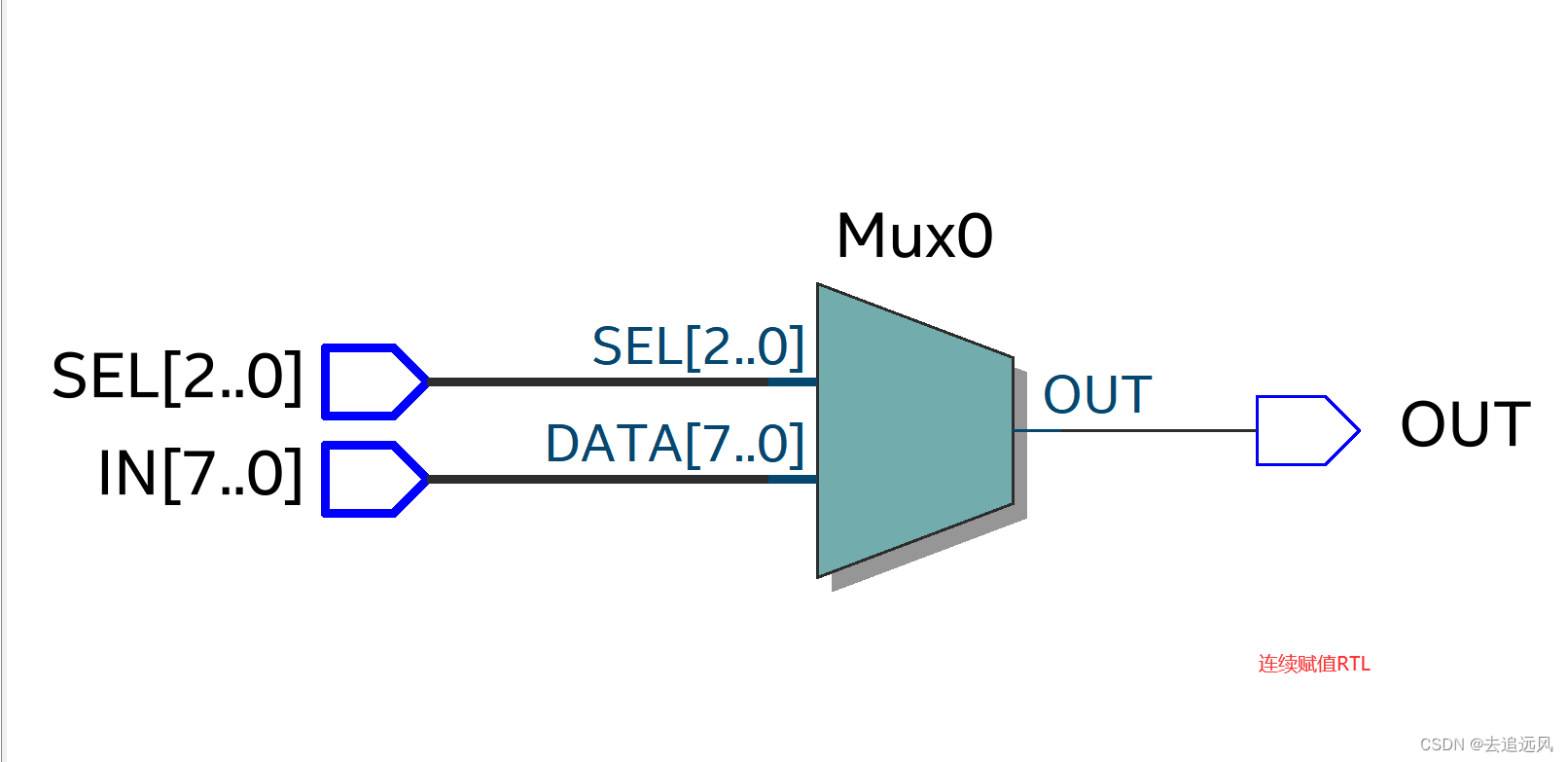

3. 使⽤RTL View分析电路的区别

2.4 电路仿真1. 激励⽂件

2. 功能仿真

三 实验报告

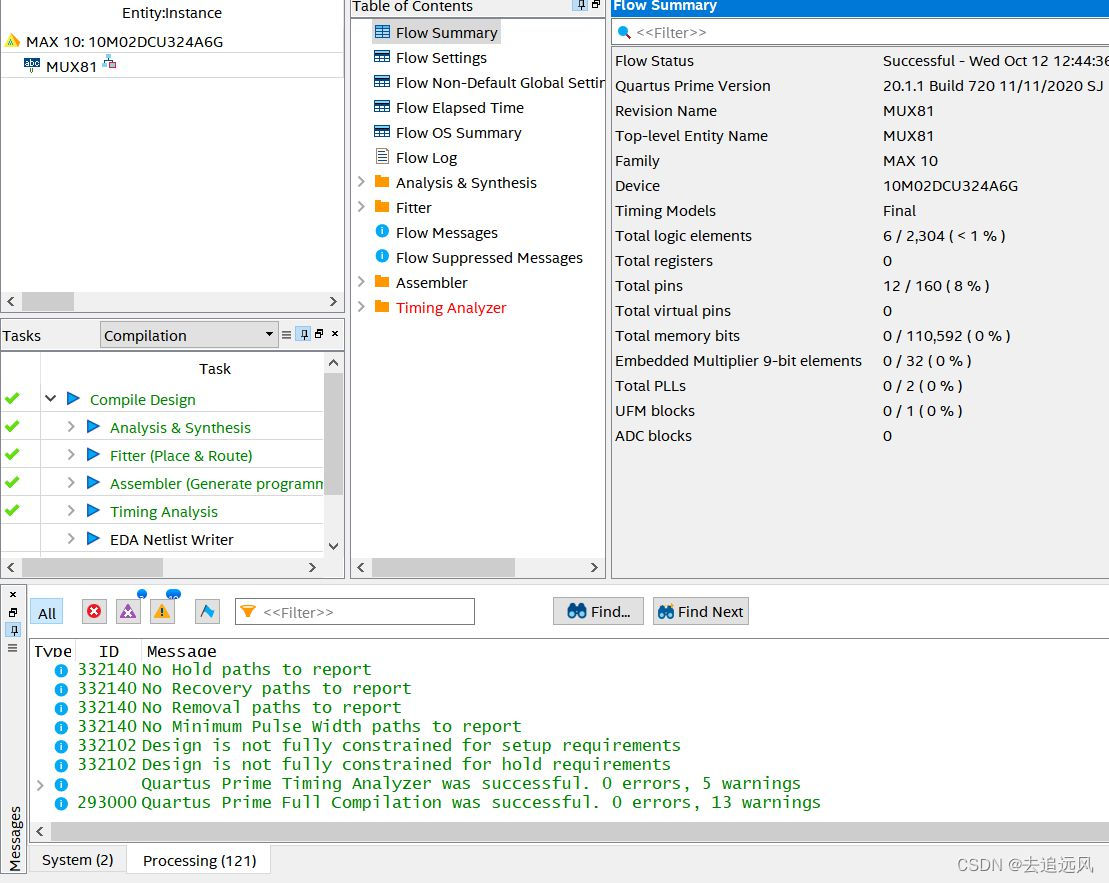

1. 设计代码、RTL视图

2. 仿真结果

3. 报告中附代码和仿真结果截图

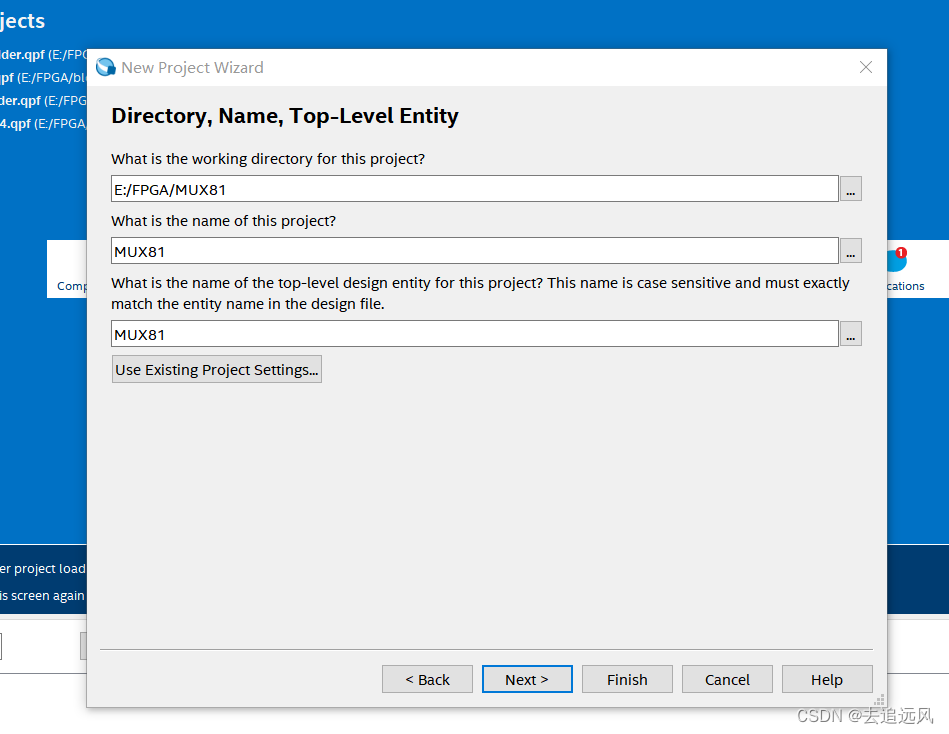

1.路径设置&创建verilog文件

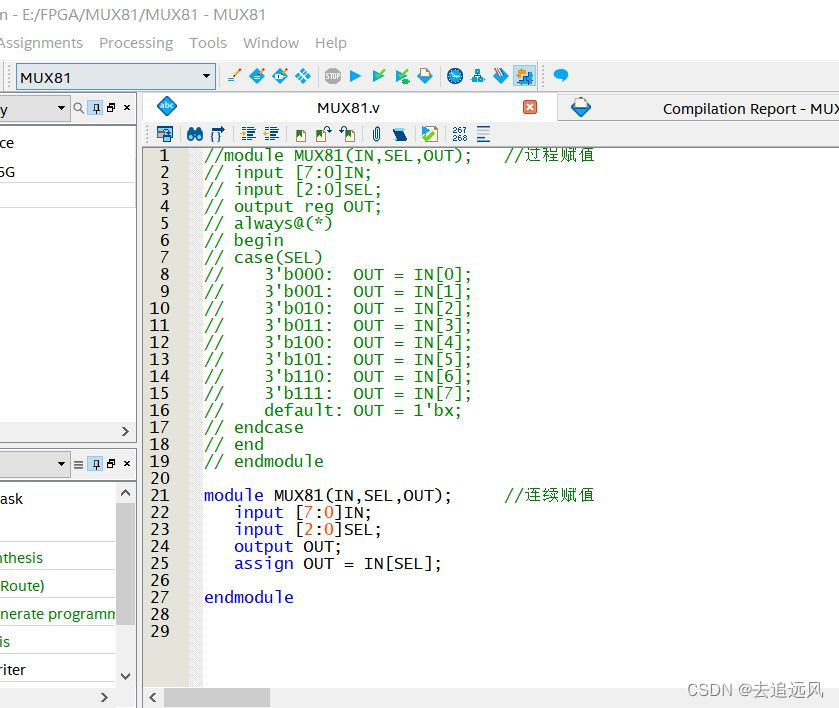

2.代码 (过程赋值 和连续赋值)

module MUX81(IN,SEL,OUT); //过程赋值

input [7:0]IN;

input [2:0]SEL;

output reg OUT;

always@(*)

begin

case(SEL)

3'b000: OUT = IN[0];

3'b001: OUT = IN[1];

3'b010: OUT = IN[2];

3'b011: OUT = IN[3];

3'b100: OUT = IN[4];

3'b101: OUT = IN[5];

3'b110: OUT = IN[6];

3'b111: OUT = IN[7];

default: OUT = 1'bx;

endcase

end

endmodule

//module MUX81(IN,SEL,OUT); //连续赋值

// input [7:0]IN;

// input [2:0]SEL;

// output OUT;

// assign OUT = IN[SEL];

//endmodule

3.RTLview :

IN[7:0]为8个1bit的数据,在仿真时设置为Random,随机

SEL[2:0] 3个1bit ,SEL 为000~111 (0~7)

从IN中选出对应的值作为OUT 的输出

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?