进位加法器实现

在不考虑进位的情况下:

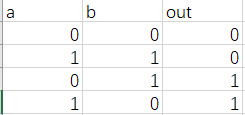

a+b的输出结果的真值表为:

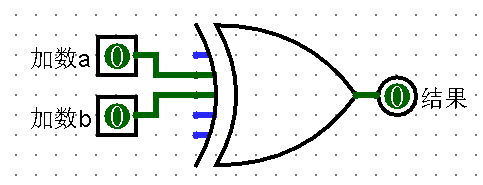

由图可知,该结果实际上为一个异或,因此可以设计以下电路:

在考虑进位的情况下:

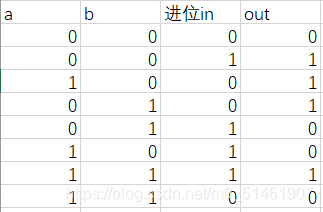

首先分析结果的值,可得以下真值表:

由图可知,该结果为一个三位异或,因此可以设计以下电路:

再分析进位输出的值:

①首先,若a,b全为1,则进位输出out一定为1。

②若a,b有一个为1,则进位输出out由进位输入in决定:当进位in=0时,进位输出out=0;当进位in=1时,进位输出out=1;

③若a,b全为0时,则不论进位输入in为多少,进位输出out恒为0;

因此,可写出以下关系式:

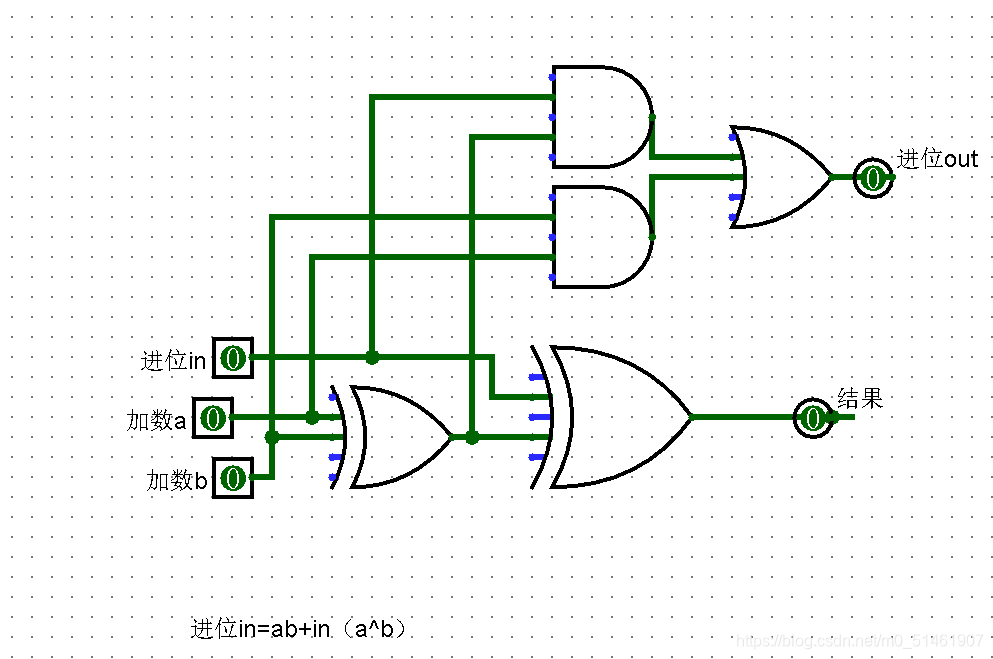

进位输出out=ab+in(a^b)

因此设计出电路图:

1435

1435

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?