在工科背景或电子爱好者的工作生活中经常需要设计电路图,并交接给pcb工程师画板、采购去备料,一份规范的电路图能大大简化交接工作。本文简单介绍电路图的一些设计细节,帮助绘制更标准的电路图。

我分四点来介绍:

一、精确性与信号完整性

-

显式标注器件关键参数 (超越基础值):

-

是什么: 不只是标

0.1uF, 需要标注0.1uF, X7R, 0603, 10V(或10uF, POSCAP, 3216, 6.3V)等影响选型和性能的核心参数。 -

为什么重要: 采购、焊接、电路性能(如电容 ESR/DCL/精度、电阻功率/精度/温漂、二极管反向恢复时间/Vf)都依赖于此。避免了在 BOM/布局阶段再查资料或引发歧义。

-

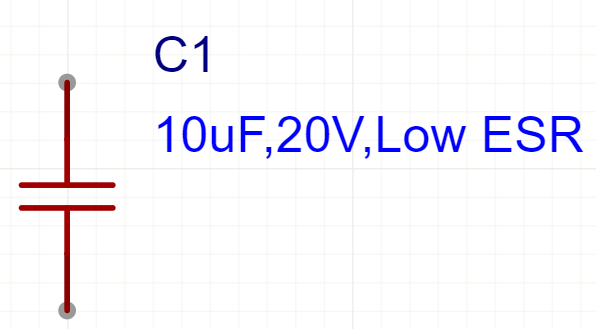

示意图:

[原理图上电容旁标注] C8: 10uF, Tantalum Polymer, 20V, Case-D (7343), Low ESR(实际情况可以不标注这么多,但是容值和耐压得标注)

-

-

明确标注关键网络的电气要求:

- 是什么: 在信号线/电源线上直接标注特性阻抗(

Zo=50Ω)、走线长度要求(Max Length < 50mm)、差分对(Diff Pair: USB_D+, USB_D-, Length Matching <= 5mil)、电流承载能力(Trace Current > 2A)。 - 为什么重要: 指导 PCB Layout 工程师进行关键布线,保证高速信号完整性、大电流通路安全。

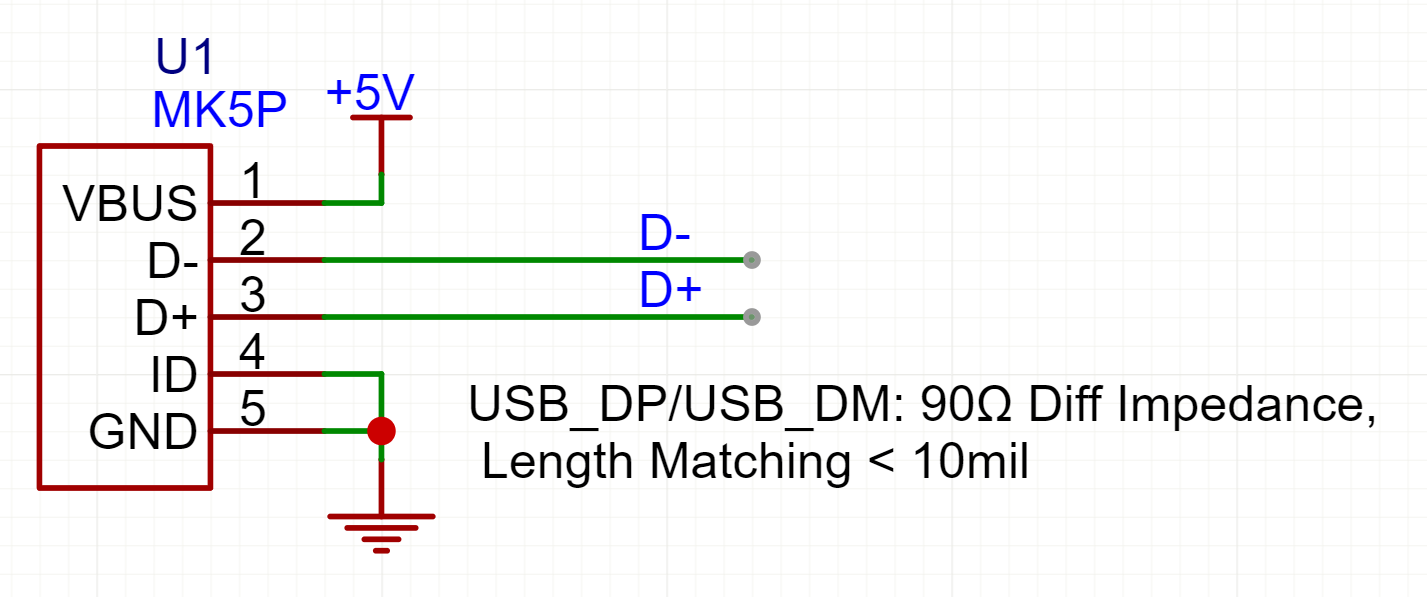

- 示意图:

[USB差分线旁标注] USB_DP/USB_DM: 90Ω Diff Impedance, Length Matching < 10mil

- 是什么: 在信号线/电源线上直接标注特性阻抗(

-

清晰标识测试点(Test Points):

- 是什么: 使用

TPx(如TP1,TP2) 符号或明确标注,放在关键信号(时钟、复位、模拟采样、电源纹波测量点)、参考电压点上。 - 为什么重要: 极大简化生产测试、功能调试和故障维修流程,避免飞线或寻找焊盘。预留的空间和位置也需在原理图中考虑。

- 示意图:

[信号线上画一个小圆圈标注] TP3 (VBAT)

- 是什么: 使用

二、可维护性与调试友好性

-

处理未使用(Unused)或空引脚(No Connect):

- 是什么: 明确标注 IC 的未使用输入引脚是 悬空(

NC或DNU)、上拉(Pull-Up) /下拉(Pull-Down) 到确定电平、还是 接地(GND)/接电源(VCC)?输出引脚是否可以悬空? - 为什么重要: 未正确处理可能导致器件功能异常、增大静态功耗、甚至闩锁效应(ESD)。清晰的标注指导焊接和布局。

- 示意图:

[IC引脚旁标注] PIN7: NC (Do Not Connect)[IC引脚画上拉电阻并标注] PIN8: Input (Pull-Up to 3.3V via R10)

- 是什么: 明确标注 IC 的未使用输入引脚是 悬空(

-

标注调试/编程接口 (JTag, SWD, UART, Boot Select):

- 是什么: 给调试/烧录接口一个清晰的区域或页面,使用标准连接器符号(如

JTAG_10),标注每一根信号线的功能和顺序(参考标准如 ARM 20-pin or 10-pin)。 - 为什么重要: 软件开发和生产编程依赖此接口。清晰的定义避免接错线损毁调试器或目标板。

- 示意图:

[JTAG接口区域标注] CONN J2 (ARM 10-pin JTAG/SWD): 1=VTref, 2=SWDIO, 3=GND, 4=SWDCLK, 5=GND, ...

- 是什么: 给调试/烧录接口一个清晰的区域或页面,使用标准连接器符号(如

-

考虑可测性(Design for Testability - DFT):

- 是什么: 在关键环路/隔离点设计预留跳线(

Jumper,0Ω Resistor),用于断开连接(如电源输入、模拟前端隔离、总线断开)。在电源输入处预留保险丝位(Fuse Placeholder)。 - 为什么重要: 允许在故障时快速隔离模块,精确测量定位问题根源。

- 示意图:

[VIN线上标注] JP1 (Shorted by Default) 或 R100 (0Ω)

- 是什么: 在关键环路/隔离点设计预留跳线(

三、细节处理与专业表达

-

全局统一符号与规则:

- 是什么: 使用公司的标准化符号库。对所有

VCC/AVCC/DVCC、GND/AGND/DGND/PGND、RESET(高低有效)、ENABLE(高低有效) 等逻辑电平/电源域采用统一且清晰的标注风格。 - 为什么重要: 保证团队协作图纸的一致性,降低理解门槛,提升专业度。

- 示意图:

[所有电源符号统一为带棱形框+电压值,所有地符号统一为带阶梯线+域名]

- 是什么: 使用公司的标准化符号库。对所有

-

精确的位号管理:

- 是什么: 原理图设计初期就规划好位号(

U1,U2,R101-R120)。不同功能模块(如 FPGA/CPLD 配置电路、RF 模块)使用独立的位号分区(U1xx,R2xx)。预留增删空间。 - 为什么重要: 避免后续增删元件导致的位号大范围变动(如删掉

R1后所有电阻位号重排),维护图纸和 BOM 的稳定性。 - 示意图:

[原理图首页/说明中标注] Uxx: Main MCU & Peripherals; U5x: Ethernet PHY; U6x: External Memories; R8xx: FPGA Config Resistors

- 是什么: 原理图设计初期就规划好位号(

-

详细且结构化的注释与设计说明 (Beyond Basic Notes):

- 是什么:

- 功能框说明: 在模块/分页开头,用文本框描述该部分电路功能/设计目标/关键规格。

- 特殊器件说明: 非标准器件、定制器件、易错器件(如二极管、MOSFET 方向)加详细注释。

- 版本变更记录: 在图纸角落或首页添加修订历史(Rev History)。

- 关键设计计算: 如分压电阻值计算

(R1 / (R1 + R2)) * VREF = 0.5V。 - 警告与注意事项(

WARNING!,CAUTION!): 高压危险、ESD敏感点、首次上电感测顺序。

- 为什么重要: 承载设计意图和过程知识,是图纸的灵魂。方便后续维护、产品迭代和问题回溯。

- 示意图:

[模块上方文本框] *Power Supply Module*: Input 9-24VDC, Output +5V@1A, +3.3V@1A. Primary switch regulator, Use low ESR capacitors at Output!

- 是什么:

四、与PCB/制造的协同

-

定义关键元件的物理属性与布局要求:

- 是什么: 在高发热器件(MOSFET, 功率电感、LDO/DC-DC)旁标注“

Place for Heatsinking”或“Bottom Pad Must Connect to Ground Plane”。高速(时钟、差分线)或敏感模拟器件(ADC参考、运放)附近标注“Keep-out region”。高压器件间标注安全间隙(Creepage > 2mm)。 - 为什么重要: 指导 PCB Layout 和结构设计,避免因散热、EMI/EMC、安规问题导致板子返工。

- 示意图:

[功率MOS旁标注] Q1: Must Connect Source/Drain Pads to Large Copper Area (Heatsink) / Backside Thermal Pad Vias to GND Plane

- 是什么: 在高发热器件(MOSFET, 功率电感、LDO/DC-DC)旁标注“

-

明确关键器件的供应商/备选型号:

- 是什么: 对于易缺货或关键器件,在器件附近标注首选型号(

PREFER: ABC123) 和 2-3 个验证过的备选型号(ALT: DEF456, GHI789)。对于连接器,标注关键机械尺寸参数或厂家元件编号。 - 为什么重要: 增强 BOM 灵活性,减少由缺料导致的停产风险。连接器的准确标注保证结构匹配。

- 示意图:

[IC旁标注] U3: AT25SF041-SSHD-B (SOIC-8). ALT: MX25L4006EM1I-12G (SOP-8); W25Q40CLSNIG (SOIC-8)

- 是什么: 对于易缺货或关键器件,在器件附近标注首选型号(

-

特殊封装脚位处理说明:

- 是什么: 对带有 Thermal Pad(如 QFN, PowerPAD)、Floating Pin(有些引脚仅作散热用无电气连接)的器件,原理图上明确绘制出该 PAD 符号(常命名为

EP),并标注处理方式:EP: Must Connect to GND Plane via Multiple Vias或EP: Electrically Isolated (No Connect)。 - 为什么重要: 确保 PCB Layout 正确处理封装,避免虚焊或散热不良。

- 示意图:

[QFN下方画出并标注一个方形引脚:] EP (PAD): Thermal Pad, Connect to GND.

- 是什么: 对带有 Thermal Pad(如 QFN, PowerPAD)、Floating Pin(有些引脚仅作散热用无电气连接)的器件,原理图上明确绘制出该 PAD 符号(常命名为

1147

1147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?