这个模块集合大部分的功能,通过开关的复用实现显示学号,清零,正常示数,校时校分四个功能,并且确定了几个开关之间的优先级顺序,,防止出现逻辑上的问题,而且巧妙的利用3600秒小时加一的关系减小了if嵌套的复杂性,程序代码如下:

module jishi(clk_1Hz,second,minute,hour,hour_swh,min_swh,swh,baochi_swh);

input clk_1Hz;

input hour_swh,min_swh,baochi_swh;

input [1:0]swh;

output reg[5:0]second,minute,hour;

reg [11:0]hs; //3600秒小时加1

always@(posedge clk_1Hz)

begin

if((swh[1:0] == 'b00)&&(!baochi_swh)) //清零

begin

second <= 0;

minute <= 0;

hour <= 0;

end

else if(baochi_swh) //使能

begin

second <= second;

minute <= minute;

hour <= hour;

end

else if((swh[1:0] == 'b11)&&(!baochi_swh)) //正常计数

begin

if(second < 'd59)

begin

second <= second + 'd1;

hs <= hs + 'd1;

end

else

begin

second <= 'd0;

hs <= hs + 'd1;

if(minute < 'd59)

minute <= minute + 'd1;

else

minute <= 'd0;

if(hs < 'd3599 && hour < 'd23)

hour <= hour + 'd1;

else if((hs == 'd3599)&&(hour == 'd23))

begin

hour <= 'd0;

hs <= 'd0;

end

end

end

else if((swh[1:0] == 'b10)&&(!baochi_swh)) //显示学号

begin

hour <= 'd00;

minute <= 'd07;

second <= 'd36;

end

else if((swh[1:0] == 'b01)&&(!baochi_swh))

begin

if((hour_swh)&&(swh[1:0] == 'b01))

begin

if(hour == 'd23)

hour <= 'd0;

else

hour <= hour + 'd1;

end

if((min_swh)&&(swh[1:0] == 'b01))

begin

if(minute == 'd59)

minute <= 'd0;

else

minute <= minute + 'd1;

end

end

end

endmodule

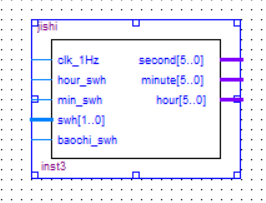

封装后如下图:

本文介绍了一个多功能计时模块的设计,该模块集成了显示学号、清零、正常计数和校时校分功能。通过巧妙地利用3600秒小时加一的关系简化了if嵌套的复杂性,确保了程序的高效性和逻辑清晰。模块还确定了开关之间的优先级顺序,避免了逻辑冲突。

本文介绍了一个多功能计时模块的设计,该模块集成了显示学号、清零、正常计数和校时校分功能。通过巧妙地利用3600秒小时加一的关系简化了if嵌套的复杂性,确保了程序的高效性和逻辑清晰。模块还确定了开关之间的优先级顺序,避免了逻辑冲突。

1116

1116

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?