把48Mhz分频成1Hz,1KHz,500Hz和2Hz:1KHz用于高频率报时,500Hz用于低频率报时,2Hz用于闹钟快速校时校分,1Hz用于正常计数。

module fenpin(clk,clk_1Hz,clk_1KHz,clk_500Hz,clk_2Hz);

input clk;

output reg clk_1Hz,clk_2Hz,clk_500Hz,clk_1KHz;

reg [26:0]counter;

reg [26:0]counter1;

always@(posedge clk) //48MHz->1KHz

begin

if(counter == 'd24000)

begin

clk_1KHz <= ~clk_1KHz;

counter <= 0;

end

else

begin

counter <= counter+1'd1;

end

end

always@(posedge clk_1KHz) //1KHz->500Hz

begin

clk_500Hz <= ~clk_500Hz;

end

always@(posedge clk_500Hz) //500Hz->2Hz

begin

if(counter1 == 'd125)

begin

clk_2Hz <= ~clk_2Hz;

counter1 <= 0;

end

else

begin

counter1 <= counter1 + 1'd1;

end

end

always@(posedge clk_2Hz) //2Hz->1Hz

begin

clk_1Hz <= ~clk_1Hz;

end

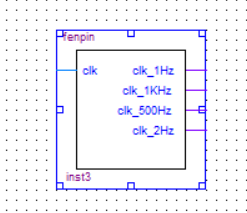

endmodule 封装后如下图:

本文介绍了一种将48MHz时钟信号分频为1Hz、1KHz、500Hz和2Hz的方法。通过使用Verilog硬件描述语言,实现了不同频率的时钟信号,适用于各种时钟需求,如高频率报时、低频率报时、快速校时和正常计数。

本文介绍了一种将48MHz时钟信号分频为1Hz、1KHz、500Hz和2Hz的方法。通过使用Verilog硬件描述语言,实现了不同频率的时钟信号,适用于各种时钟需求,如高频率报时、低频率报时、快速校时和正常计数。

611

611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?