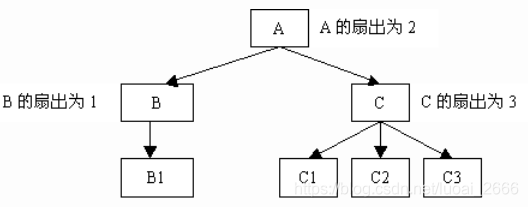

扇入系数是指门电路允许的输入端数目。扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力。

多扇出问题,会严重影响FPGA布线的稳定性,不利于时序收敛

当输出负载大于它的扇出能力的时候,就会有如下的效应:

1、输出低态时,输出电压VOL可能高于VOLmax。

2、输出高态时,输出电压VOH可能高于VOLmin。

3、输出的传播延迟可能大于规格说明的延迟值。

4、输出的上升和下降时间可能大于规格说明的延迟值。

5、器件工作温度可能升高,从而降低其可靠性,最终引起器件失效。

解决方法:

复制寄存器。

举个例子: CLK为系统时钟,M为1MHz方波信号,由于M信号驱动的模块较多,所以M的扇出较多,为了减少扇出,用系统时钟采样,将M信号驱动7个D触发器,然后将7个D触发器的输出端分给7个模块,这样每个复制点(DUP0~DUP6)平均扇出变为原来的1/7,M的信号扇出变为7,这样就减少了每个信号的扇出,优化了逻辑,也提高了设计的整体性能。简而言之,就是将一路信号用D触发器和CLK将其分成两路信号,或者是更多路的信号,再让这些信号来驱动下面的各个模块。

如何判断是系统的问题是由于多扇出而导致的呢。我是这样判断的,因为我的模块是一个一个写,一块一块的调试的,所以在分开调试的时候没有出任何问题,当所有的综合在一起的时候,就出现了有一个模块的信号总是不正常,单独调试该模块的时候又正常,然而这两个模块之间又没有什么交互信号,所以,就把问题定位在这个共用信号的驱动能力上了,最终曾加了D触发器,解决了这个问题。

另外经高手指点,还有一种方法是将这个频率信号放在CLK的管脚上,因为时钟管脚的驱动能力比一般的IO口要大一些,所以也就能够带动更多的逻辑门。

参考资料

https://www.cnblogs.com/woshitianma/archive/2013/01/22/2871561.html

https://blog.youkuaiyun.com/weixin_30907935/article/details/99366674

本文介绍了FPGA设计中遇到的多扇出问题,包括输出电压异常、延迟增加和可靠性下降等影响。通过使用D触发器复制信号和利用时钟管脚的强驱动能力来减少扇出,可以有效优化逻辑并提高设计性能。当模块集成后出现信号不稳定时,考虑多扇出可能是问题源头,并提供了解决方案。

本文介绍了FPGA设计中遇到的多扇出问题,包括输出电压异常、延迟增加和可靠性下降等影响。通过使用D触发器复制信号和利用时钟管脚的强驱动能力来减少扇出,可以有效优化逻辑并提高设计性能。当模块集成后出现信号不稳定时,考虑多扇出可能是问题源头,并提供了解决方案。

5224

5224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?