目录

一、状态寄存器传送指令

读CPSR:

@读CPRS

MRS R1 , CPSR @ R1 =CPRS 写CPSR:

@写CPRS

MRS CPSR,#0x10将CPSR改成usr模式,ARM状态、开启IRQ、FIQ

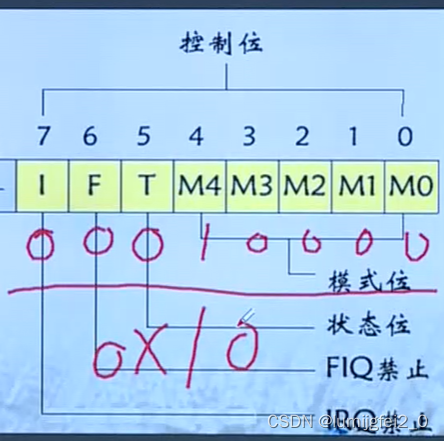

[7:0] 分别为00010000转换成16进制为0x10

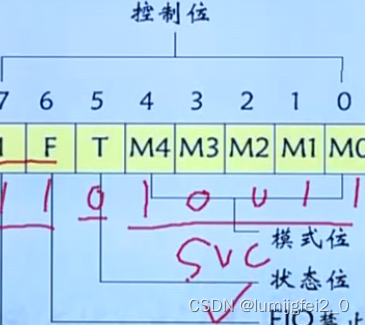

CPSR 更改为USR模式后,无法将CPSR写成0xD3 SVC模式(0x000000D3转换成二进制的值为11010011),因为USR非特权模式,权限低不能随意修改核心的东西

MRS CPSR,#0x10

MRS CPSR,#0xD3

![]()

本文详细解释了ARM处理器中的状态寄存器传送指令(CPSR操作),软中断(SWI)处理,协处理器指令的使用,以及伪指令的作用。涉及了从CPSR模式转换、软中断异常处理到协处理器数据运算和存储的操作过程。

本文详细解释了ARM处理器中的状态寄存器传送指令(CPSR操作),软中断(SWI)处理,协处理器指令的使用,以及伪指令的作用。涉及了从CPSR模式转换、软中断异常处理到协处理器数据运算和存储的操作过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8159

8159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?