协议来自PCI Express Base Specification Revision 3.0

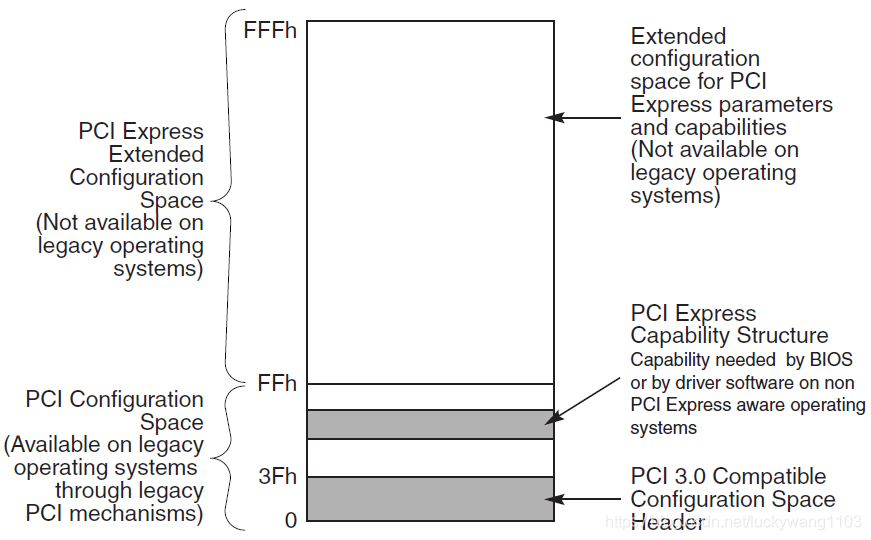

7.1 PCI Express Configuration Mechanisms

PCI Compatible Configuration Space Header,范围是[0, 0x3F],查看7.5节

PCI Express Capability Structure,范围是[0x40, 0xFF],(注:图中灰色的部分PCI Express Capability Structure只是众多PCI Capability Structure中的一个),查看7.7节

PCI Express Extended Capability Structure,范围是[0x100, 0xFFFF]

PCI Express Capability Structure

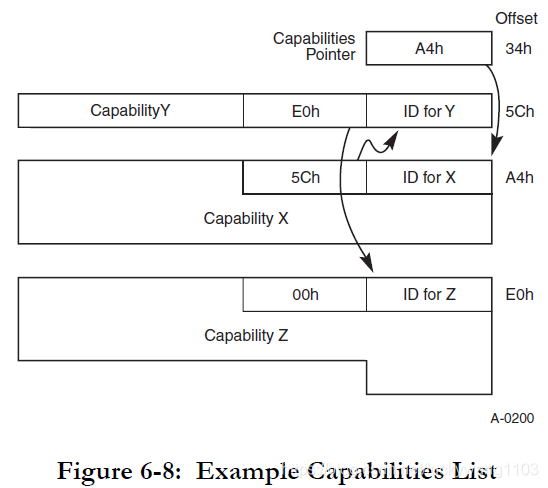

PCI Express Capability List位于[0x40, 0xFF]区间

他可以被看作是一个由Capability Item组成的链表,链表的头指针保存在PCI compatible configuration register的0x34位置的Capability Pointer中。每个Capability Item的大小长度范围是不同的,但是都遵循一个标准化的Capibility Header,如下:

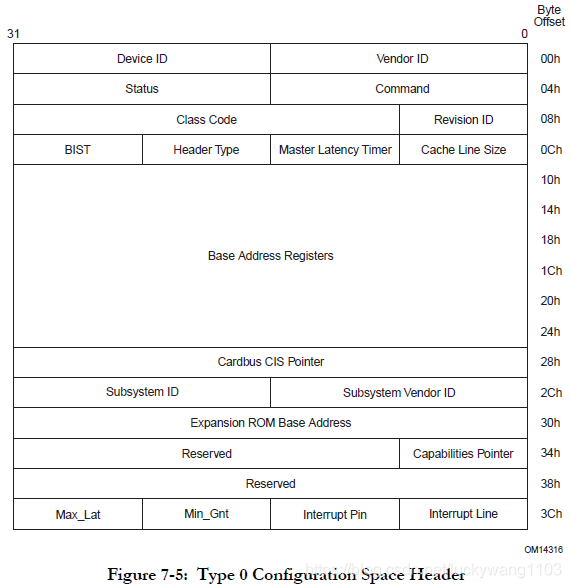

7.5 PCI compatible configuration register

这是type 0型的头部结构,一般用于PCI设备,还有个type 1型的头部结构,用于PCI桥。

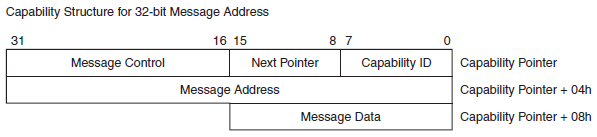

7.7 MSI and MSI-X Capability structures

MSI(Message Signaled Interrupts)是一种中断方式,从PCI2.2开始只是,在PCI3.0中得到扩展,支持更多中断以及拥有独立配置各个中断能力的MSI-X。

MSI的原理:PCI有一个特殊的寄存器,往这个寄存器里面写数据,就会触发CPU中断

这个寄存器就来自PCI提供的MSI/MSI-X Capability结构里的Message Address

INTx,MSI,MSI-X区别:

INTx:

在PCI总线里面INTx中断是由四条可选的中断线决定的,这种中断方式是共享的,所有的PCI设备把中断信号在一条中断线上相与,再上报给CPU,CPU收到中断后再查询具体是哪个设备产生了中断。

MSI:

在PCIe总线里已经没有实体的INTx物理总线了,PCIe使用专门的Message事物包来实现INTx中断,这是为了兼容以前的PCI软件。MSI中断是往CPU中断寄存器中进行memory写操作来产生中断。

MSI-X:

MSI支持的中断数据比较有限,而且如果有一组中断的话,必须要求中断号连续,而MSI可以支持很多的中断,并且一组中断中中断号也不需要连续。

参考文章

- PCI Express Base Specification Revision 3.0

- PCI Express体系结构导读

203

203

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?