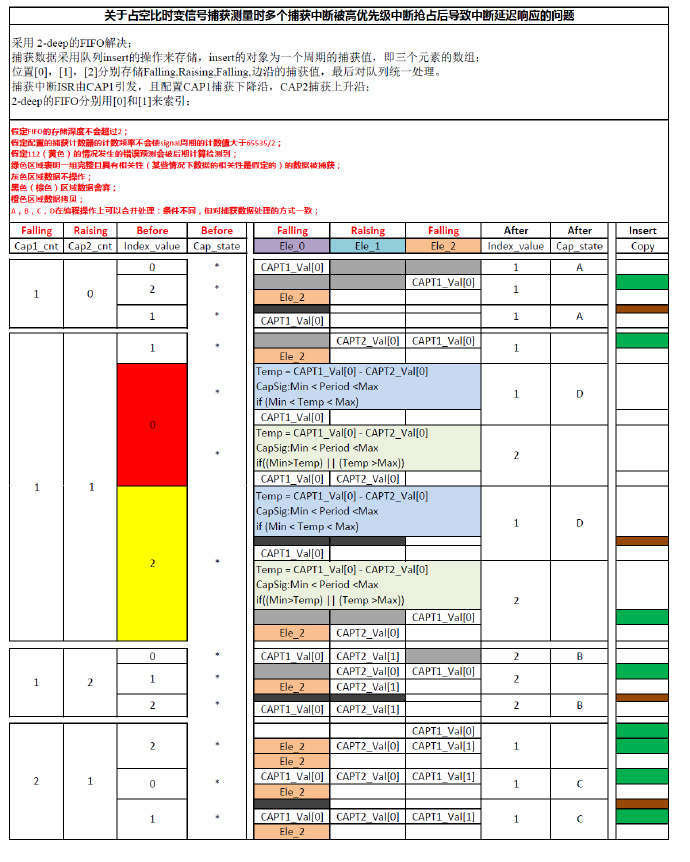

采用 2-deep的FIFO解决;

捕获数据采用队列insert的操作来存储,insert的对象为一个周期的捕获值,即三个元素的数组;

位置[0],[1],[2]分别存储Falling,Raising,Falling,边沿的捕获值,最后对队列统一处理。

捕获中断ISR由CAP1引发,且配置CAP1捕获下降沿,CAP2捕获上升沿;

2-deep的FIFO分别用[0]和[1]来索引;

-----------------------------------------------------------------

假定FIFO的存储深度不会超过2;

假定配置的捕获计数器的计数频率不会使signal周期的计数值大于65535/2;

假定112(黄色)的情况发生的错误预测会被后期计算检测到;

绿色区域表明一组完整且具有相关性(某些情况下数据的相关性是假定的)的数据被捕获;

灰色区域数据不操作;

黑色(棕色)区域数据舍弃;

橙色区域数据拷贝;

A,B,C,D在编程操作上可以合并处理:条件不同,但对捕获数据处理的方式一致;

------------------------------------------------------------------------------

------R---F-----R------F------R-----F---------------PWM signal

------a----b----c--cd--d------e-----f----------------index

考虑突发112的情况:已经有FR,即01;期待F,即2位;低位编码,F触发ISR:

>>>>>>>>正常情况下,下一个11应该是RF;R在F前面;此时舍弃01,利用新的F重建0位,期待1位;

>>>>>>>>某种情况下:R(a位置)被干扰丢失(RF序列被打乱),F(b位置)随即发生;这样就有了F,ISR即将触发,但是恰巧被延迟到下一个“序列(cd序列)”的R(c位置)之后(下一个RF序列的F(d位置)尚未发生之前),即cd位置,此时11的情况产生了,而此时11的情况应该是FR,按照cap情况而言,R在F的后面,此时满足一个FRF,且可以新建一个FR,期待2位,即F;

.........程序必须对112情况的RF序列的情况进行判别,并处理;当然后续PWM协议检查也是可以检查出来这种假设是否正确,此处的目的在于采集序列被破坏之后如何顺利实现自恢复~~

本文详细阐述了使用FIFO结构解决信号捕获问题的方法,包括采用队列存储周期捕获值,配置捕获中断ISR并处理不同序列情况,如突发112情况下的自恢复机制。

本文详细阐述了使用FIFO结构解决信号捕获问题的方法,包括采用队列存储周期捕获值,配置捕获中断ISR并处理不同序列情况,如突发112情况下的自恢复机制。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?