Verilog PLI(Programming Language Interface )是一种Verilog代码调用C/C++函数的机制。它能让Verilog像调用一些系统调用(如$display/$stop/$random)一样调用用户编写的C/C++函数。PLI可以完成如下功能:

- 功耗分析

- 代码覆盖率工具

- 修改Verilog仿真数据结构(如修改为更精确的延时,即sdf反标)

- 自定义输出显示

- 联合仿真

- 设计的调试功能

- 仿真分析

- 加速仿真的C模型接口

- Testbench建模

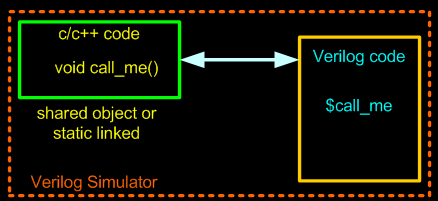

为了完成上述功能,C代码需要能够访问Verilog的内部数据结构,因此Verilog PLI需要提供一些访问程序集(acc routines),此外Verilog PLI还提供了另外一组程序集:任务功能程序集(tf routines)。目前PLI有两个版本:PLI1.0和PLI2.0,PLI 2.0又叫VPI,是随着Verilog 2001一起发布的。

1.工作原理

1)C/C++编写函数

2)编译并产生共享库(.DLL in Windows .so in UNIX)。一些仿真器如VCS允许静态链接。

3)将C/C++函数细节在编译veriog代码是传递给编译器(称为链接linking)

4)一旦链接完成,就可以像运行其他的verilog仿真一样了。

当Verilog仿真器遇到用户定义的系统函数时,便将控制权交给PLI 程序(C/C++函数)

2.示例-Hello World

下面给出一个简单的示例,例子不涉及任何PLI标准函数(ACC,TF等),因此,只要使用对应仿真器连接C/C++函数即可。

hello.c:

#include <stdio.h> void hello () { printf ("\nHello World!\n"); }

hello_pli.v

module hello_pli (); initial begin $hello; #10 $finish; end endmodule

使用如下VCS命令编译并运行:

vcs -R -P hello.tab hello_pli.v hello.c

hello.tab文件内容如下:

$hello call=hello

3.示例-PLI应用程序

下面一个示例将简单的调用PLI系统函数实现C/C++代码对Verilog代码的数据结构的访问,并将其应用在Testbench中实现对DUT的监视。

DUT设计为一个简单的16进制计数器,counter.v代码如下:

`timescale 1ns/10ps module counter ( input clk, input reset, input enable, output reg [3:0] count ); always @(posedge clk or posedge reset) begin if(reset) begin count <= 4'b0; end else if(enable) begin count <= count+

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

107

107

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?