sequence机制时UVM的核心机制,主要作用的是发送transaction以及对transaction的控制,下面将会重点介绍item transaction是如何从sequence传入到driver的。

在这里,我们暂时不会介绍start方法的使用,主要还是item如何从sequence传入到driver的。

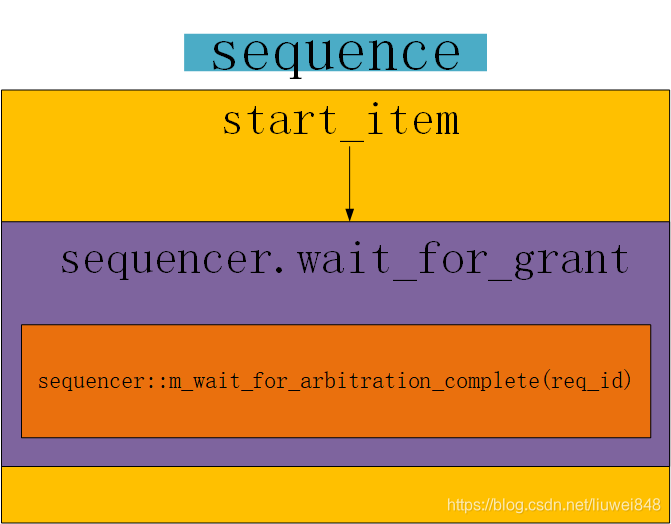

首先在sequence中负责发送item的方法是start_item和finish_item

在driver中负责接收item的方法是seq_item_port::get_next_item()

seq_item_port::item_done()两个方法。下面看一下是如何发生同步的

上图是sequence在调用start_item方法时的流程,在sequencer中有一个重要的变量专门用来存放sequence发送的请求,这个变量是

uvm_sequence_request arb_sequence_q[ $ ],sequence每发送一次请求,会生成一个unique req_id,arb_sequence_q中存放每个请求,以每个请求的unique req_id来标记不同的请求。接下来需要等待sequencer来仲裁,那么这个仲裁是如何发生的呢,其实是在调用seq_item_port::get_next_item()中实现的,我们这里讨论的前提是sequence的请求没有设置被的仲裁算法,以及没有lock,grab操作,同时只有一个sequence挂载到sequencr上。这个时候由于arb_sequence_q[ $ ]有一个请求,那么经过仲裁以后,这个请求得到许可,然后将这个请求放入到sequencer中的变量

bit arb_complete[int]中,相当于是arb_complete[req_id]=1。这个时候仲裁完成,strat_item task结束阻塞。

总结一下就是

(1)arb_sequence_q[$]中存放每一次seque

本文详细介绍了UVM sequence的核心机制,特别是item如何从sequence传递到driver的过程。通过start_item、finish_item、seq_item_port的get_next_item()和item_done()等方法,阐述了transaction在sequence和driver间的同步与仲裁流程。

本文详细介绍了UVM sequence的核心机制,特别是item如何从sequence传递到driver的过程。通过start_item、finish_item、seq_item_port的get_next_item()和item_done()等方法,阐述了transaction在sequence和driver间的同步与仲裁流程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

729

729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?