使用testbench 与 modelsim altera 联合仿真。解决vsim-19报错的一种慢方法。

1. test bench的modelsim 链接文件产生。

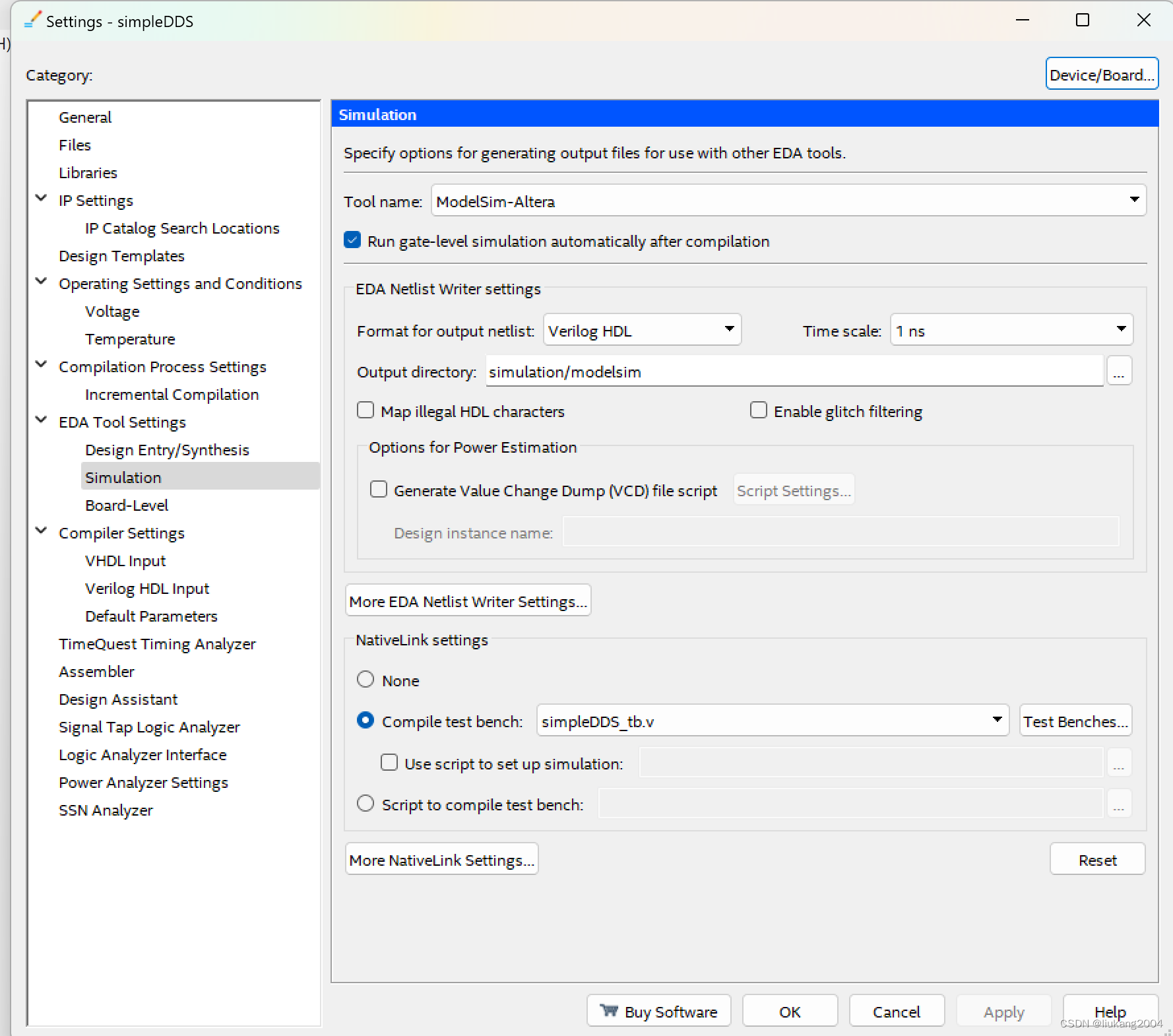

assignment setting simulate

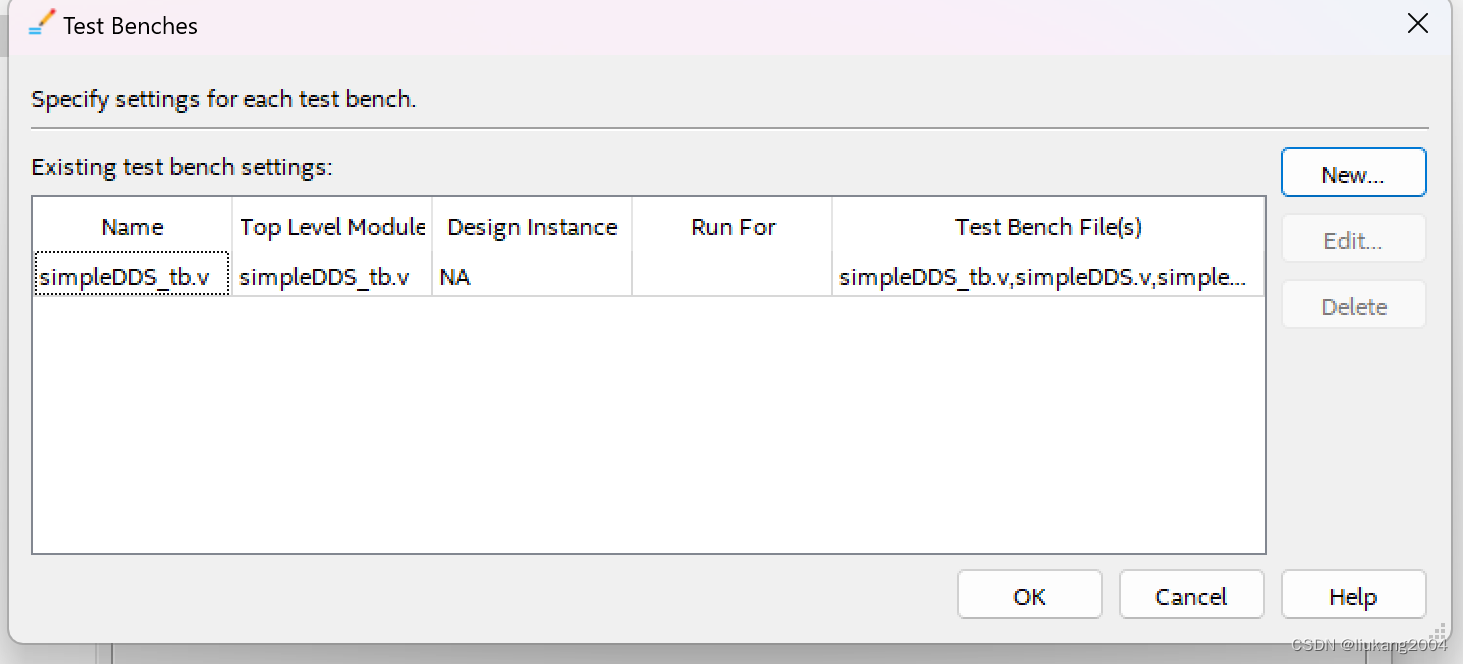

Test bench

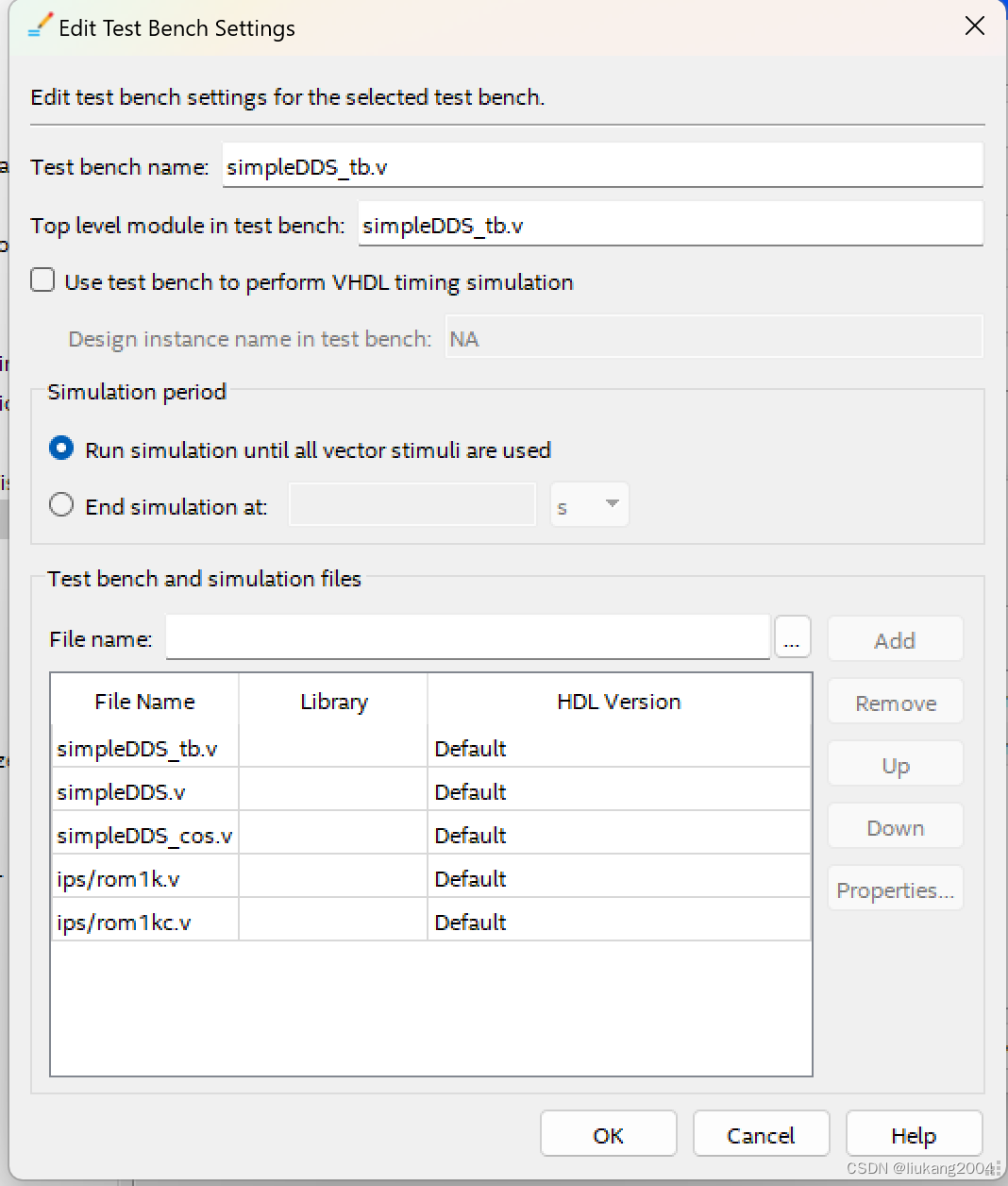

New or edit

添加测试文件,都要添加,不仅仅添加test bench,但是要以test bench 设为顶层设计。

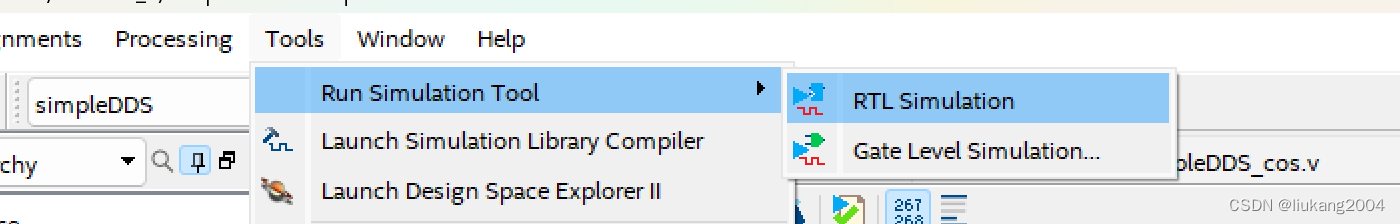

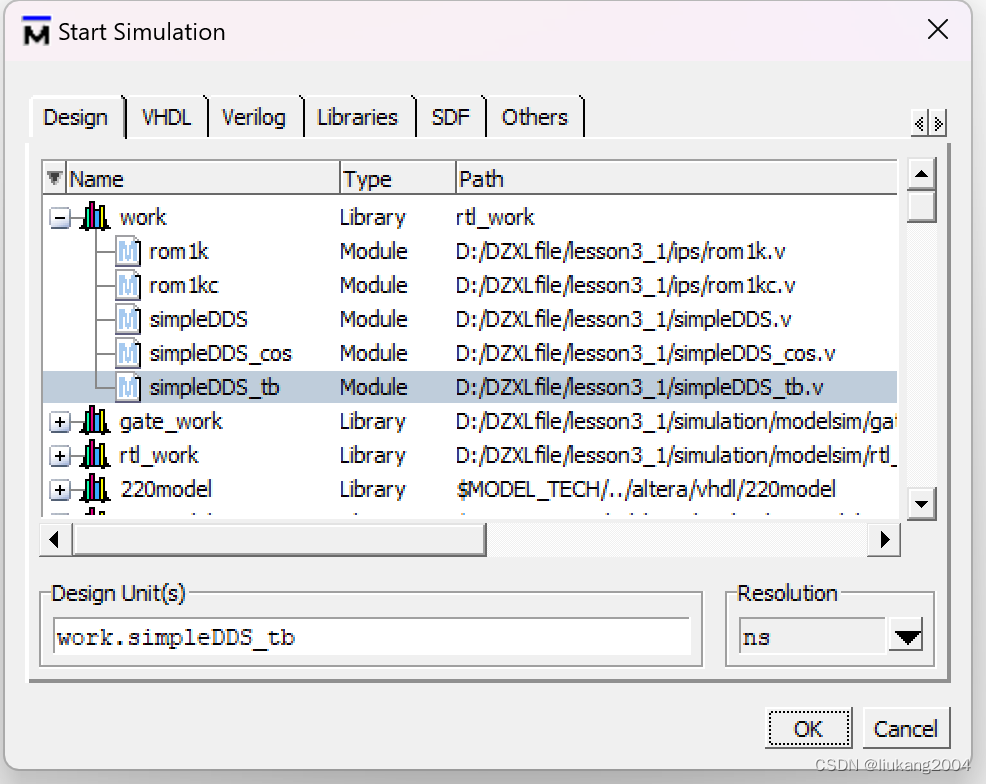

2. test bench仿真

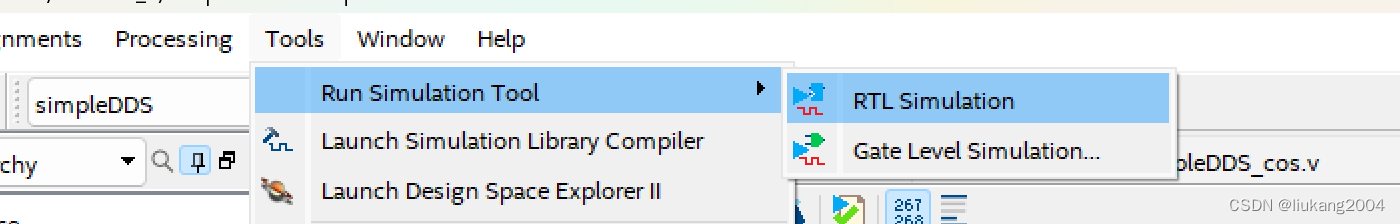

点击rtl simulatation

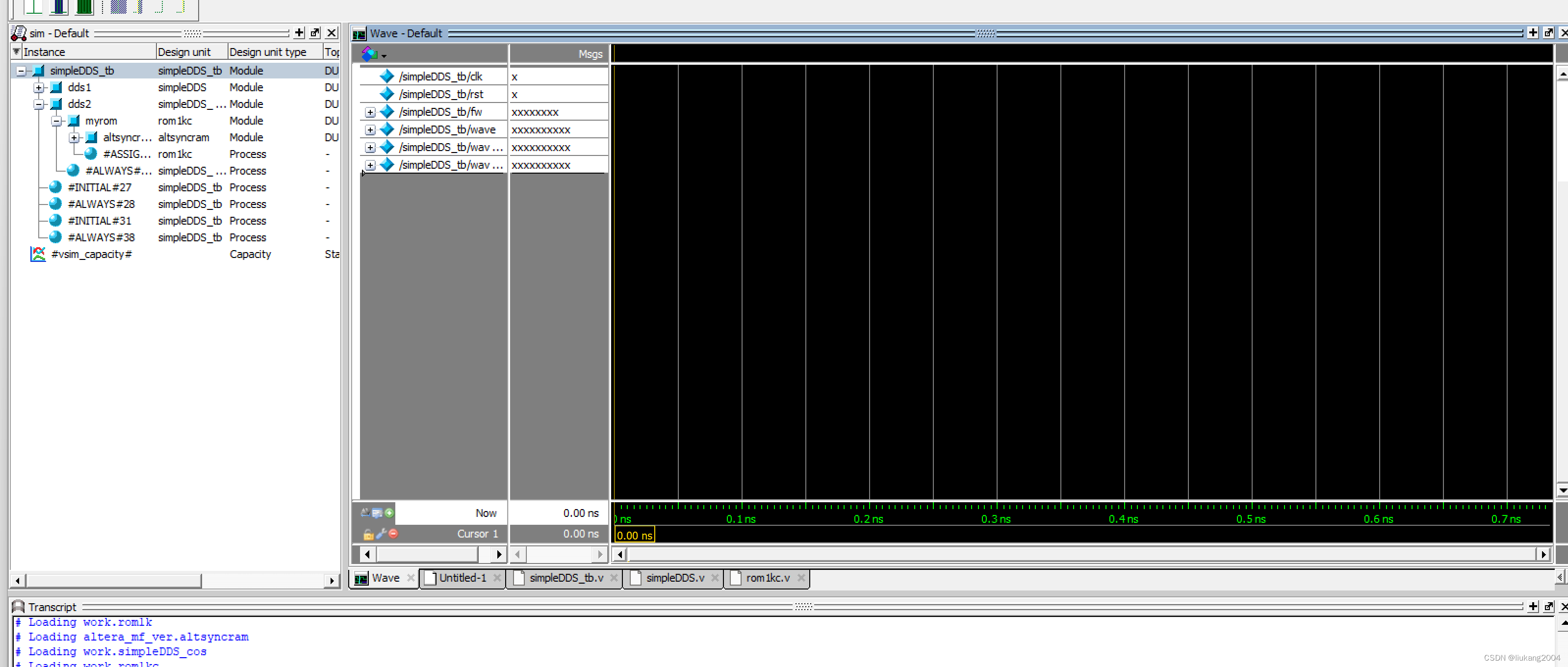

理论上因该产生以下页面

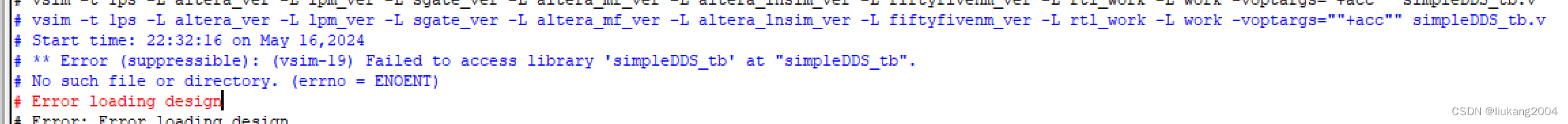

但是实际由于modelsim-altera配置错误,或者是上面的bench的链接文件产生了错误,会报错以下部分。

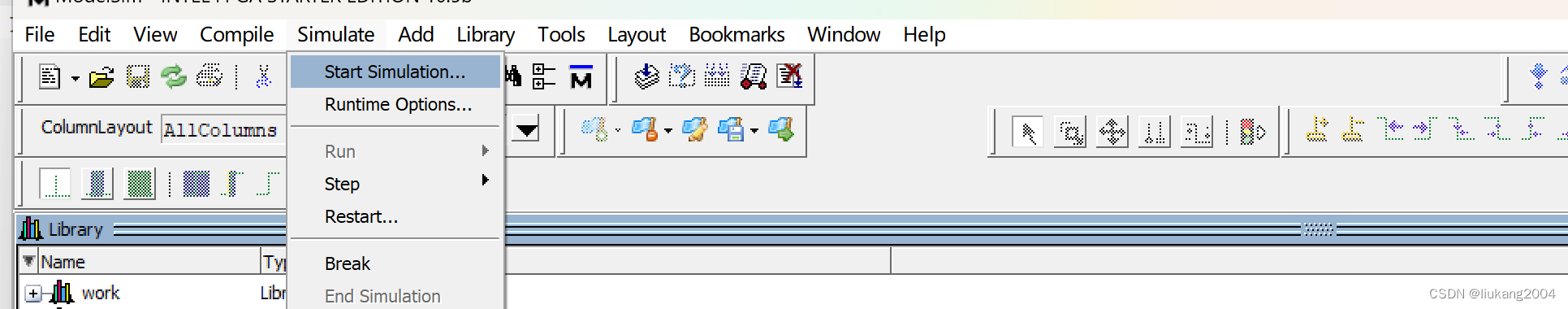

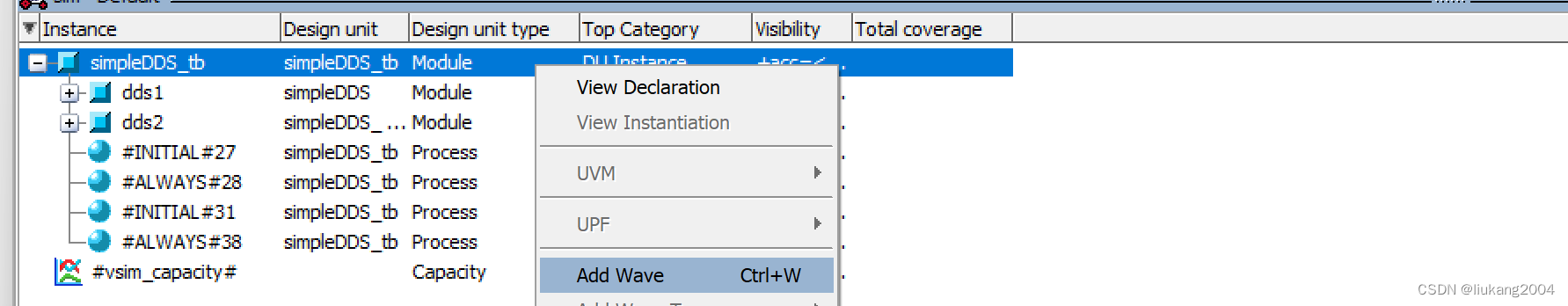

#### 3. modelsim altera 直接仿真

应对上述的报错,各类博客有一些解释,但是对于我的实际情况并不适用。所以我选择手动打开这个文件。然后进行仿真。

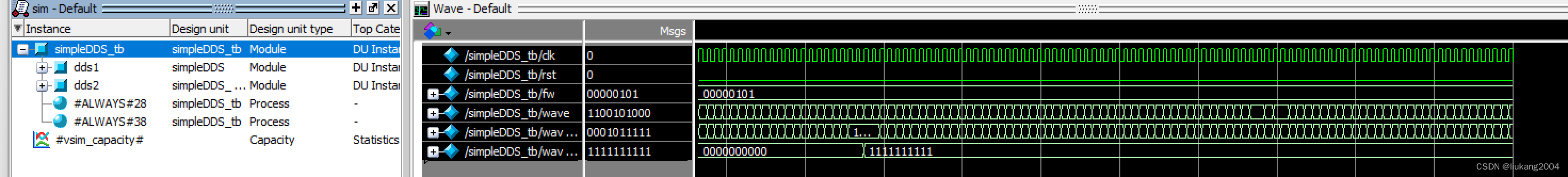

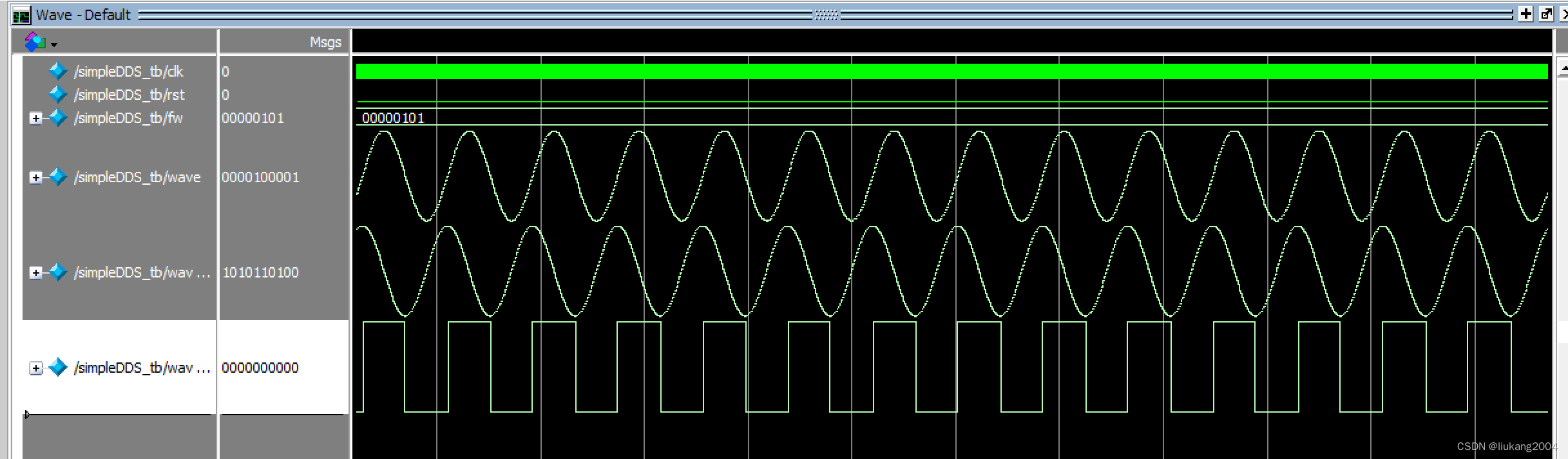

时间设置10ms,开始仿真。

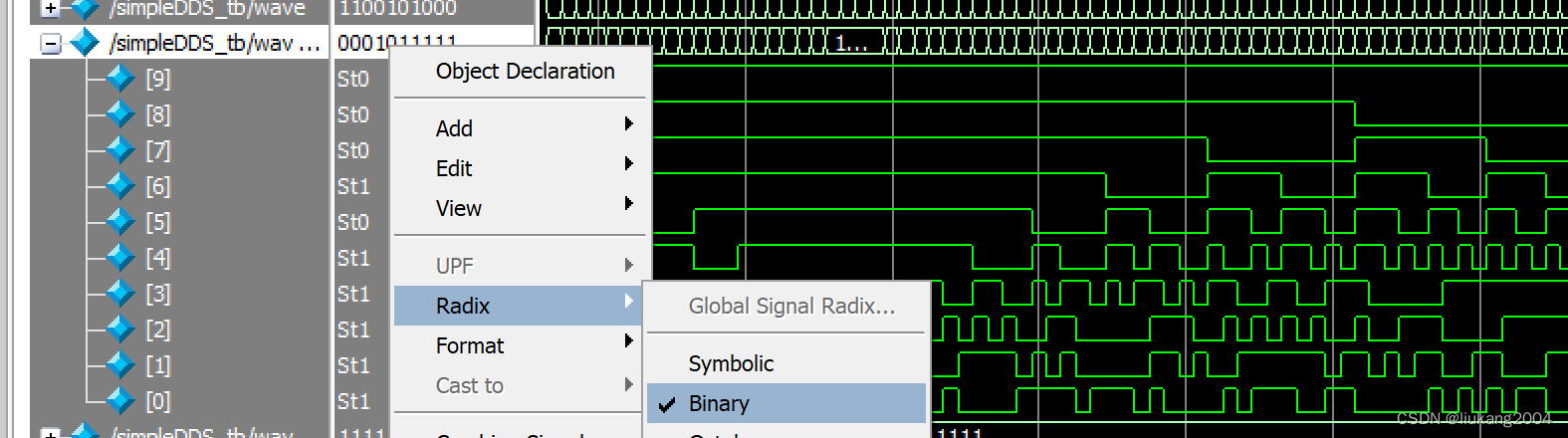

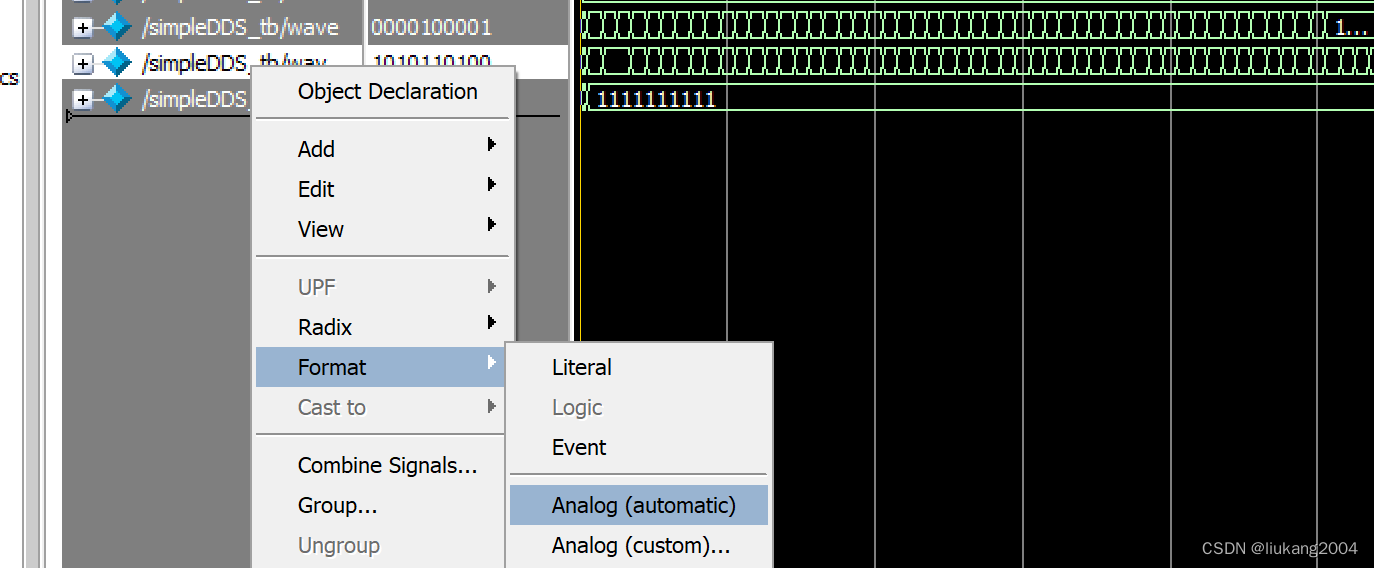

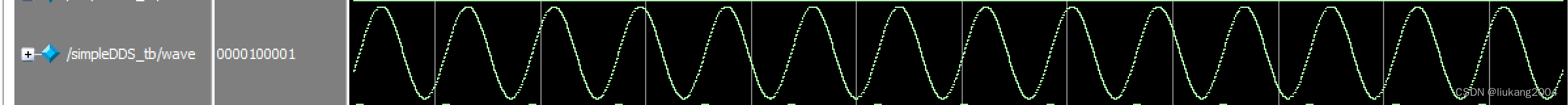

将这个数字输出可视化,进行模拟输出。

4. dds普通产生仿真结果

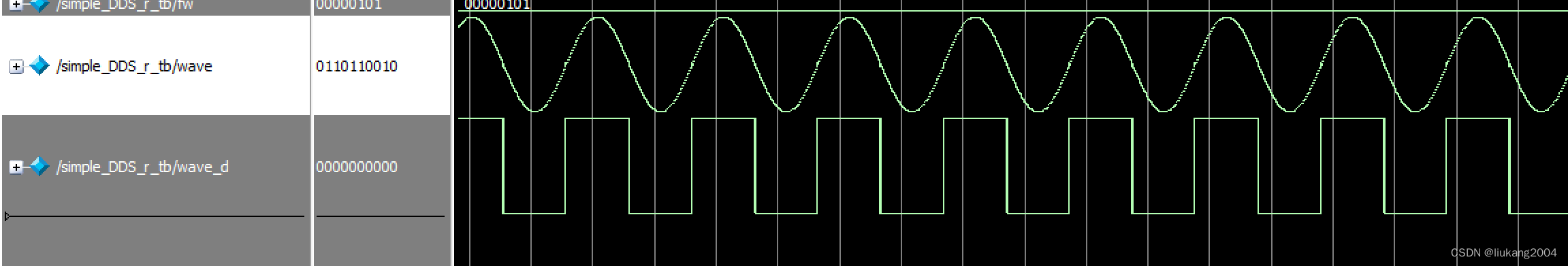

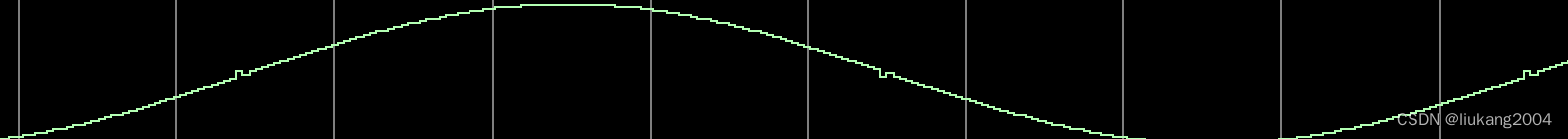

5. 1/4 dds仿真结果

明显小凸起,是程序算法带来的必然结果。具体请详细分析代码

对于vsim-19报错部分为本人理解,其他如有侵权请多多谅解。

5438

5438

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?