在Vivado TCL命令窗口中可以通过调用write_edif命令将用户自定义模块封装成.edf网表文件(类似ISE里的.ngc文件),但是当自定义模块中包含ngc时,编译时会报错,提示有未定义的黑盒。

那么如何将包含XIlinx IP或ngc的用户模块封装成网表文件呢,下面将给出详细步骤

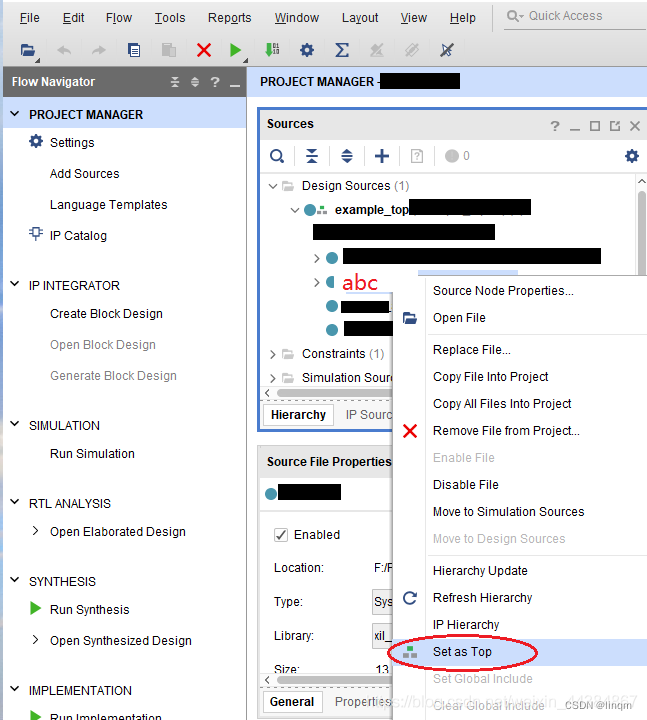

1. 将待封装模块设置为top层

如下图所示,待封装模块为abc,则选中abc后右键,选择“Set as Top”,

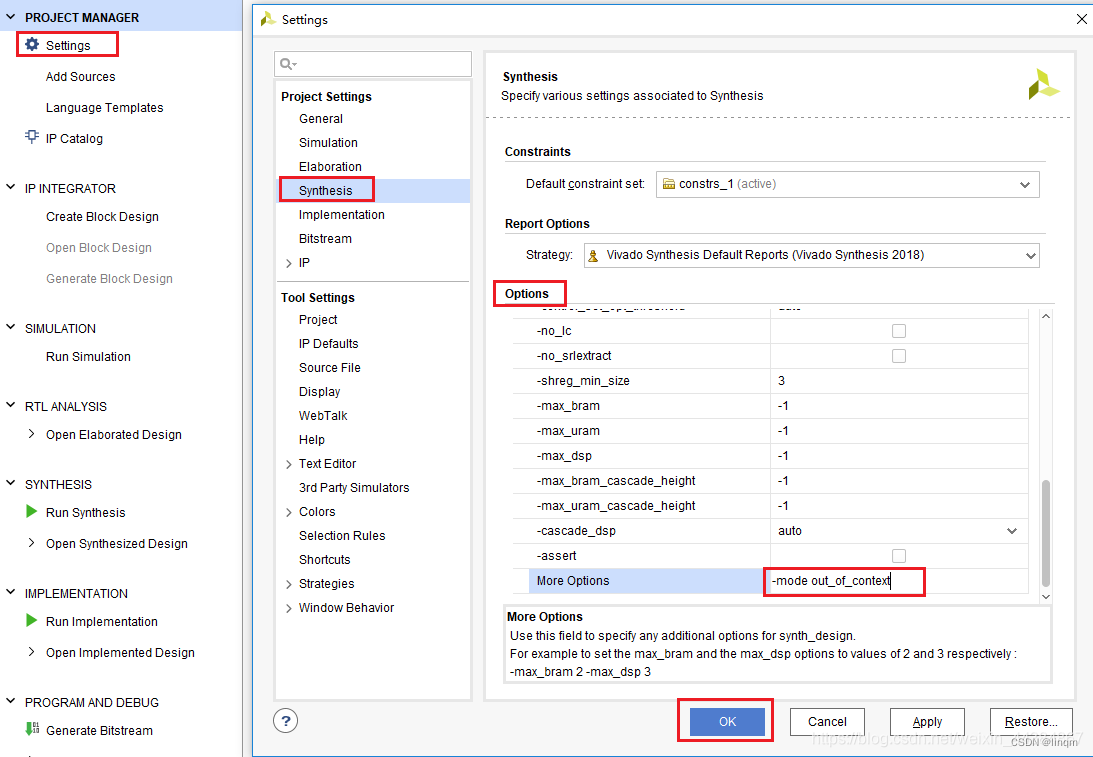

2. I/O Buffers设置

设置Settings–>综合 synthesis–>选项options下拉至最后一项:More Options,将其值设置为:

-mode out_of_context

-mode out_of_context表示在该级不插入任何I/O BUFFERs,该选项类似ISE里在相应设置处不勾选I/O BUFFERs。另外还可以在选项options中找到“-flatten_hierarchy”,将层级结构设置为“full”,层级结构则可设置“-ierarchy”选项为“full”:“全”该选项指示工具把层级全面变平,只剩下顶层,保护IP的层级结构不被其他用户清楚查看。

3. 综合

运行综合synthesis,完成综合后,打开综合设计open synthesized design

4. 生成仅包含IO端口信息的empty module

打开综合设计open synthesized design后,在TCL命令窗口执行如下命令:

2017.4之前版本:

write_verilog -mode port F:/FPGA/abc_stub.v

2018.1之后版本:

write_verilog -mode synth_stub F:/FPGA/abc_stub.v

其中F:/FPGA/替换为要存放的路径,如未指明路径,则将存放到工程文件所在路径下。

5. 生成edf文件

划重点了,分两条:

1、若不含Xilinx IP则可通过如下命令生成edf文件:

write_edif F:/FPGA/abc.edf

2、若含Xilinx IP则需通过如下命令生成edf文件:

write_edif -security_mode all F:/FPGA/abc.edf

6. 新工程中网表文件调用

将上述生成的abc_stub.v和abc.edf添加到新工程中即可。

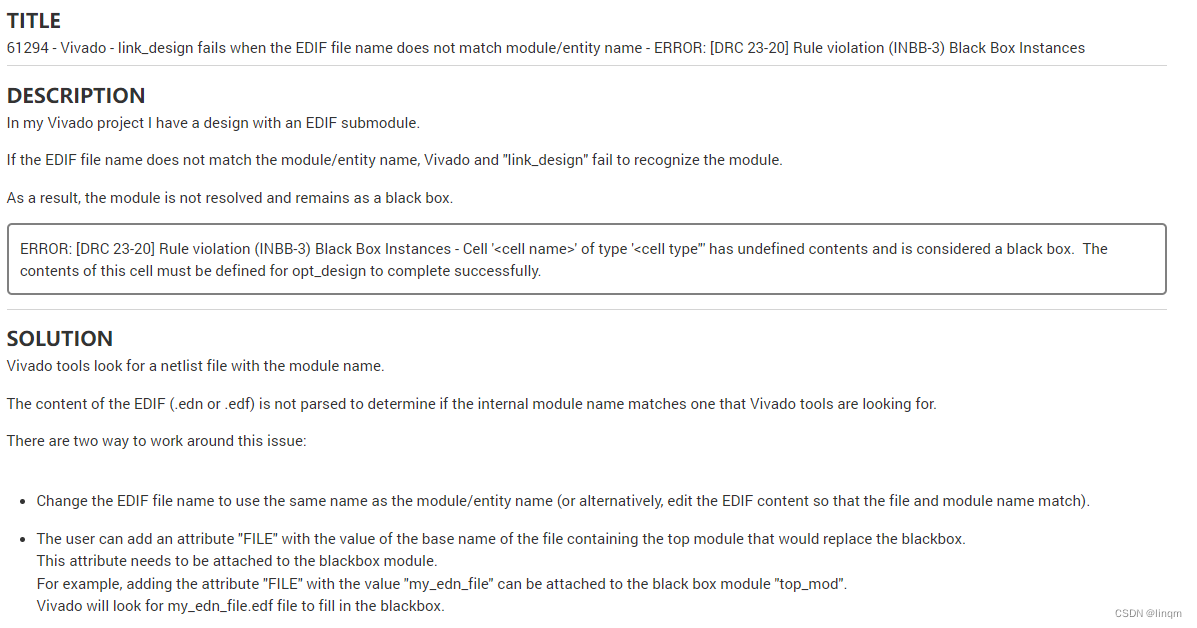

再划重点了:若出现如下错误时“Cell ‘’ of type ‘<cell type"’ has undefined contents and is considered a black box.The contents of this cell must be defined for opt_design to complete successfully.”

以下是解决方案,亲测通过改文件名可以解决。

7. 带Xilinx IP的另外一种网表封装方式(不推荐)

上述步骤3后,在tcl命令窗口中执行如下命令:

write_verilog -force abc_stub.v

该命令会将待封装模块中所有源码、IP都写入一个文件中,然后在新工程中仅需添加该文件即可。

1833

1833

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?