编者按AMD Kria SOM及KV260视觉入门套件介绍 - 电子发烧友在线研讨会

软件和硬件,既相互依存又需要某种程度上的相互独立。通过软件和硬件之间的接口把两者连接在一起。软硬件接口,有很多含义:比如指令集是CPU软件和硬件之间的接口;比如一些硬件模块(包括IO接口模块、GPU、各种加速引擎等)暴露出来的可读写寄存器,则为控制接口;再比如,CPU和GPU或其他硬件模块之间通过DMA进行数据交互的(软硬件间的)数据传输接口。 软硬件接口,是个非常庞大的命题。本文是《软硬件融合》图书内容的节选,聚焦在软件和硬件之间的数据交互接口。

软件和硬件之间数据交互接口

我们在计算机的基础课程里一般都学过IO交互的四种模式:寄存器模式、中断模式、DMA模式和通道模式。随着计算机技术的发展,除了IO设备,还有很多独立的硬件组件通过各种类型总线跟CPU连接在一起。接口已经不仅仅是用于IO数据传输场景,也用于软件(运行于CPU的程序)和其他硬件之间的数据交互场景。 注:本文用“软硬件接口”特指软件和硬件之间数据交互的接口。

1 软硬件接口定义

传统的非硬件缓存一致性总线,是需要软件驱动显式的控制设备来进行数据交互的。通过梳理软硬件接口的演进,逐步给出软硬件接口的定义。 a. 软硬件接口演进

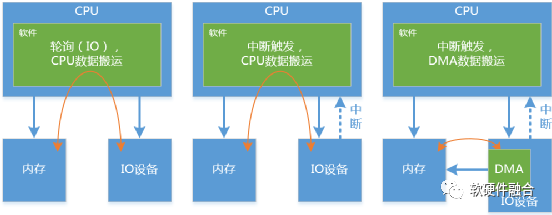

(a) CPU轮询 (b) CPU中断 (c) DMA方式

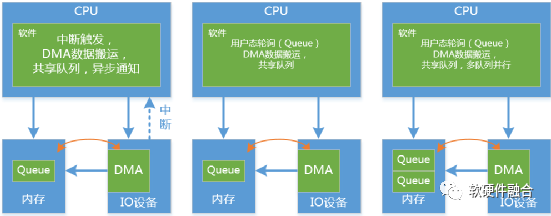

(d) 共享队列

(e) 用户态轮询

(f) 多队列 图1 软硬件接口的演进 软硬件接口是在IO接口基础上的扩展,如图1,我们结合IO交互的四种模式,重新梳理一下软硬件接口的演进:

第一阶段,使用软件轮询硬件状态。如图1(a),最开始是通过软件轮询,这时候软件和硬件的交互非常简单。发送的时候,软件会定期的去查询硬件的状态,当发送缓冲为空的时候,就把数据写入到硬件的缓存寄存器;接收的时候,软件会定期的查询硬件的状态,当接收缓冲区有数据的时候,就把数据读取到软件。

第二阶段,使用中断模式。如图1(b),随着CPU的性能快速提升,统计发现,轮询的失败次数很高,大量的CPU时间被浪费在硬件状态查询而不是数据传输,因此引入中断模式。只有当发送缓冲存在空闲区域可以让软件存放一定量待发送数据的时候,或者接收缓冲已经有一定量数据待软件接收的时候,硬件会发起中断,CPU收到中断后进入中断服务程序,在中断服务程序里处理数据的发送和接收。

第三阶段,引入DMA。如图1(c),前面的两种情况下,都需要CPU来完成数据的传输,依然会有大量的CPU消耗。因此引入了专用的数据搬运模块DMA来完成CPU和硬件之间的数据传输,某种程度上,DMA可以看做是用于代替CPU进行数据搬运的加速器。发送的时候,当数据在CPU内存准备好,CPU告诉DMA源地址和数据的大小,DMA收到这些信息后主动把数据从CPU内存搬到硬件内部。同样的,接收的时候,CPU开辟好一片内存空间并告知DMA目标地址和空间的长度,DMA负责把硬件内部的数据搬运到CPU内存。

第四阶段,专门的共享队列。如图1(d),引入了DMA之后,如果只有一片空间用于软件和硬件之间的数据交换,则软件和硬件之间的数据交换则是同步的。例如在接收的时候,当DMA把数据搬运到CPU内存之后,CPU需要马上进行处理并释放内存,CPU处理的时候DMA则只能停止工作。后来引入了乒乓缓冲的机制,当一个内存缓冲区用于DMA传输数据的时候,另一个缓冲区的数据由CPU进行处理,实现DMA传输和CPU处理的并行。更进一步的,演变成更多缓冲区组成的循环缓冲队列。这样,CPU的数据处理和DMA的数据传输则完全异步的完成,并且CPU对数据的处理以及DMA对数据的搬运都可以批量操作完成后,再同步状态信息给对方。

第五阶段&#x

本文介绍了软硬件数据交互接口的演进历程,从最初的CPU轮询、中断模式、DMA方式,到共享队列、用户态轮询驱动以及多队列支持。通过这些接口,软件和硬件之间的数据交互变得更加高效和异步,例如在存储和网络处理中,DPDK和SPDK等用户态轮询驱动技术提升了性能和降低了延迟。软硬件接口的演进对于提升系统整体性能和实现软件硬件解耦具有重要意义。

本文介绍了软硬件数据交互接口的演进历程,从最初的CPU轮询、中断模式、DMA方式,到共享队列、用户态轮询驱动以及多队列支持。通过这些接口,软件和硬件之间的数据交互变得更加高效和异步,例如在存储和网络处理中,DPDK和SPDK等用户态轮询驱动技术提升了性能和降低了延迟。软硬件接口的演进对于提升系统整体性能和实现软件硬件解耦具有重要意义。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5667

5667

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?